文章目录

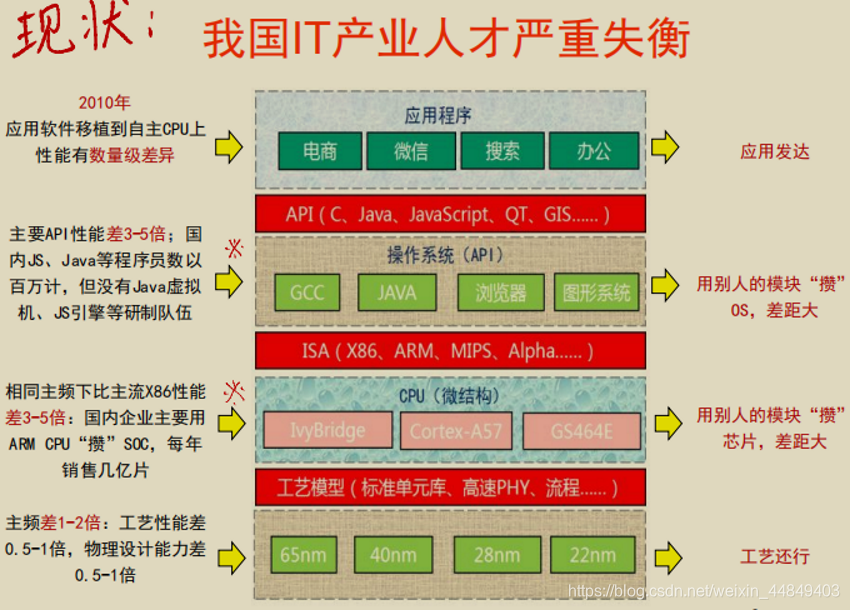

现状

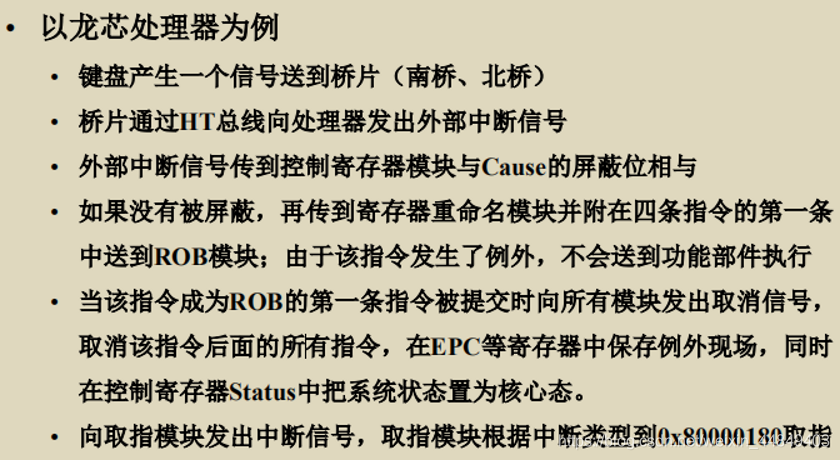

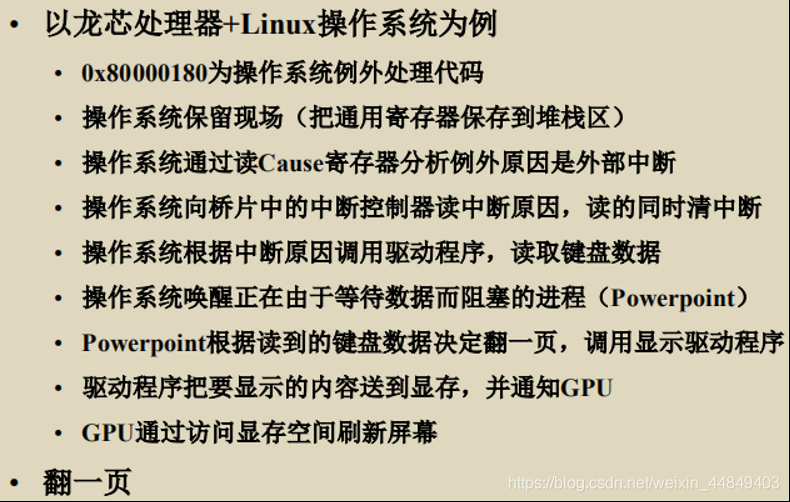

应用举例:PPT翻页过程

其中,如果觉得ppt翻页卡顿:

看系统中有没有其他任务在运行,因为任务会占用CPU、内存带宽、IO带宽等资源;

影响因素:

①GPU:下一页PPT可能图比较多,GPU忙不过来;

②内存带宽:显示内容数据量大,把数据从PowerPoint的应用程序空间传给GPU使用的显存,内存带宽不足;(独显时:数据采用类似DMA的方式,从内存传输到显存)

计算机体系结构

1. 定义:

计算机体系结构(Computer Architecture)是描述计算机各组成部分及其相互关系的一组规则和方法,是程序员所看到的计算机属性。

2. 主要研究内容:

计算机体系结构主要研究内容包括指令系统结构(Instruction Set Architecture,简称ISA)和计算机组织结构(Computer Organization)。

3.现代体系结构基础:

二进制、冯诺依曼结构的存储程序和指令驱动执行原理

4.表现方式:

(1)指令系统手册和结构框图:结构框图中的方块表示计算机的功能模块,线条和箭头表示指令和数据在功能模块中的流动,结构框图可以不断分解一直到门级或晶体管级;

(2)高级语言:(如C语言来表示)形成结构模拟器,用于性能评估和分析;

(3)硬件描述语言:(如:Verilog)可通过电子设计自动化EDA工具,进行功能验证和性能分析,转化成门级及晶体管网表,并通过布局布线最终转换成版图,用于芯片制造。

造CPU必须知道:

- 指令是是应用的“算子”;(要知道哪些是硬件实现?哪些是软件实现?)

- 结构设计要结合应用行为,例如:

Cache利用应用访存局部性;

转移猜测利用转移相关性和重复性 - ISA和微结构要考虑OS需求;(页表和TLB,多线程支持,虚拟机支持)

- 结构设计要考虑晶体管属性,例如:

cache容量影响主频;

多发射结构发射电路影响主频;

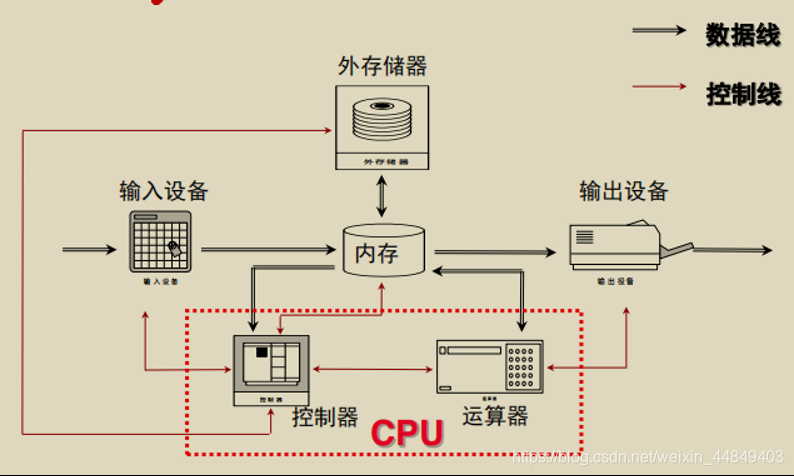

冯诺依曼结构:

1.基本原理:存储程序和指令驱动执行

①计算机由存储器、运算器、控制器、输入设备、输出设备五部分组成,其中运算器和控制器合称称CPU;

②存储器是按地址访问的线性编址的一维结构,每个单元的位数固定。指令和数据不加区别混合存储在同一个存储器中。

③控制器从存储器中取出指令并依指令要求发出控制信号控制计算机的操作。控制器中的程序计数器指明要执行的指令所在的存储单元地址。程序计数器一般按顺序递增,但可按指令要求而改变。

④以运算器为中心,输入输出(IO)设备与存储器之间的数据传送都经过运算器。

2.演进:

(1)中心:运算器–>存储器:数据流向更加合理,使运算器、存储器和IO设备能并行工作。

(2)控制:单一集中–>分散:早期计算机工作速度低,运算器、存储器、控制器和IO设备可在同一个时钟信号控制下同步工作。现在运算器、存储器与IO设备的速度差异很大,需要异步分散控制。

(3)串行算法–>适应并行算法:出现了流水线处理器、超标量处理器、向量处理器、多核处理器、对称多处理机(Symmetric Multiprocessor,简称SMP)、大规模并行处理机(Massively Parallel Processing,简称MPP)和机群系统等。

(4)出现为适应特殊需要的专用计算机:如图形处理器(Graphic Processing Unit,简称GPU)、数字信号处理器(Digital Signal Processor,简称DSP)等

补: 哈佛结构

将冯诺依曼结构里的指令和数据分开存储。

目前的计算机没有能突破该特征的,都是对冯诺依曼结构的变种(如哈佛结构、并行结构等)

3.优缺点:

优:自动快速执行

缺:指令驱动的顺序执行;CPU和存储器分开且越来越远。

衡量计算机的指标—主要内容:性能、价格、功耗

性能

1.性能的本质定义:

以指令为基本单位,完成一个任务所需的时间;

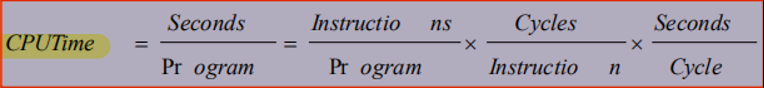

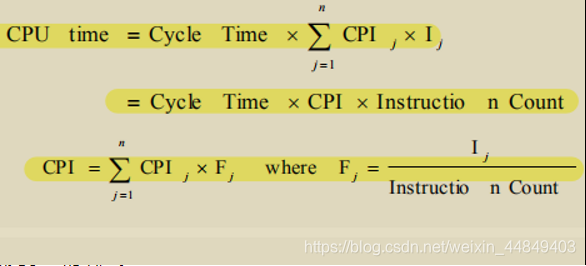

程序的CPU时间=程序指令数 x 每条指令时钟周期数 x 时钟周期

2.影响性能的因素:

算法(影响最大):如冒泡排序复杂度为O(N*N),快速排序复杂度为O(NlogN)

编译器影响:一般有几倍的差距

指令系统:复杂指令如三角函数、FFT、AES等是否硬件实现

微结构:IPC(Instructions per cycle):通过乱序执行、多发射、存储层次等提高IPC

主频:受工艺和微结构(流水线)的影响

①主频降低,单核性能大幅提高;

②性能的提高少量来自于自动并行化,主要是浮点;

③主要通过结构优化提高性能:骨架做大(如:多访存部件等)、细节做精(结合应用具体优化)

3.评价原则:

拿基准测试程序来测,而不是看个别技术指标(如:主频等)

(1)注意点:

①对于不同的计算机,侧重点不同需要采用不同的测试程序;

(例如:个人PC在乎单任务关注响应时间,计算中心多任务更关注吞吐量)

②测试程序要有代表性,要足够大,而不是拿个别程序册,要能全面综合评价计算机性能;

③多个程序测试时,最后应该采用几何平均,这样放映的结果更加公平;

> 算术平均值的权重与特定程序在特定机器上的执行时间成正比,所以权重不仅与该程序的执行频度有关,也与运行该程序的机器特性和输入数据相关。可能导致测试者把自己机器上运行最快的程序的输入量增到最大,以提高计算该程序平均值时的权重,干扰了真实结果。

> 几何平均:优点:小于算术平均值、与参考机无关、强调性能平衡。缺点:可能导致硬件和软件设计者集中精力提高最易提高速度的软件的性能,而不是提高速度最慢的软件的性能。

④当负载中各程序的执行百分比不同时,常用方法:计算加权执行时间、“归一化”(将执行时间对一台参考机器进行归一化,然后取其归一化执行时间的平均值)

⑤测试报告要足够详细,要公开,要可以检查;

(2)常见的基准测试程序套件:

SPEC CPU基准测试程序、TPC(事务处理测试程序)、EEMBC(嵌入式基准测试程序)、LMBench(比较不同的unix系统性能)

4.CPI和IPC

在指令系统确定后,系统结构设计者的主要目标就是降低CPI或提高IPC

CPI=(CPU时间*CLOCK Rate频率)/ 指令数 = 时钟周期数 / 指令数

成本

1.成本和性能的关系:

①. 超级计算机:不计成本,只追求性能

②. 嵌入式应用:为降低功耗和成本,可以牺牲一部分性能

③. 介于两者之间:比如PC机,工作站,服务器等:追求性能价格比的最优设计

2.影响成本的因素:

生产成本降低,加速学习降低一次性成本,商品竞争量的增加。

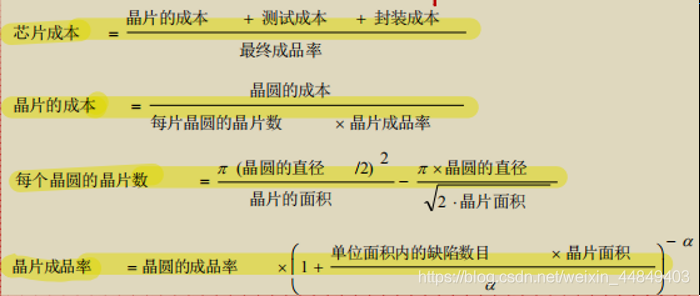

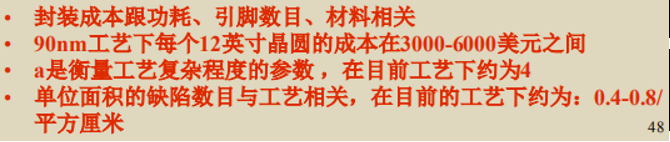

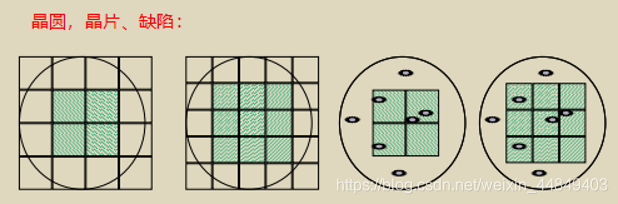

3.芯片成本:

功耗

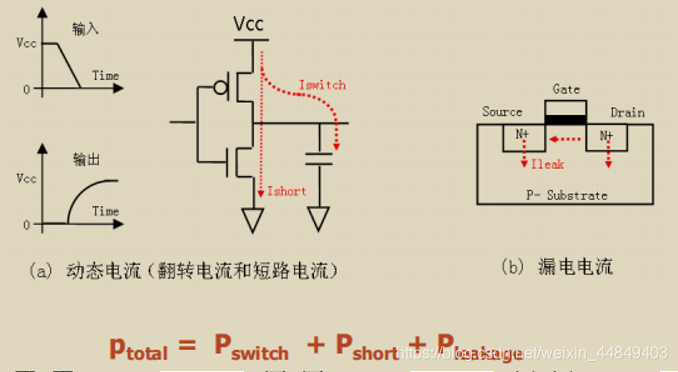

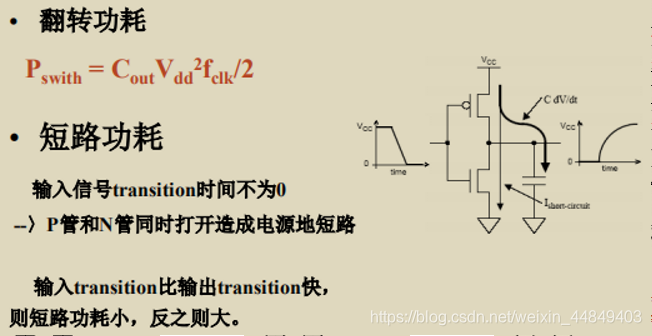

动态功耗:

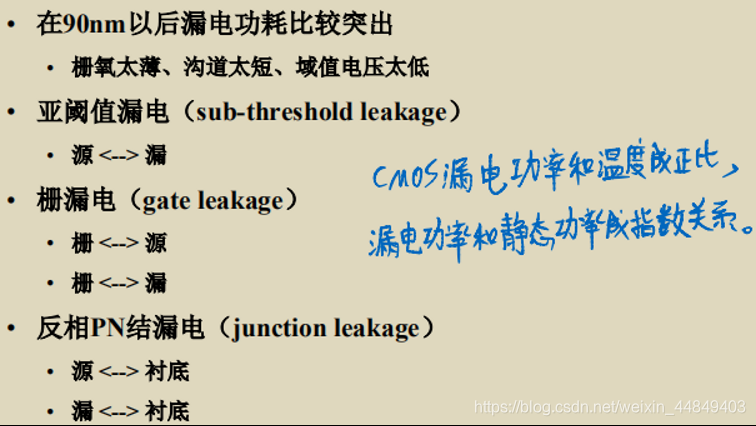

CMOS静态功耗:

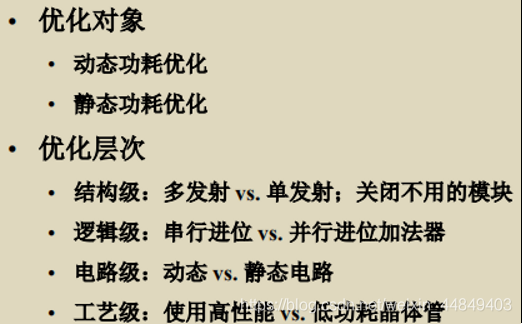

降低功耗的方法:

计算机体系结构发展趋势:

1.动力:

①. 半导体工艺技术和计算机体系结构技术互为动力;

②. 应用需求是计算机体系结构发展的持久动力;

③. 主要动力:2010年代前工艺技术,2010年代后应用需求;

2.摩尔定律–非客观规律,是人们努力的结果

晶体管数目每18-24个月翻一番;同样晶体管数量的芯片价格下降一倍,现在买一颗大米的钱可以买100-1000只晶体管;

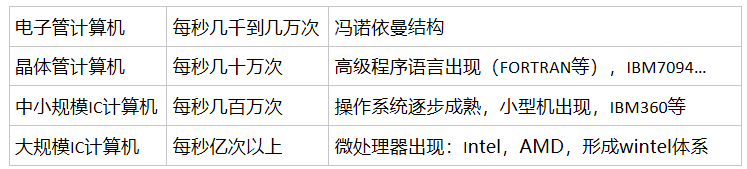

(1)第一代到第四代:摩尔定律与结构进步

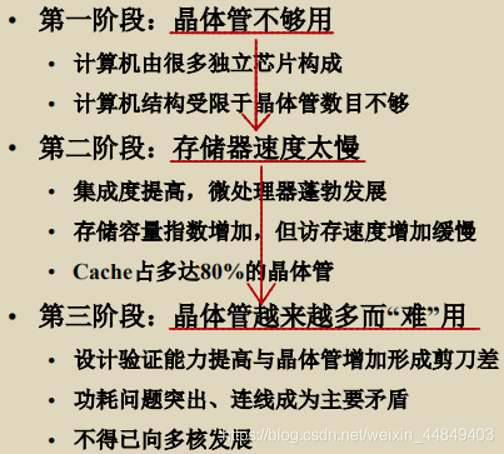

(2)摩尔定律与系统结构:

(3)CMOS工艺正面临物理极限

难以进一步缩小已经达成共识,所以会不会有新材料及新器件技术取代CMOS?(硅的平台不可能被取代,但硅平台上生长的器件会不断改进:如碳纳米管)

3.计算机应用与体系结构:

发展趋势:

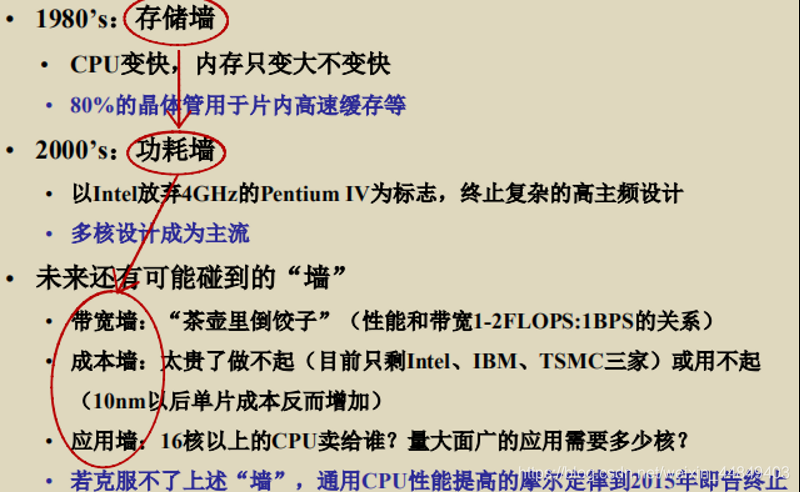

4.计算机体系结构发展中碰到的“墙”:

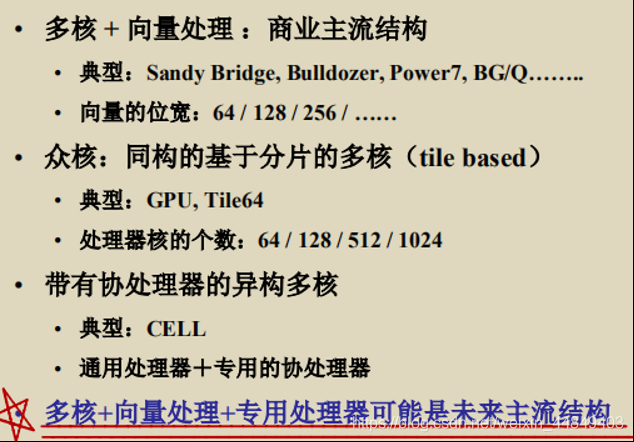

5.未来可能会流行的CPU结构:

计算机体系结构设计的基本原则

①. 平衡性:结构设计要统筹兼顾

②. 局部性:结构设计要重点突出

③. 并行性:人多力量大,开发各个层次的并行性

④. 虚拟化:自己麻烦点,让用户好用点

(1)平衡性:

1)木桶原理:短板决定总体性能;

2)访存和计算机的平衡:经验定律使然,为保持通用性,峰值浮点运算速度(MFLOPS)和峰值访存带宽(MB/s)为1:1左右;

3)Amdahl定律(关注短板):通过使用某种较快的执行方式所获得的性能的提高,受可使用这

种较快执行方式的时间所占的百分比例的限制

(2)开发局部性:

1)计算机中的局部性事件:

> 指令局部性:指令顺序执行,循环体中的指令

> 访存局部性:时间局部性和 空间局部性

> 转移局部性:同一条转移指令经常往同一个方向跳转

(Cache、TLB、预取、转移猜测)

2)当结构设计基于平衡后,优化性能要抓住主要矛盾,重点改进最频繁发生事件的执行效率;

(3)开发并行性:

► 指令级并行

> 是过去的20年里体系结构设计者提升性能的主要途径

> 时间并行性:指令流水线

> 空间并行性:SuperScalar(Out-of-Order)和EPIC(编译器优化)

> 进一步挖掘指令级并行的空间不大

► 数据级并行:SIMD

> 向量机、SSE多媒体指令

> 作为指令级并行的有效补充,在高性能计算及流媒体等领域发挥重要作用,在专用处理器中应用较多

► 线程级并行

> 线程级并行大量存在于Internet应用

> 多核处理器及多线程处理器

(4)虚拟化:

► 虚拟化:应用和实现的“桥梁”

> 用起来是这样的,实际上是那样的

> 逻辑上是这样的,物理上是那样的

> 宁愿自己多费点事,也要用尽量为用户提供一个好用的接口

► 计算机中的“桥梁”

> 操作系统对虚拟地址空间的支持(CPU中实现TLB)(特优)

> 多发射在维持串行编程模型的情况下提高了速度(优)

> 多线程和虚拟机技术在单一硬件上虚拟出多个CPU(优)

> Cache在维持一维的地址空间的情况下提高了速度(良)

> Cache一致性协议在分布存储的情况下提供统一编程空间(一般)