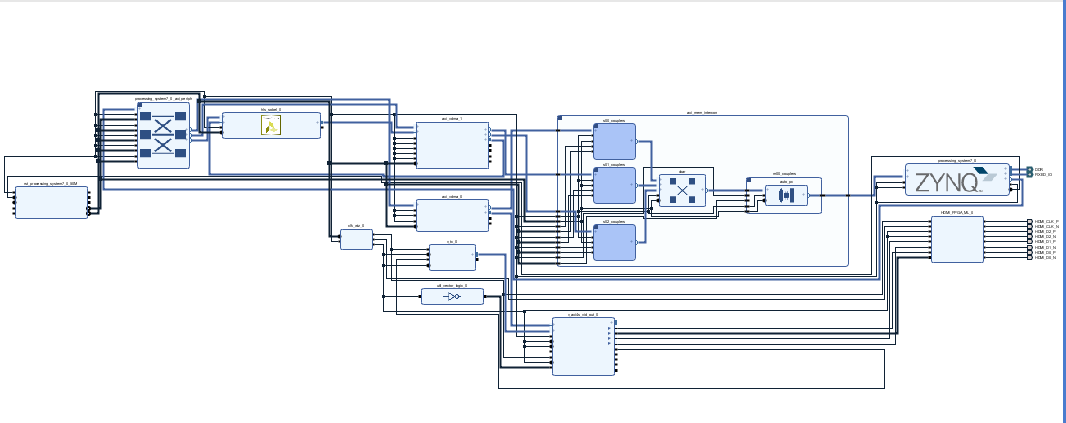

重点分析一、AXI_VDMA_1

之前一直认为这个就是内含有DDR的ip核(......最近才搞懂是个啥),后来经过对FDMA的分析发现这就是个框架,通AXI总线挂载到bus总线,可以实现PL端FPGA代码直接读写PS侧的DDR。

几个关键的AXI(AXIS)总线接口:

(1)、S_AXI_LITE接口:该接口收到ZYNQ核和GP总线控制,M_AXI_GP接口通过AXI-Lite总线控制VDMA的配置

(2)、M_AXIS_MM2S接口:本接口将从DDr中读取的数据发送到sobel处理ip

(3)、M_AXIS_S2MM接口:该接口接收sobel处理ip核的输出数据流

(4)、M_AXI_S2MM接口:该接口将数据输出到ZYNQ处理器,然后数据可以刷入DDR

(5)、M_AXI_MM2S接口:该接口接收来自DDR的像素数据

学习完FDMA之后,对VDMA才有了一个初步的了解,VDMA就是通过AXI(AXIS)总线挂载到总线的典型应用,M_AXI_MM2S接口接收到来自ps侧DDR的像素数据,然后通过M_AXI_MM2S将数据发送到sobel ip核,ip对图片数据进行处理后进行将数据转换为AXI_STREAM格式,可以在上一篇博文中看到,输出数据通过S_AXIS_S2MM进入VDMA,然后,由于在VDMA中设置的是三帧缓存,这三帧数据并不是在VDMA中缓存的,是在DDR中进行缓存。那么VDMA与三帧数据的关系是什么?参考FDMA中的设计,CDMA就是对输入数据设计了一个标志位flag,保证有三帧数据传送到DDR进行缓存。数据通过M_AXI_MM2S接口进入DDR。

那么,AXI_CONNECT1的作用中有一个S00_AXI的作用=是什么?可以看到该总线发出读请求,读取ps侧DDR缓存的像素数据。

其他分析一、AXI_VDMA

框架流程:就是将图像数据以而进行形式进行存储,ZYNQ通过AXI_GP接口对各个模块进行配置,将sobel处理的结构通过stream数据流发送到vdma0,再经过stream2video进行转换,将输出图像发送到HDMI核,video timing核的作用是进行时钟约束,其中HDMI的主时钟是74.25Mhz,除此之外还输入一个串转并数据时钟,为主时钟的5M:74.25*5Mhz。

回宿舍了,写不完了,鸽了鸽了