概述

主要分析SOC系统中功耗来源的基本原理

功耗来源

数字CMOS电路中功耗来源主要包括:动态功耗,静态功耗,短路功耗。

动态功耗

动态功耗主要指电路翻转时对负载电容充放电产生的。

如图,为反相器电路,当V-in输入为低电平时,PMOS导通,电容充电,V-out输出为高;当V-in为高电平时,PMOS管截至,NMOS管导通,电容放电,V-out输出为低。电容充放电过程产生动态功耗。在输出有0跳变到1,或1跳变到0,产生动态功耗。

动态功耗公式如下:

P_dynamic=KfC_L V_dd^2;

K为单位时间跳变次数,f为时钟频率;

动态功耗和工作电压,部件工作频率,电容相关,所以降低动态功耗主要研究降低工作电压,降低负载电容,降低时钟频率和电路工作次数。

短路功耗

输入电压V-in在高低电平之间切换时,如果V-in大于NMOS导通门限电压,并小于PMOS导通电压值,N管和P管同时导通,V-dd和GND形成通路,产生短路电流。

短路功耗公式为:

P_short=I_mean V_DD==β(V_dd-V_t )^3 τ/12T;

V_t为阈值电压,T为时钟周期,τ为电路电平从变化到稳定时间,β由电路工艺参数决定。

降低短路功耗主要是降低工作电压,提供阈值电压以及改善电路工艺;

降低短路功耗主要是降低工作电压,提供阈值电压以及改善电路工艺;

静态功耗

Mos电路PN结中存在方向电流,形成静态功耗。

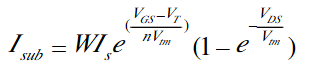

静态功耗公式为:

V_t为阈值电压;

当阈值电压下降时,流电流呈指数正常。在深亚微米工艺里,泄露电流重点研究输入向量的控制技术。

功耗影响分析

动态功耗;在电源电源较高时主要功耗来源,占75%-90%

静态功耗:整个电路功耗中不到1%,一般可以忽略,但在会增加到不可忽略地步,需要专门优化。一旦晶体管上电,这些漏电流就会存在,它与时钟频率或开关频率无关。降低时钟信号频率或关闭时钟频率都无法使它减小。但是,通过降低电源电压,或者完全切断晶体管的供电,可以减小甚至消除漏电流。

短路功耗:对于转换较快电路,可以忽略;对于转换较慢电路,占10%-30%