1.项目简介

用索尼的imx264 sensor采集图像,在内部模数转换之后,由lvds接收,然后解码,最后送给后端显示

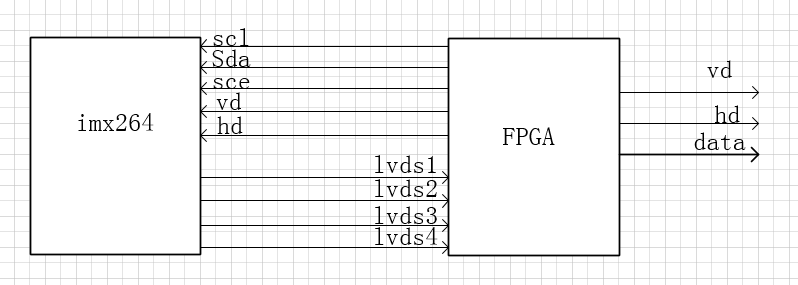

2.框图

imx264配置成从模式,由spi总线配置,需要由FPGA提供 行、场信号,imx264根据接收到的行场信号输出四路数据,FPGA用lvds IP核接收这四路数据,然后还原成正确的像素,再产生相应的行场,与数据一起送给后端显示

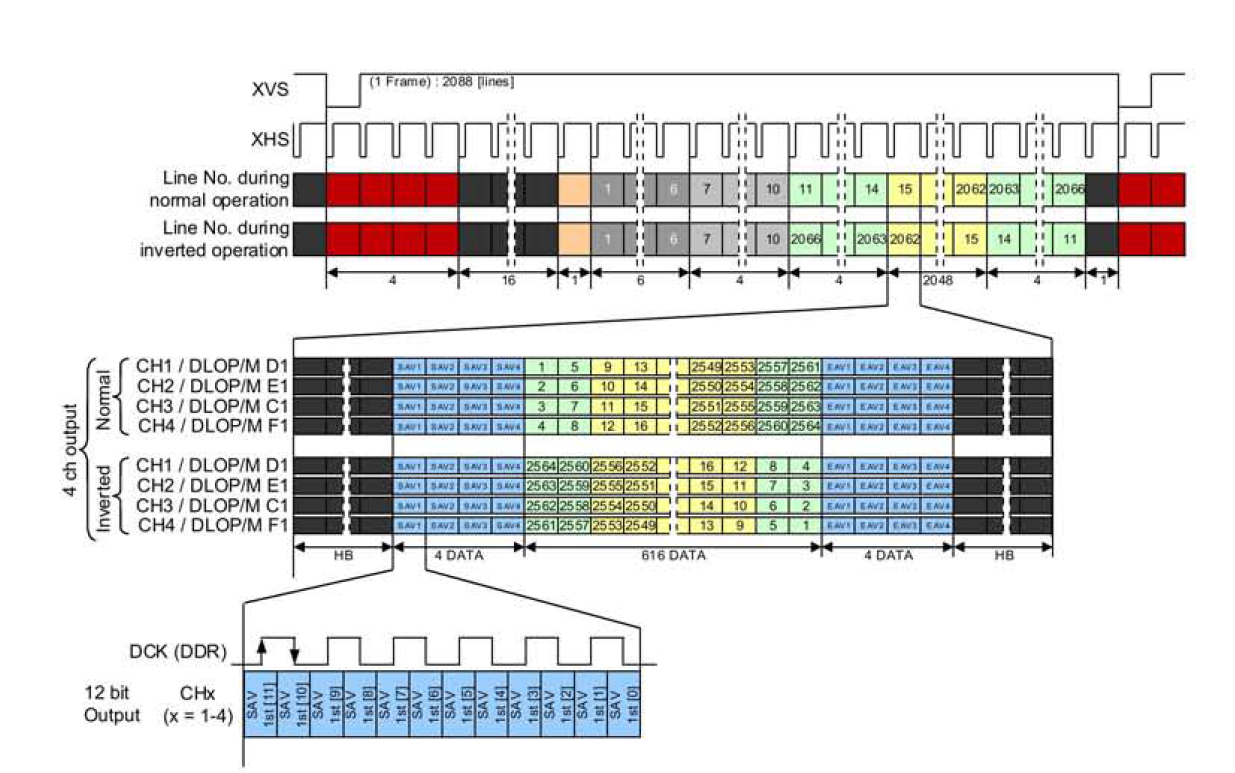

3.时序

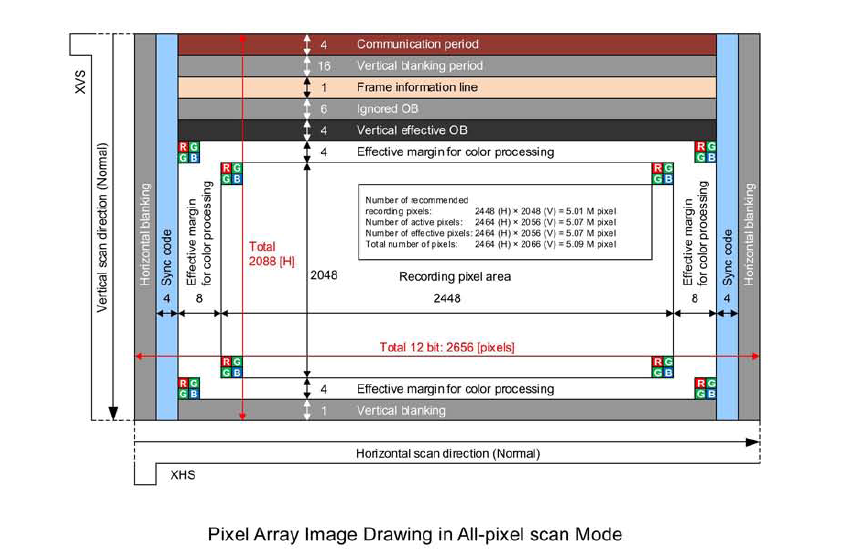

由时序图可以看到,一帧一共2088行(有效行2048行),每行2656个像素点(有效像素点2448个)。每行有头同步字和尾结束同步字。每个像素12bit,先送高位再送低位。

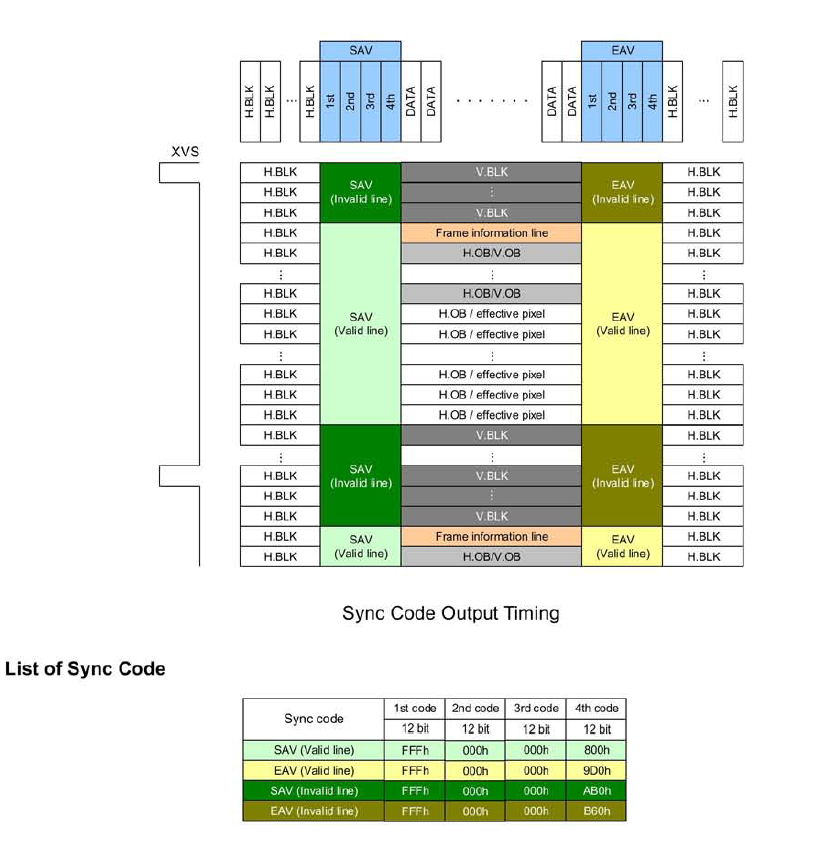

4.同步字

由同步字可以看出,一帧2088行分为通讯期(4行,无同步字),消隐期(16行,头同步字fff,尾同步字AB0),信息行(1行),ob行(10行),像素边缘行(8行,上4+下4),有效行2048行,尾消隐期(1行)。对应的同步字见图。

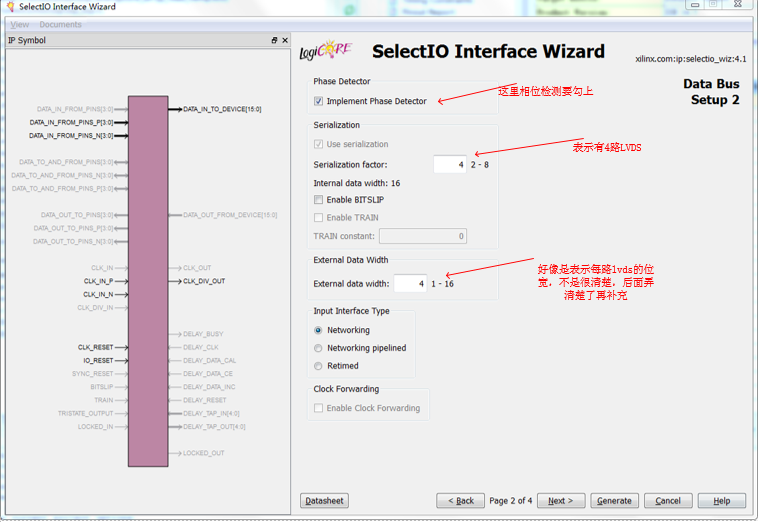

5.lvds IP核配置

由于从imx264送过来的是差分时钟和差分数据,所以配置成差分时钟和差分数据,后面也没什么东西了

6.仿真

说明

1.根据imx264的数据手册,一帧图像有2656*2088个像素点,每个像素12bit,35.7帧每秒。所以一共有2656*2088*12*35.7=2.376Gbps。一共分四路输出,所以每路输出的数据量为2.376/4=594mbps。因为是双沿输出数据,所以差分时钟为594/2=297m。

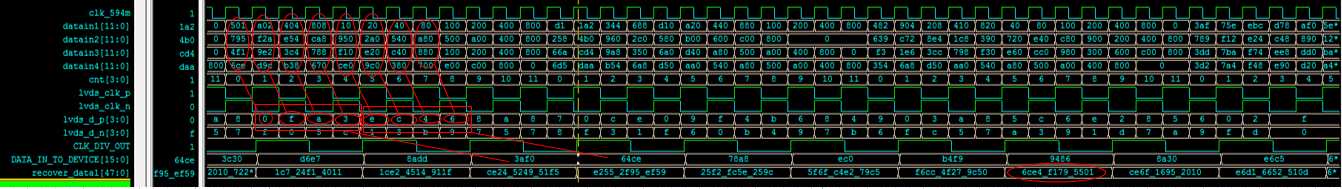

2.在594m的时钟下产生4路12bit数据,每个时钟进行移位,12次移完。只看data1-data4的最高位。每个时钟下data1-data4的最高位组成一个4bit的差分数据。这个由LVDS的配置决定。

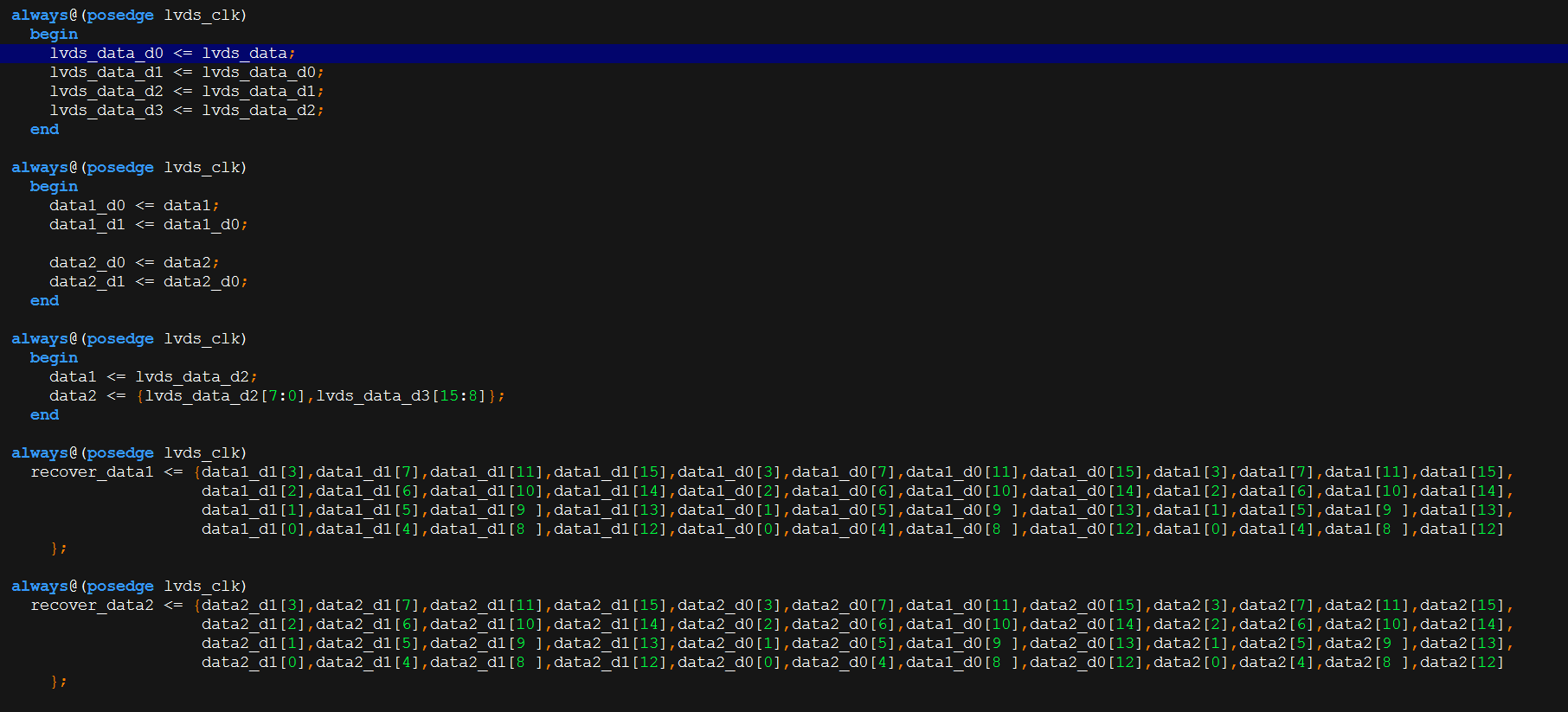

3.lvds IP 核把4个4bit的数据组成一个16bit的数据数据,把最先进来的数据放在最低位,最后进来的数据放在最高位。我们需要把lvds输出的数据进行解析,需要把3个16bit的数据还原成4个12bit的数据。

4.lvds输出来的数据有两种情况。看上图lvds_d_p这个信号,LVDS IP核可能会把fo8a组成一个16bit的数据输出,也可能把3af0组成一个16bit数据输出。如果是f0a8这种输出,f0是由后面的4个12bit数据产生的,8a是由前面4个12bit数据产生的。而且会根据上电,可能会来回切换,所以要准备两种解析方式。代码如下 lvds_data表示lvds IP核输出的数据recover_data1核recover_data2表示两种方式解析出来的数据。(如果lvds IP核里面的数据位宽配置成2,就不会出现这种情况)

7.输出显示

根据两种方式解析出来的数据进行检测同步字,根据同步字指示出有效数据,然后进行乒乓缓存,同时产生相应的行场信号,