亚稳态是由于违背触发器的建立保持时间而产生的不稳定状态;并非所有不满足建立时间保持时间的输入变化都会导致亚稳态输出,触发器是否进入亚稳态和返回稳态所需要时间取决于生产期间工艺技术与外界环境。一般来说,触发器都会在一个或者两个周期内返回稳定值。

亚稳态产生的情况:

1.输入信号是异步信号(比如复位信号);

2.信号在两个不同频率或者相同频率但相位和偏移不同的时钟域下跨时钟域工作(不同频或者同频不同相);

3.时钟偏移和时钟抖动(上升/下降时间)高于容限值;

4.组合延迟使触发器的数据输入在亚稳态窗口内发生变化(组合电路延迟);

解决亚稳态的方式:

1.通常最简单的解决方法为降频使时钟周期足够长(但此方法在实际设计中不实用);

2.使用同步器的方式:

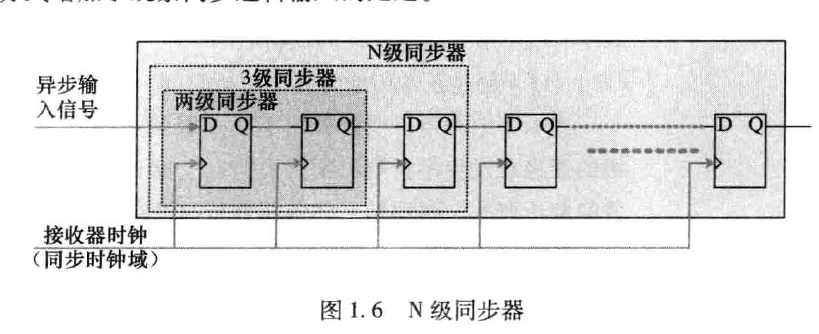

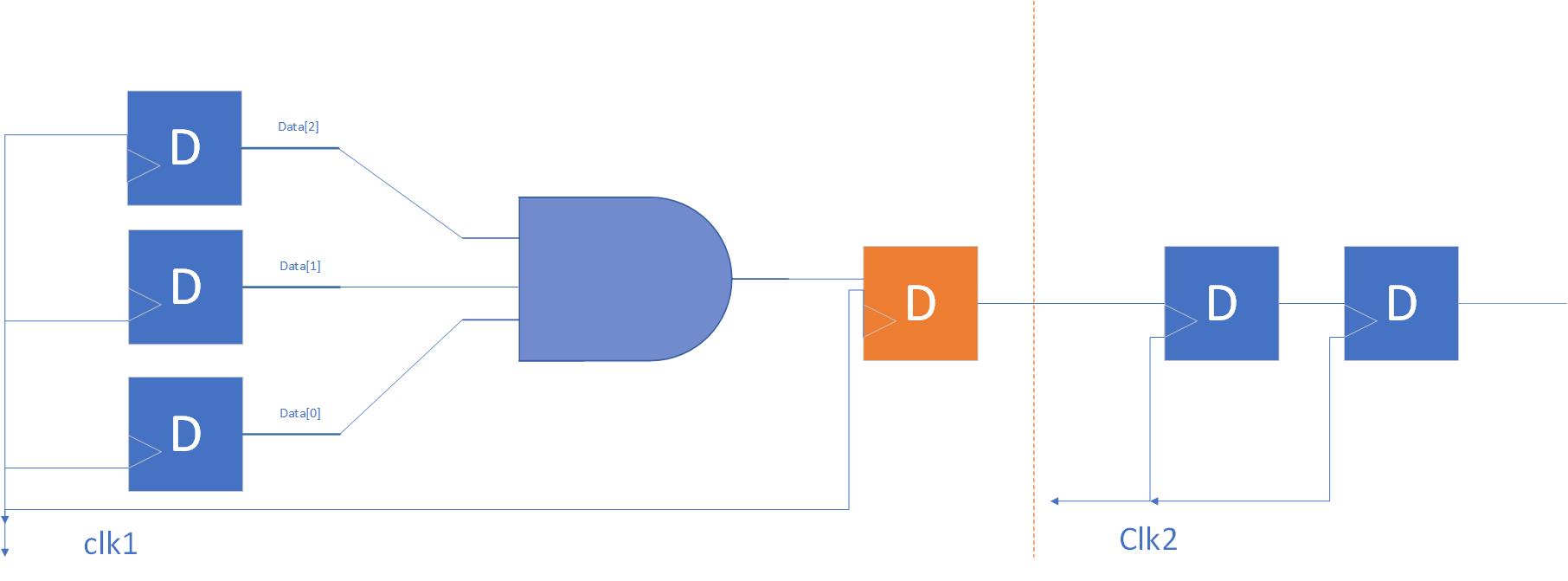

2.1.简单的多级同步器,

2.2.使用时钟倍频的多级同步器

其中前级时钟内经过组合逻辑必须要寄存器寄存一拍消除毛刺;

2.3.还可以采用握手处理和FIFO形式;

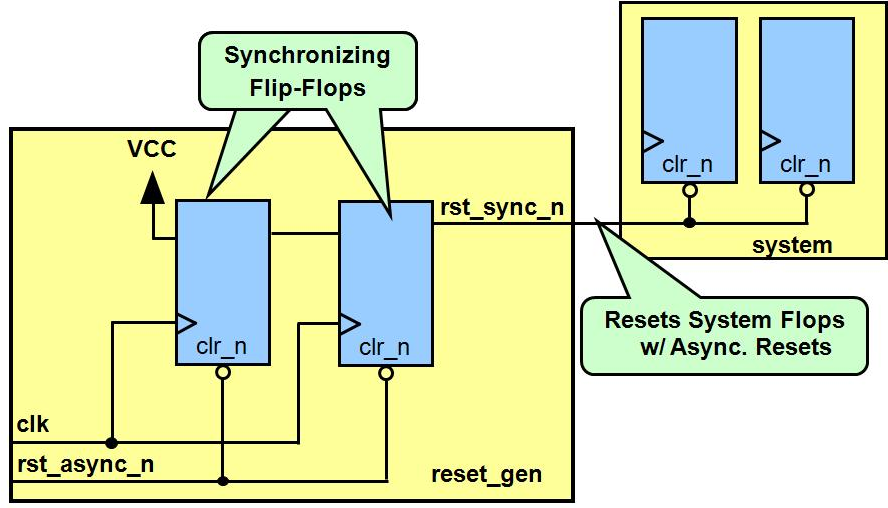

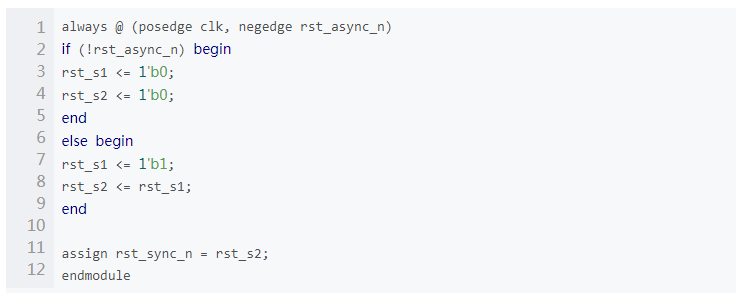

3.对于复位异步信号避免亚稳态形式可以采用,异步复位同步释放的形式

4.对于时钟偏:

及Tskew问题采用全局时钟的形式避免

5.组合延迟导致的问题

Trouting+Tlogic,其中Tlogic可以通过retiming去实行,或者复制电路减少扇出,或者其插入寄存器;

Trouting中可以采用一些约束,比如多周期约束,或者是物理约束,位置约束,或者采用手动布线。

亚稳态测试电路: