视频链接地址

实验一:

http://v.youku.com/v_show/id_XMTg1MzYzNzEzMg==_type_99.html

实验二:

http://v.youku.com/v_show/id_XMTg1MzYzNzExMg==.html

实验目的(内容要求)

实验内容一

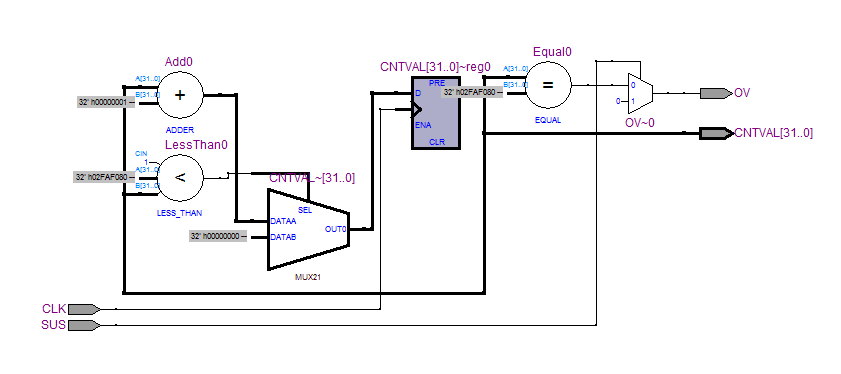

手工绘制的RTL电路图

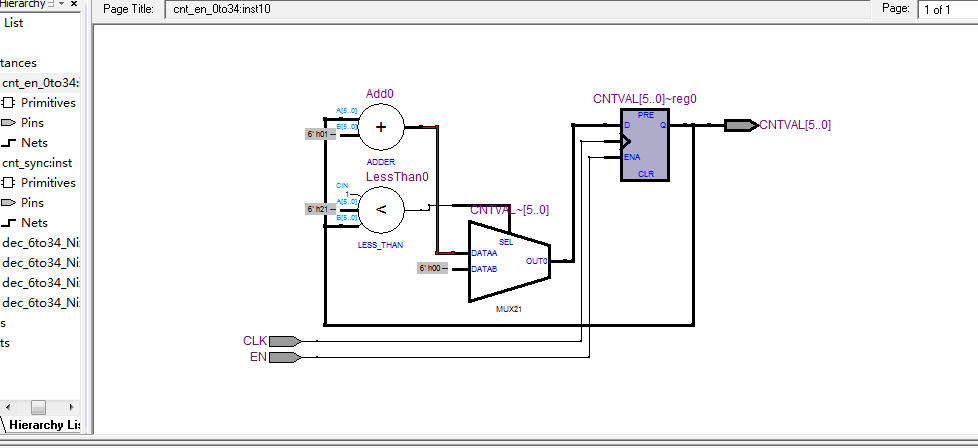

在代码中又添加了复位与暂停功能,在本图中并没有显示

Quartus扫描生成的RTL电路图

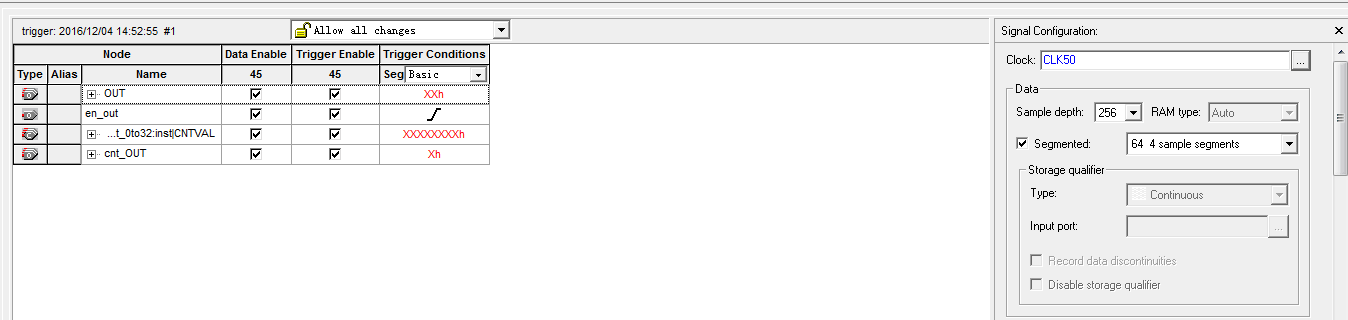

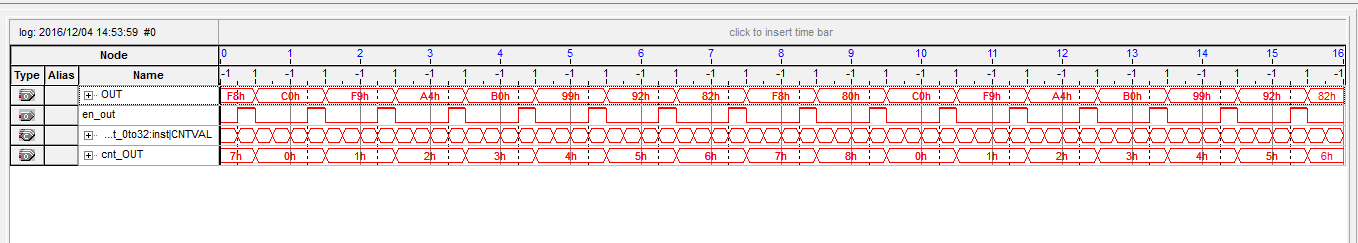

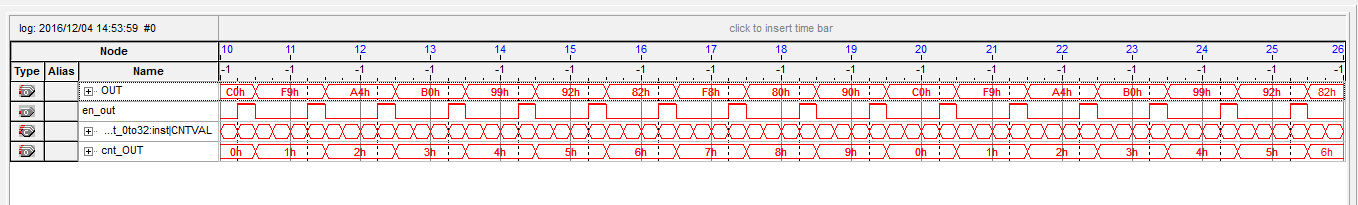

计数器的计数值的SignalTap截图

代码

//////////////module cnt_sync////////////////////////

module cnt_sync(

CLK , // clock

SUS , // suspend

CNTVAL, // counter value

OV ); // overflow

input CLK;

input SUS;

output [32-1:0] CNTVAL;

output OV;

parameter CNT_MAX_VAL = 50_000_000; //将最大值设置为常数50_000_000

reg [32-1:0] CNTVAL;

reg OV;

always @ (posedge CLK) begin

//计数值小于最大计数值,加1。否则,为0

if(CNTVAL >= CNT_MAX_VAL)

CNTVAL <= 0;

else

CNTVAL <= CNTVAL + 1'b1;

end

always @ (CNTVAL) begin

if(SUS) //suspend work

OV = 1'b0;

else begin //OV以周期1秒输出高电平

if(CNTVAL == CNT_MAX_VAL)

OV = 1'b1;

else

OV = 1'b0;

end

end

endmodule

//////////////module cnt_en_0to6789///////////////////////

module cnt_en_0to6789(

CLK , // clock

CNTVAL, // counter value

EN , // enable

RST , //RESET

OV ); // overflow

input CLK;

input EN;

input RST;

output [4-1:0] CNTVAL;

output OV;

reg [4-1:0] CNTVAL;

reg [4-1:0] CNT_MAX_VAL = 6; //最大计数值初始值设为6

reg OV;

always @ (posedge CLK ) begin

if(RST == 0) begin //RESET work

CNTVAL <= 0;

CNT_MAX_VAL <= 6;

end

else begin

if(EN) begin // work enable

if(CNTVAL >= CNT_MAX_VAL) begin

//计数值大于等于最大计数值,为0

CNTVAL <= 0;

if(CNT_MAX_VAL < 9) //最大计数值小于9,加1.否则,为6

CNT_MAX_VAL <= CNT_MAX_VAL +1'b1;

else

CNT_MAX_VAL <= 6;

end

else //计数值小于最大计数值,加1

CNTVAL <= CNTVAL + 1'b1;

end

else

CNTVAL <= CNTVAL ; // hold same value

end

end

endmodule

//////////////module dec_4to9_Nixietube//////////////

module dec_4to9_Nixietube(

IN ,

OUT

);

input [4-1:0] IN;

output [8-1:0] OUT;

reg [8-1:0] OUT;

always@(IN)

begin

case(IN)

4'b0000: OUT = 8'b11000000; // Nixietube_0

4'b0001: OUT = 8'b11111001; // Nixietube_1

4'b0010: OUT = 8'b10100100; // Nixietube_2

4'b0011: OUT = 8'b10110000; // Nixietube_3

4'b0100: OUT = 8'b10011001; // Nixietube_4

4'b0101: OUT = 8'b10010010; // Nixietube_5

4'b0110: OUT = 8'b10000010; // Nixietube_6

4'b0111: OUT = 8'b11111000; // Nixietube_7

4'b1000: OUT = 8'b10000000; // Nixietube_8

4'b1001: OUT = 8'b10010000; // Nixietube_9

default: OUT = 8'b11111111; /* Nixietube_darkness*/

endcase

end

endmodule

实验内容二

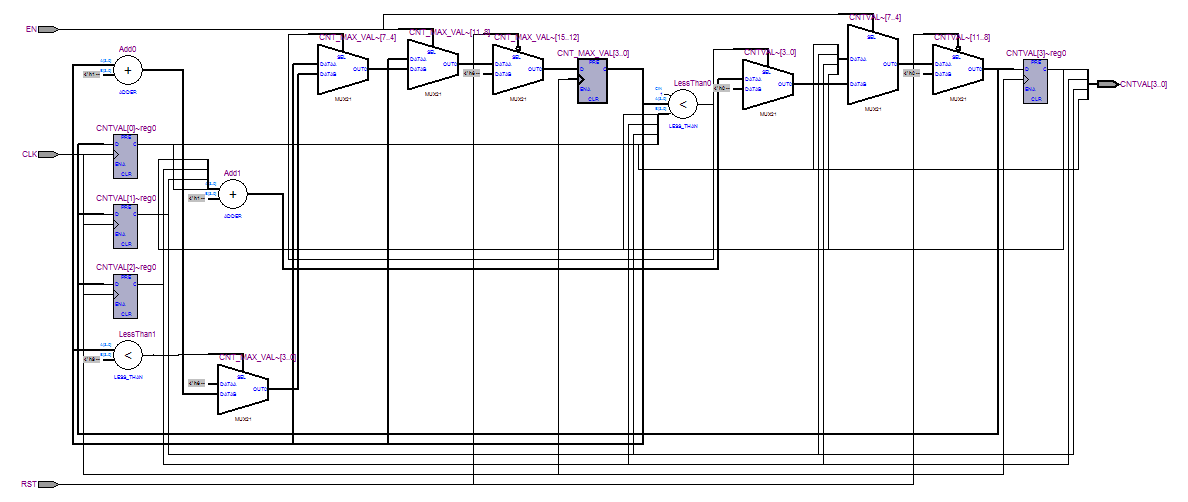

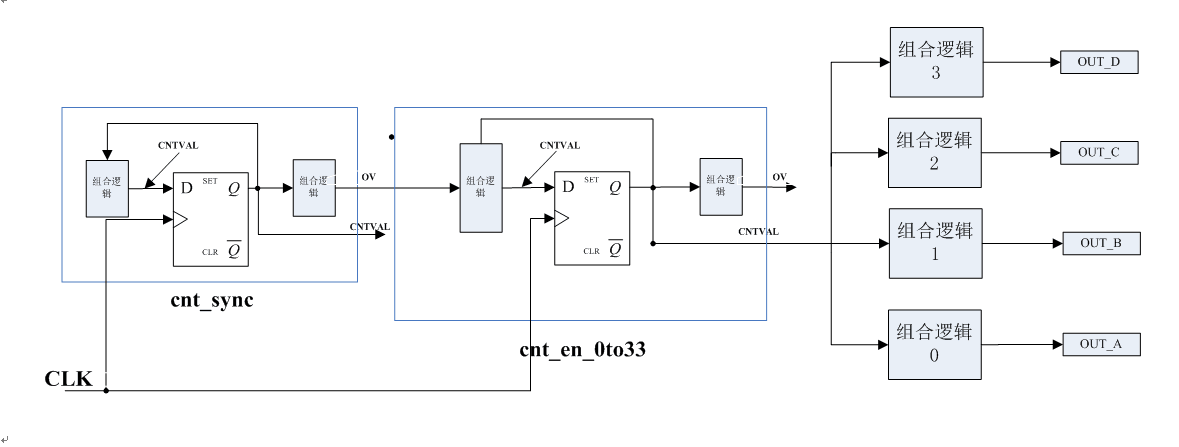

手工绘制的RTL电路图

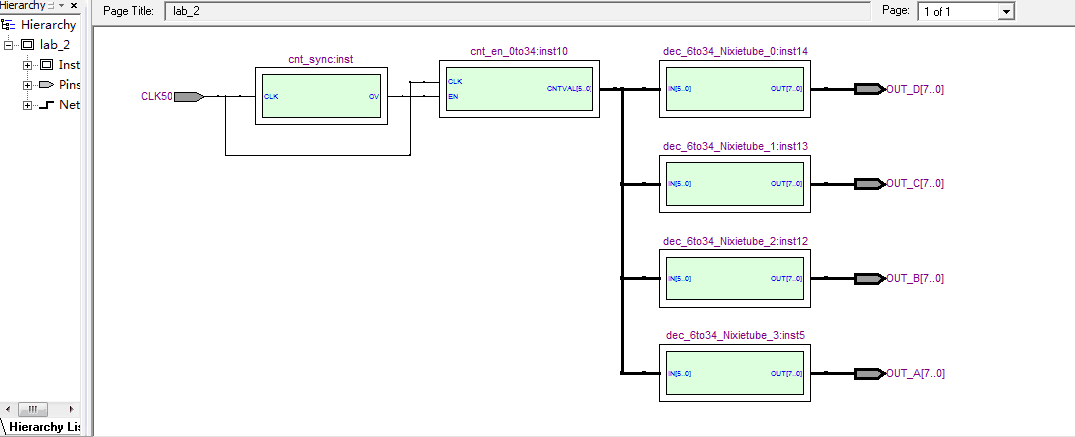

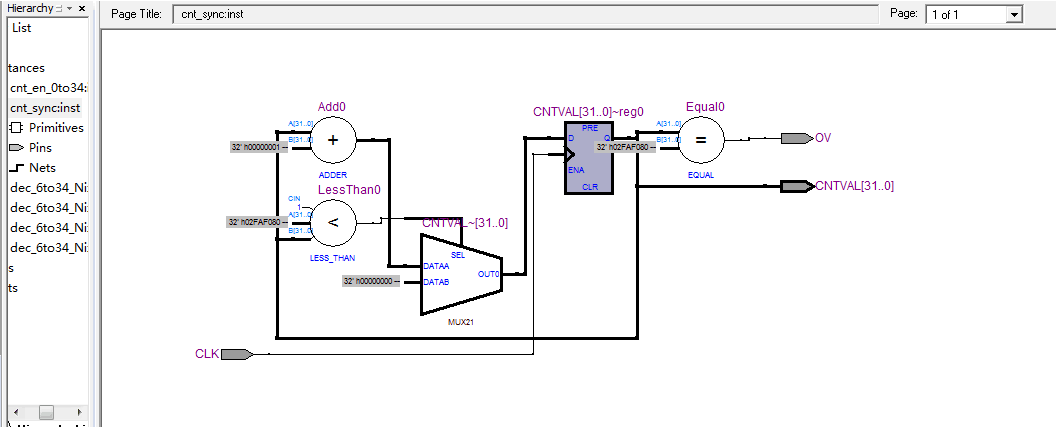

Quartus扫描生成的RTL电路图

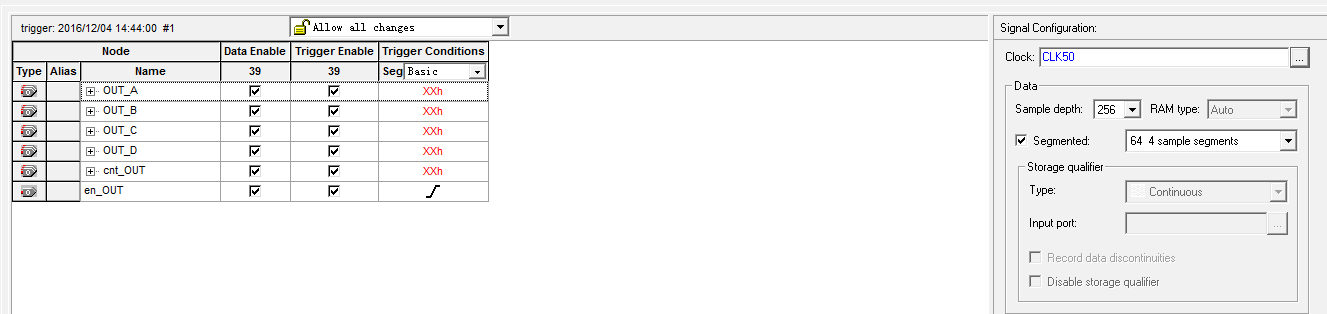

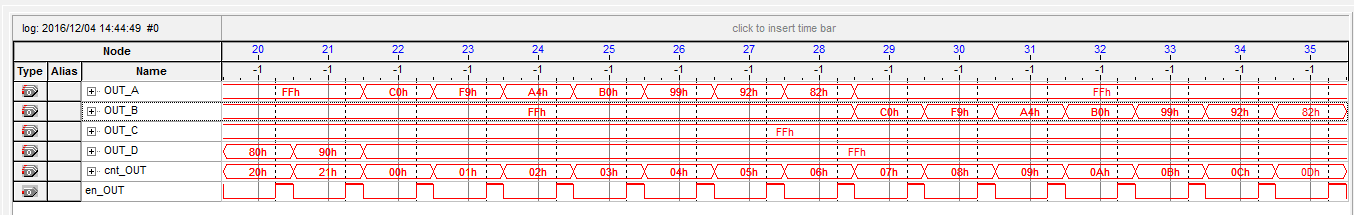

计数器的计数值的SignalTap截图

代码

/*/////////////module cnt_sync///////////////////////*/

module cnt_sync(

CLK , // clock

CNTVAL, // counter value

OV ); // overflow

input CLK;

output [32-1:0] CNTVAL;

output OV;

parameter CNT_MAX_VAL = 50_000_000;

/* 将最大值设置为常数50_000_000 */

reg [32-1:0] CNTVAL;

reg OV;

always @ (posedge CLK) begin

/* 计数值小于最大计数值,加1。否则,为0 */

if(CNTVAL >= CNT_MAX_VAL)

CNTVAL <= 0;

else

CNTVAL <= CNTVAL + 1'b1;

end

always @ (CNTVAL) begin

if(CNTVAL == CNT_MAX_VAL)

OV = 1;

else

OV = 0;

end

endmodule

/*////////////module cnt_en_0to33///////////////////*/

module cnt_en_0to33(

CLK , // clock

CNTVAL, // counter value

EN ); // enable

input CLK;

input EN;

output [6-1:0] CNTVAL;

reg [6-1:0] CNTVAL;

always @ (posedge CLK) begin

if(EN) begin // work enable

if(CNTVAL >= 33) /* 计数器一个周期为0到33 */

CNTVAL <= 0;

else

CNTVAL <= CNTVAL + 1'b1;

end

else

CNTVAL <= CNTVAL; /* hold same value */

end

endmodule

/*/////////////module dec_6to34_Nixietube_3///////////*/

module dec_6to34_Nixietube_3(

IN ,

OUT

);

input [6-1:0] IN;

output [8-1:0] OUT;

reg [8-1:0] OUT;

always@(IN) begin

case(IN)

6'b000000: OUT = 8'b11000000; /* Nixietube_0 */

6'b000001: OUT = 8'b11111001; /* Nixietube_1 */

6'b000010: OUT = 8'b10100100; /* Nixietube_2 */

6'b000011: OUT = 8'b10110000; /* Nixietube_3 */

6'b000100: OUT = 8'b10011001; /*Nixietube_4 */

6'b000101: OUT = 8'b10010010; /* Nixietube_5 */

6'b000110: OUT = 8'b10000010; /*Nixietube_6 */

default : OUT = 8'b11111111; /* Nixietube_darkness */

endcase

end

endmodule

/*////////////module dec_6to34_Nixietube_2///////////*/

module dec_6to34_Nixietube_2(

IN ,

OUT

);

input [6-1:0] IN;

output [8-1:0] OUT;

reg [8-1:0] OUT;

always@(IN)

begin

case(IN)

6'b000111: OUT = 8'b11000000; /* Nixietube_0 */

6'b001000: OUT = 8'b11111001; /* Nixietube_1 */

6'b001001: OUT = 8'b10100100; /* Nixietube_2 */

6'b001010: OUT = 8'b10110000; /* Nixietube_3 */

6'b001011: OUT = 8'b10011001; /* Nixietube_4 */

6'b001100: OUT = 8'b10010010; /* Nixietube_5 */

6'b001101: OUT = 8'b10000010; /* Nixietube_6 */

6'b001110: OUT = 8'b11111000; /* Nixietube_7 */

default : OUT = 8'b11111111; /* Nixietube_darkness */

endcase

end

endmodule

/*//////////////module dec_6to34_Nixietube_1//////*/

module dec_6to34_Nixietube_1(

IN ,

OUT

);

input [6-1:0] IN;

output [8-1:0] OUT;

reg [8-1:0] OUT;

always@(IN)

begin

case(IN)

6'b001111: OUT = 8'b11000000; /* Nixietube_0 */

6'b010000: OUT = 8'b11111001; /* Nixietube_1 */

6'b010001: OUT = 8'b10100100; /* Nixietube_2 */

6'b010010: OUT = 8'b10110000; /* Nixietube_3 */

6'b010011: OUT = 8'b10011001; /* Nixietube_4 */

6'b010100: OUT = 8'b10010010; /* Nixietube_5 */

6'b010101: OUT = 8'b10000010; /* Nixietube_6 */

6'b010110: OUT = 8'b11111000; /* Nixietube_7 */

6'b010111: OUT = 8'b10000000; /* Nixietube_8 */

default : OUT = 8'b11111111; /* Nixietube_darkness */

endcase

end

endmodule

/*///////////////////module dec_6to34_Nixietube_0////////*/

module dec_6to34_Nixietube_0(

IN ,

OUT

);

input [6-1:0] IN;

output [8-1:0] OUT;

reg [8-1:0] OUT;

always@(IN)

begin

case(IN)

6'b011000: OUT = 8'b11000000; /* Nixietube_0 */

6'b011001: OUT = 8'b11111001; /* Nixietube_1 */

6'b011010: OUT = 8'b10100100; /* Nixietube_2 */

6'b011011: OUT = 8'b10110000; /* Nixietube_3 */

6'b011100: OUT = 8'b10011001; /* Nixietube_4 */

6'b011101: OUT = 8'b10010010; /* Nixietube_5 */

6'b011110: OUT = 8'b10000010; /* Nixietube_6 */

6'b011111: OUT = 8'b11111000; /* Nixietube_7 */

6'b100000: OUT = 8'b10000000; /* Nixietube_8 */

6'b100001: OUT = 8'b10010000; /* Nixietube_9 */

default : OUT = 8'b11111111; /* Nixietube_darkness */

endcase

end

endmodule