之前做LDPC编码器时,学习了一下异步FIFO的相关知识,主要参考了http://www.cnblogs.com/aslmer/p/6114216.html,并在此基础上根据项目需求,添加了一个读控制模块。因为后面编码模块的需要,因此fifo_in模块要求满足下面功能:

a、存储输入数据

b、当fifo中存储数据的个数达到x时,产生激励信号,并连续输出这x个数据

c、当后面编码模块处于编码过程中时,禁止数据输出

d、x是根据不同编码码率而确定的,因此要时常变化(这个功能时联合其他模块共同实现的)

1、fifo_in.v 是顶层模块,作用是将各个小模块例化联系起来。

输入信号encoding是由后面编码模块产生,表示是否在编码过程中。输入信号in_length输入的数就是个数要求x,由码率选择模块产生。

输出信号start_code是给编码模块的激励信号。输出信号rd_over表示当前一串数据已经输出完毕,主要用于给码率选择模块改变x的值时用。

1 module fifo_in 2 ( 3 //input 4 input wr_clk, 5 input encoding, 6 input wr_rst_n, 7 input wr_ask, 8 input [2:0] wr_data, 9 input rd_clk, 10 input rd_rst_n, 11 input [9:0] in_length, 12 //output 13 output wr_full,//写满 14 output rd_empty,//读空 15 output [2:0] rd_data, 16 output rd_en, 17 output start_code, 18 output rd_over 19 ); 20 wire wr_en; 21 wire [9:0] wr_addr; 22 wire [9:0] rd_addr; 23 wire rd_ask; 24 25 assign wr_en =(wr_ask) && (!wr_full); 26 fifo_in_control fifo_in_control 27 ( 28 //input 29 .wr_clk(wr_clk), 30 .wr_rst_n(wr_rst_n), 31 .wr_ask(wr_ask), 32 //.wr_data(wr_data), 33 .rd_clk(rd_clk), 34 .rd_rst_n(rd_rst_n), 35 .rd_ask(rd_ask), 36 //output 37 .wr_full(wr_full),//写满 38 .rd_empty(rd_empty),//读空 39 .wr_addr(wr_addr), 40 .rd_addr(rd_addr) 41 //output [2:0] rd_data 42 ); 43 fifo_in_rd_control fifo_in_rd_control 44 ( 45 //input 46 .rd_clk(rd_clk), 47 .rd_rst_n(rd_rst_n), 48 .rd_addr(rd_addr), 49 .wr_addr(wr_addr), 50 .in_length(in_length), 51 .encoding(encoding), 52 //output 53 .rd_ask(rd_ask), 54 .start_code_1(start_code), 55 .rd_en_1(rd_en), 56 .rd_over(rd_over) 57 58 ); 59 fifo_in_mem fifo_in_mem ( 60 .data(wr_data), 61 .rdaddress(rd_addr), 62 .rdclock(rd_clk), 63 .wraddress(wr_addr), 64 .wrclock(wr_clk), 65 .wren(wr_en), 66 .q(rd_data) 67 ); 68 endmodule

2、fifo_in_control.v 是异步fifo的主要程序,我从上面那个网址抄来的,网址内的讲解也非常清楚,使用格雷码来避免读写地址的混乱。

1 module fifo_in_control 2 ( 3 //input 4 input wr_clk, 5 input wr_rst_n, 6 input wr_ask, 7 //input [2:0] wr_data, 8 input rd_clk, 9 input rd_rst_n, 10 input rd_ask, 11 //output 12 output reg wr_full,//写满 13 output reg rd_empty,//读空 14 output [9:0] wr_addr, 15 output [9:0] rd_addr 16 //output [2:0] rd_data 17 ); 18 19 reg [10:0] rd_proint_gray;//格雷码形式的写指针 20 reg [10:0] rd_proint_gray_1;//格雷码形式的写指针_延时一个写时钟 21 reg [10:0] rd_proint_gray_2;//格雷码形式的写指针_延时两个写时钟(同步到写时钟的读指针) 22 23 reg [10:0] wr_proint_gray;//格雷码形式的读指针 24 reg [10:0] wr_proint_gray_1;//格雷码形式的读指针_延时一个读时钟 25 reg [10:0] wr_proint_gray_2;//格雷码形式的读指针_延时两个读时钟(同步到读时钟的写指针) 26 27 reg [10:0] wr_proint_bin;//二进制形式的写指针 28 wire [10:0] wr_proint_bin_next; 29 wire [10:0] wr_proint_gray_next; 30 wire wr_full_val; 31 32 reg [10:0] rd_proint_bin;//二进制形式的读指针 33 wire [10:0] rd_proint_bin_next; 34 wire [10:0] rd_proint_gray_next; 35 wire rd_empty_val; 36 //--------------------------------------------------------------------------------- 37 always @(posedge wr_clk or negedge wr_rst_n)//读指针同步到写时钟 38 begin 39 if (!wr_rst_n) 40 begin 41 rd_proint_gray_1 <= 0; 42 rd_proint_gray_2 <= 0; 43 end 44 else 45 begin 46 rd_proint_gray_1 <= rd_proint_gray; 47 rd_proint_gray_2 <= rd_proint_gray_1; 48 end 49 end 50 //-------------------------------------------------------------------------------- 51 always @(posedge rd_clk or negedge rd_rst_n)//写指针同步到读时钟 52 begin 53 if (!rd_rst_n) 54 begin 55 wr_proint_gray_1 <= 0; 56 wr_proint_gray_2 <= 0; 57 end 58 else 59 begin 60 wr_proint_gray_1 <= wr_proint_gray; 61 wr_proint_gray_2 <= wr_proint_gray_1; 62 end 63 end 64 //--------------------------------------------------------------------------------- 65 //写满判决 66 always @(posedge wr_clk or negedge wr_rst_n) 67 begin 68 if (!wr_rst_n) 69 {wr_proint_bin, wr_proint_gray} <= 0; 70 else 71 {wr_proint_bin, wr_proint_gray} <= {wr_proint_bin_next, wr_proint_gray_next}; 72 end 73 74 // Memory write-address pointer (okay to use binary to address memory) 75 assign wr_addr = wr_proint_bin[9:0]; 76 assign wr_proint_bin_next = wr_proint_bin + (wr_ask & ~wr_full); 77 assign wr_proint_gray_next = (wr_proint_bin_next>>1) ^ wr_proint_bin_next; //二进制转为格雷码 78 assign wr_full_val = (wr_proint_gray_next=={~rd_proint_gray_2[10:9],rd_proint_gray_2[8:0]}); //当最高位和次高位不同其余位相同时则写指针超前于读指针一圈,即写满 79 80 always @(posedge wr_clk or negedge wr_rst_n) 81 begin 82 if (!wr_rst_n) 83 wr_full <= 1'b0; 84 else 85 wr_full <= wr_full_val; 86 end 87 //---------------------------------------------------------------------------------- 88 //读空判决 89 always @(posedge rd_clk or negedge rd_rst_n) 90 begin 91 if (!rd_rst_n) 92 begin 93 rd_proint_bin <= 0; 94 rd_proint_gray <= 0; 95 end 96 else 97 begin 98 rd_proint_bin <= rd_proint_bin_next; //直接作为存储实体的地址 99 rd_proint_gray <= rd_proint_gray_next; 100 end 101 end 102 // Memory read-address pointer (okay to use binary to address memory) 103 assign rd_addr = rd_proint_bin[9:0]; //直接作为存储实体的地址 104 assign rd_proint_bin_next = rd_proint_bin + (rd_ask & ~rd_empty);//不空且有读请求的时候读指针加1 105 assign rd_proint_gray_next = (rd_proint_bin_next>>1) ^ rd_proint_bin_next;//将二进制的读指针转为格雷码 106 // FIFO empty when the next rptr == synchronized wptr or on reset 107 assign rd_empty_val = (rd_proint_gray_next == wr_proint_gray_2); //当读指针等于同步后的写指针,则为空。 108 109 always @(posedge rd_clk or negedge rd_rst_n) 110 begin 111 if (!rd_rst_n) 112 rd_empty <= 1'b1; 113 else 114 rd_empty <= rd_empty_val; 115 end 116 117 endmodule

3、fifo_in_rd_control.v 是fifo_in的读控制模块,状态机分为五个状态。数据length记录当前fifo中存储数据的个数,当其大于x(in_length)时,可以进行输出。当fifo中存储数据的个数一直大于x时,两串输出数据的间隔只有几个时钟周期,有时会造成encoding信号还没有生效,新的一串数据已经开始输出,因此设置delay状态,稍等几个周期,确定编码模块是否在工作。

1 module fifo_in_rd_control 2 ( 3 //input 4 input rd_clk, 5 input rd_rst_n, 6 input [9:0] rd_addr, 7 input [9:0] wr_addr, 8 input [9:0] in_length, 9 input encoding, 10 //output 11 output reg rd_ask, 12 output reg start_code_1, 13 output reg rd_en_1, 14 output reg rd_over 15 ); 16 reg [9:0] length;//当前fifo中存储数据的个数 17 reg [4:0] state; 18 reg [9:0] count;//计输出数据的个数 19 // reg [9:0] in_length_next; 20 //reg rd_over; 21 reg start_code; 22 reg rd_en; 23 reg [1:0]i;//延时几个时钟 24 25 parameter hold = 5'b00001; 26 parameter delay = 5'b00010; 27 parameter start = 5'b00100; 28 parameter read = 5'b01000; 29 parameter over = 5'b10000; 30 31 32 always @(posedge rd_clk or negedge rd_rst_n) 33 begin 34 start_code_1 <= start_code; 35 rd_en_1 <= rd_en; 36 end 37 always @(posedge rd_clk or negedge rd_rst_n) 38 begin 39 if(!rd_rst_n) 40 begin 41 state <= hold; 42 rd_ask <= 0; 43 start_code <= 0; 44 rd_en <= 0; 45 rd_over <= 0; 46 end 47 else if(encoding) 48 begin 49 state <= hold; 50 rd_ask <= 0; 51 start_code <= 0; 52 rd_en <= 0; 53 rd_over <= 0; 54 end 55 else 56 case(state) 57 hold: 58 if(in_length <= length) 59 begin 60 state <= delay; 61 rd_over <= 0; 62 i <= 2'b00; 63 end 64 else 65 begin 66 state <= hold; 67 rd_over <= 0; 68 end 69 delay: 70 if(i >= 2) 71 state <= start; 72 else 73 i <= i + 1; 74 start: 75 begin 76 state <= read; 77 start_code <= 1; 78 end 79 read: 80 if(count == in_length-1) 81 begin 82 state <= over; 83 rd_en <= 0; 84 rd_ask <= 0; 85 end 86 else 87 begin 88 state <= read; 89 rd_en <= 1; 90 rd_ask <= 1; 91 start_code <= 0; 92 end 93 over: 94 begin 95 state <= hold; 96 rd_over <= 1; 97 end 98 default:state <= hold; 99 endcase 100 end 101 102 always @(posedge rd_clk or negedge rd_rst_n) 103 begin 104 if(!rd_rst_n) 105 length <= 0; 106 else if(wr_addr < rd_addr) 107 length <= (10'd1023 ^ rd_addr) + wr_addr + 10'd1; 108 else 109 length <= wr_addr - rd_addr; 110 end 111 112 always @(posedge rd_clk or negedge rd_rst_n) 113 begin 114 if(!rd_rst_n) 115 count <= 10'd0; 116 else if(rd_en) 117 count <= count + 10'd1; 118 else if(start_code) 119 count <= 10'd0; 120 else 121 count <= count; 122 end 123 124 // always @(posedge rd_clk or negedge rd_rst_n) 125 // begin 126 // if(!rd_rst_n) 127 // in_length_next <= in_length; 128 // else if(rd_over) 129 // in_length_next <= in_length; 130 // else 131 // in_length_next <= in_length_next; 132 // end 133 134 endmodule

4、fifo_in_mem.v 生成存储实体,FIFO 的本质是RAM,因此在设计存储实体的时候有两种方法:用数组存储数据或者调用RAM的IP核。我是采用IP核的方法。

1 // megafunction wizard: %RAM: 2-PORT% 2 // GENERATION: STANDARD 3 // VERSION: WM1.0 4 // MODULE: altsyncram 5 6 // ============================================================ 7 // File Name: fifo_in_mem.v 8 // Megafunction Name(s): 9 // altsyncram 10 // 11 // Simulation Library Files(s): 12 // altera_mf 13 // ============================================================ 14 // ************************************************************ 15 // THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE! 16 // 17 // 17.1.0 Build 590 10/25/2017 SJ Standard Edition 18 // ************************************************************ 19 20 21 //Copyright (C) 2017 Intel Corporation. All rights reserved. 22 //Your use of Intel Corporation's design tools, logic functions 23 //and other software and tools, and its AMPP partner logic 24 //functions, and any output files from any of the foregoing 25 //(including device programming or simulation files), and any 26 //associated documentation or information are expressly subject 27 //to the terms and conditions of the Intel Program License 28 //Subscription Agreement, the Intel Quartus Prime License Agreement, 29 //the Intel FPGA IP License Agreement, or other applicable license 30 //agreement, including, without limitation, that your use is for 31 //the sole purpose of programming logic devices manufactured by 32 //Intel and sold by Intel or its authorized distributors. Please 33 //refer to the applicable agreement for further details. 34 35 36 // synopsys translate_off 37 `timescale 1 ps / 1 ps 38 // synopsys translate_on 39 module fifo_in_mem ( 40 data, 41 rdaddress, 42 rdclock, 43 wraddress, 44 wrclock, 45 wren, 46 q); 47 48 input [2:0] data; 49 input [9:0] rdaddress; 50 input rdclock; 51 input [9:0] wraddress; 52 input wrclock; 53 input wren; 54 output [2:0] q; 55 `ifndef ALTERA_RESERVED_QIS 56 // synopsys translate_off 57 `endif 58 tri1 wrclock; 59 tri0 wren; 60 `ifndef ALTERA_RESERVED_QIS 61 // synopsys translate_on 62 `endif 63 64 wire [2:0] sub_wire0; 65 wire [2:0] q = sub_wire0[2:0]; 66 67 altsyncram altsyncram_component ( 68 .address_a (wraddress), 69 .address_b (rdaddress), 70 .clock0 (wrclock), 71 .clock1 (rdclock), 72 .data_a (data), 73 .wren_a (wren), 74 .q_b (sub_wire0), 75 .aclr0 (1'b0), 76 .aclr1 (1'b0), 77 .addressstall_a (1'b0), 78 .addressstall_b (1'b0), 79 .byteena_a (1'b1), 80 .byteena_b (1'b1), 81 .clocken0 (1'b1), 82 .clocken1 (1'b1), 83 .clocken2 (1'b1), 84 .clocken3 (1'b1), 85 .data_b ({3{1'b1}}), 86 .eccstatus (), 87 .q_a (), 88 .rden_a (1'b1), 89 .rden_b (1'b1), 90 .wren_b (1'b0)); 91 defparam 92 altsyncram_component.address_aclr_b = "NONE", 93 altsyncram_component.address_reg_b = "CLOCK1", 94 altsyncram_component.clock_enable_input_a = "BYPASS", 95 altsyncram_component.clock_enable_input_b = "BYPASS", 96 altsyncram_component.clock_enable_output_b = "BYPASS", 97 altsyncram_component.intended_device_family = "Cyclone V", 98 altsyncram_component.lpm_type = "altsyncram", 99 altsyncram_component.numwords_a = 1024, 100 altsyncram_component.numwords_b = 1024, 101 altsyncram_component.operation_mode = "DUAL_PORT", 102 altsyncram_component.outdata_aclr_b = "NONE", 103 altsyncram_component.outdata_reg_b = "CLOCK1", 104 altsyncram_component.power_up_uninitialized = "FALSE", 105 altsyncram_component.widthad_a = 10, 106 altsyncram_component.widthad_b = 10, 107 altsyncram_component.width_a = 3, 108 altsyncram_component.width_b = 3, 109 altsyncram_component.width_byteena_a = 1; 110 111 112 endmodule 113 114 // ============================================================ 115 // CNX file retrieval info 116 // ============================================================ 117 // Retrieval info: PRIVATE: ADDRESSSTALL_A NUMERIC "0" 118 // Retrieval info: PRIVATE: ADDRESSSTALL_B NUMERIC "0" 119 // Retrieval info: PRIVATE: BYTEENA_ACLR_A NUMERIC "0" 120 // Retrieval info: PRIVATE: BYTEENA_ACLR_B NUMERIC "0" 121 // Retrieval info: PRIVATE: BYTE_ENABLE_A NUMERIC "0" 122 // Retrieval info: PRIVATE: BYTE_ENABLE_B NUMERIC "0" 123 // Retrieval info: PRIVATE: BYTE_SIZE NUMERIC "8" 124 // Retrieval info: PRIVATE: BlankMemory NUMERIC "1" 125 // Retrieval info: PRIVATE: CLOCK_ENABLE_INPUT_A NUMERIC "0" 126 // Retrieval info: PRIVATE: CLOCK_ENABLE_INPUT_B NUMERIC "0" 127 // Retrieval info: PRIVATE: CLOCK_ENABLE_OUTPUT_A NUMERIC "0" 128 // Retrieval info: PRIVATE: CLOCK_ENABLE_OUTPUT_B NUMERIC "0" 129 // Retrieval info: PRIVATE: CLRdata NUMERIC "0" 130 // Retrieval info: PRIVATE: CLRq NUMERIC "0" 131 // Retrieval info: PRIVATE: CLRrdaddress NUMERIC "0" 132 // Retrieval info: PRIVATE: CLRrren NUMERIC "0" 133 // Retrieval info: PRIVATE: CLRwraddress NUMERIC "0" 134 // Retrieval info: PRIVATE: CLRwren NUMERIC "0" 135 // Retrieval info: PRIVATE: Clock NUMERIC "1" 136 // Retrieval info: PRIVATE: Clock_A NUMERIC "0" 137 // Retrieval info: PRIVATE: Clock_B NUMERIC "0" 138 // Retrieval info: PRIVATE: IMPLEMENT_IN_LES NUMERIC "0" 139 // Retrieval info: PRIVATE: INDATA_ACLR_B NUMERIC "0" 140 // Retrieval info: PRIVATE: INDATA_REG_B NUMERIC "0" 141 // Retrieval info: PRIVATE: INIT_FILE_LAYOUT STRING "PORT_B" 142 // Retrieval info: PRIVATE: INIT_TO_SIM_X NUMERIC "0" 143 // Retrieval info: PRIVATE: INTENDED_DEVICE_FAMILY STRING "Cyclone V" 144 // Retrieval info: PRIVATE: JTAG_ENABLED NUMERIC "0" 145 // Retrieval info: PRIVATE: JTAG_ID STRING "NONE" 146 // Retrieval info: PRIVATE: MAXIMUM_DEPTH NUMERIC "0" 147 // Retrieval info: PRIVATE: MEMSIZE NUMERIC "3072" 148 // Retrieval info: PRIVATE: MEM_IN_BITS NUMERIC "0" 149 // Retrieval info: PRIVATE: MIFfilename STRING "" 150 // Retrieval info: PRIVATE: OPERATION_MODE NUMERIC "2" 151 // Retrieval info: PRIVATE: OUTDATA_ACLR_B NUMERIC "0" 152 // Retrieval info: PRIVATE: OUTDATA_REG_B NUMERIC "1" 153 // Retrieval info: PRIVATE: RAM_BLOCK_TYPE NUMERIC "0" 154 // Retrieval info: PRIVATE: READ_DURING_WRITE_MODE_MIXED_PORTS NUMERIC "2" 155 // Retrieval info: PRIVATE: READ_DURING_WRITE_MODE_PORT_A NUMERIC "3" 156 // Retrieval info: PRIVATE: READ_DURING_WRITE_MODE_PORT_B NUMERIC "3" 157 // Retrieval info: PRIVATE: REGdata NUMERIC "1" 158 // Retrieval info: PRIVATE: REGq NUMERIC "0" 159 // Retrieval info: PRIVATE: REGrdaddress NUMERIC "1" 160 // Retrieval info: PRIVATE: REGrren NUMERIC "1" 161 // Retrieval info: PRIVATE: REGwraddress NUMERIC "1" 162 // Retrieval info: PRIVATE: REGwren NUMERIC "1" 163 // Retrieval info: PRIVATE: SYNTH_WRAPPER_GEN_POSTFIX STRING "0" 164 // Retrieval info: PRIVATE: USE_DIFF_CLKEN NUMERIC "0" 165 // Retrieval info: PRIVATE: UseDPRAM NUMERIC "1" 166 // Retrieval info: PRIVATE: VarWidth NUMERIC "0" 167 // Retrieval info: PRIVATE: WIDTH_READ_A NUMERIC "3" 168 // Retrieval info: PRIVATE: WIDTH_READ_B NUMERIC "3" 169 // Retrieval info: PRIVATE: WIDTH_WRITE_A NUMERIC "3" 170 // Retrieval info: PRIVATE: WIDTH_WRITE_B NUMERIC "3" 171 // Retrieval info: PRIVATE: WRADDR_ACLR_B NUMERIC "0" 172 // Retrieval info: PRIVATE: WRADDR_REG_B NUMERIC "0" 173 // Retrieval info: PRIVATE: WRCTRL_ACLR_B NUMERIC "0" 174 // Retrieval info: PRIVATE: enable NUMERIC "0" 175 // Retrieval info: PRIVATE: rden NUMERIC "0" 176 // Retrieval info: LIBRARY: altera_mf altera_mf.altera_mf_components.all 177 // Retrieval info: CONSTANT: ADDRESS_ACLR_B STRING "NONE" 178 // Retrieval info: CONSTANT: ADDRESS_REG_B STRING "CLOCK1" 179 // Retrieval info: CONSTANT: CLOCK_ENABLE_INPUT_A STRING "BYPASS" 180 // Retrieval info: CONSTANT: CLOCK_ENABLE_INPUT_B STRING "BYPASS" 181 // Retrieval info: CONSTANT: CLOCK_ENABLE_OUTPUT_B STRING "BYPASS" 182 // Retrieval info: CONSTANT: INTENDED_DEVICE_FAMILY STRING "Cyclone V" 183 // Retrieval info: CONSTANT: LPM_TYPE STRING "altsyncram" 184 // Retrieval info: CONSTANT: NUMWORDS_A NUMERIC "1024" 185 // Retrieval info: CONSTANT: NUMWORDS_B NUMERIC "1024" 186 // Retrieval info: CONSTANT: OPERATION_MODE STRING "DUAL_PORT" 187 // Retrieval info: CONSTANT: OUTDATA_ACLR_B STRING "NONE" 188 // Retrieval info: CONSTANT: OUTDATA_REG_B STRING "CLOCK1" 189 // Retrieval info: CONSTANT: POWER_UP_UNINITIALIZED STRING "FALSE" 190 // Retrieval info: CONSTANT: WIDTHAD_A NUMERIC "10" 191 // Retrieval info: CONSTANT: WIDTHAD_B NUMERIC "10" 192 // Retrieval info: CONSTANT: WIDTH_A NUMERIC "3" 193 // Retrieval info: CONSTANT: WIDTH_B NUMERIC "3" 194 // Retrieval info: CONSTANT: WIDTH_BYTEENA_A NUMERIC "1" 195 // Retrieval info: USED_PORT: data 0 0 3 0 INPUT NODEFVAL "data[2..0]" 196 // Retrieval info: USED_PORT: q 0 0 3 0 OUTPUT NODEFVAL "q[2..0]" 197 // Retrieval info: USED_PORT: rdaddress 0 0 10 0 INPUT NODEFVAL "rdaddress[9..0]" 198 // Retrieval info: USED_PORT: rdclock 0 0 0 0 INPUT NODEFVAL "rdclock" 199 // Retrieval info: USED_PORT: wraddress 0 0 10 0 INPUT NODEFVAL "wraddress[9..0]" 200 // Retrieval info: USED_PORT: wrclock 0 0 0 0 INPUT VCC "wrclock" 201 // Retrieval info: USED_PORT: wren 0 0 0 0 INPUT GND "wren" 202 // Retrieval info: CONNECT: @address_a 0 0 10 0 wraddress 0 0 10 0 203 // Retrieval info: CONNECT: @address_b 0 0 10 0 rdaddress 0 0 10 0 204 // Retrieval info: CONNECT: @clock0 0 0 0 0 wrclock 0 0 0 0 205 // Retrieval info: CONNECT: @clock1 0 0 0 0 rdclock 0 0 0 0 206 // Retrieval info: CONNECT: @data_a 0 0 3 0 data 0 0 3 0 207 // Retrieval info: CONNECT: @wren_a 0 0 0 0 wren 0 0 0 0 208 // Retrieval info: CONNECT: q 0 0 3 0 @q_b 0 0 3 0 209 // Retrieval info: GEN_FILE: TYPE_NORMAL fifo_in_mem.v TRUE 210 // Retrieval info: GEN_FILE: TYPE_NORMAL fifo_in_mem.inc FALSE 211 // Retrieval info: GEN_FILE: TYPE_NORMAL fifo_in_mem.cmp FALSE 212 // Retrieval info: GEN_FILE: TYPE_NORMAL fifo_in_mem.bsf FALSE 213 // Retrieval info: GEN_FILE: TYPE_NORMAL fifo_in_mem_inst.v FALSE 214 // Retrieval info: GEN_FILE: TYPE_NORMAL fifo_in_mem_bb.v FALSE 215 // Retrieval info: LIB_FILE: altera_mf

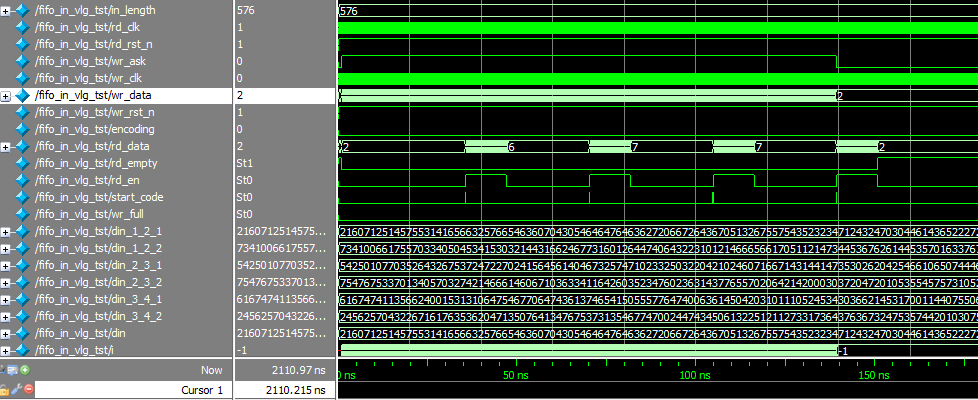

5、fifo_in_vlg_tst.vt 测试文件

1 `timescale 1 ps/ 1 ps 2 module fifo_in_vlg_tst(); 3 4 // test vector input registers 5 reg [9:0] in_length; 6 reg rd_clk; 7 reg rd_rst_n; 8 reg wr_ask; 9 reg wr_clk; 10 reg [2:0] wr_data; 11 reg wr_rst_n; 12 reg encoding; 13 // wires 14 wire [2:0] rd_data; 15 wire rd_empty; 16 wire rd_en; 17 wire start_code; 18 wire wr_full; 19 20 //malv 1/2 21 reg [575:0] din_1_2_1; 22 reg [575:0] din_1_2_2; 23 //malv 2/3 24 reg [1151:0] din_2_3_1; 25 reg [1151:0] din_2_3_2; 26 //malv 3/4 27 reg [1727:0] din_3_4_1; 28 reg [1727:0] din_3_4_2; 29 30 reg [6911:0] din; 31 32 integer i; 33 // assign statements (if any) 34 fifo_in i1 ( 35 // port map - connection between master ports and signals/registers 36 .in_length(in_length), 37 .rd_clk(rd_clk), 38 .rd_data(rd_data), 39 .rd_empty(rd_empty), 40 .rd_en(rd_en), 41 .rd_rst_n(rd_rst_n), 42 .encoding(encoding), 43 .start_code(start_code), 44 .wr_ask(wr_ask), 45 .wr_clk(wr_clk), 46 .wr_data(wr_data), 47 .wr_full(wr_full), 48 .wr_rst_n(wr_rst_n) 49 ); 50 initial 51 begin 52 din_1_2_1= 576'O 216071251457553141656632576654636070430546464764636272066726436705132675575435232347124324703044614365222721255502724213676021274561705551344656470423514271071110356653574261134400253673045231; 53 din_1_2_2= 576'O 734100661755703340504534153032144316624677316012644740643223101214666566170511214734453676261445357016337671034473372575240732732041042256277164745532035241257613727416542012571673163075070075; 54 55 din = 6912'o 216071251457553141656632576654636070430546464764636272066726436705132675575435232347124324703044614365222721255502724213676021274561705551344656470423514271071110356653574261134400253673045231542501077035264326753724722702415645614046732574710233250322042102460716671431441473530262042546610650744466305262611705533733122712351603065154647323273235316421143506516144106630415427670155643465425347677600020324722621463553370234733536333100716567137573041454431304700710617024455316156070660472646602537542273606077401560672521652430032221351533114247557647027635331303274633674616747411356624001531310647546770647436137465415055577647400636145042031011105245343036621453170011440755067766413107222350646230152707457233660120421175370554142117010307102307220204650067406225005445562543062450143765000675150052554515760225462106134153160214030062473563507126363205334026511003554051101112212754110754214712305373413166252464223324533002257731665505310611574517450650424331207571764326106555336266645730652715431031526541727120510525350765634442131670406707056477511100472377576251254346444405727273311256506760355125341166701031700462121475030437637137754734100661755703340504534153032144316624677316012644740643223101214666566170511214734453676261445357016337671034473372575240732732041042256277164745532035241257613727416542012571673163075070075245625704322671617635362047135076413476753731354677470024474345061322512112733173643763673247535744201030750013105263300041667311462357154373154267711040374213703605721574716231645607365613476744607305114223334110261556622426642513347671406467730411205542647724246516035625711122704161472013217573704617664621246236471651334606623455633746244704407736142361232671153775635747535713735775004475542740540721021502273646076032514443043033465601376320541316270654550702170455606451457300565274701676216621266442563332577525101140657357427027220712734450406261470005406400160110655754767533701340570327421466614606710363341164260352347602363143776557020642142000303720472010535545757310525545433730156716434355206361077760474607743250274332774733116546441410541354110331500770361665037535147625270260465132341751476532412776714575356407040361753126054573276304142254615065707442061247471350536327530550073001734307224325742130741406344520305075741267260435203513562; 56 57 din_2_3_1= 1152'O 542501077035264326753724722702415645614046732574710233250322042102460716671431441473530262042546610650744466305262611705533733122712351603065154647323273235316421143506516144106630415427670155643465425347677600020324722621463553370234733536333100716567137573041454431304700710617024455316156070660472646602537542273606077401560672521652430032221351533114247557647027635331303274633674; 58 din_2_3_2= 1152'O 754767533701340570327421466614606710363341164260352347602363143776557020642142000303720472010535545757310525545433730156716434355206361077760474607743250274332774733116546441410541354110331500770361665037535147625270260465132341751476532412776714575356407040361753126054573276304142254615065707442061247471350536327530550073001734307224325742130741406344520305075741267260435203513562; 59 60 din_3_4_1= 1728'O 616747411356624001531310647546770647436137465415055577647400636145042031011105245343036621453170011440755067766413107222350646230152707457233660120421175370554142117010307102307220204650067406225005445562543062450143765000675150052554515760225462106134153160214030062473563507126363205334026511003554051101112212754110754214712305373413166252464223324533002257731665505310611574517450650424331207571764326106555336266645730652715431031526541727120510525350765634442131670406707056477511100472377576251254346444405727273311256506760355125341166701031700462121475030437637137754; 61 din_3_4_2= 1728'O 245625704322671617635362047135076413476753731354677470024474345061322512112733173643763673247535744201030750013105263300041667311462357154373154267711040374213703605721574716231645607365613476744607305114223334110261556622426642513347671406467730411205542647724246516035625711122704161472013217573704617664621246236471651334606623455633746244704407736142361232671153775635747535713735775004475542740540721021502273646076032514443043033465601376320541316270654550702170455606451457300565274701676216621266442563332577525101140657357427027220712734450406261470005406400160110655; 62 63 in_length = 10'd576; 64 encoding = 0; 65 rd_clk = 0; 66 wr_clk = 0; 67 rd_rst_n = 1; 68 wr_rst_n = 1; 69 wr_ask = 0; 70 wr_data = 3'd0; 71 #50 72 rd_rst_n = 0; 73 wr_rst_n = 0; 74 #50 75 rd_rst_n = 1; 76 wr_rst_n = 1; 77 // #2000 78 // in_length = 10'd384; 79 end 80 // initial 81 // begin 82 // #63950 83 // encoding = 1; 84 // #5000 85 // encoding = 0; 86 // end 87 // initial 88 // begin 89 // #30000 90 // in_length = 10'd576; 91 // end 92 // initial 93 // begin 94 // #60000 95 // in_length = 10'd192; 96 // end 97 // initial 98 // begin 99 // #83000 100 // in_length = 10'd576; 101 // end 102 103 always #10 rd_clk <= ~rd_clk; 104 always #30 wr_clk <= ~wr_clk; 105 106 initial 107 begin 108 #1000 109 for(i = 6911; i >=2; i = i-3) 110 begin 111 wr_data[2] <= din[i]; 112 wr_data[1] <= din[i-1]; 113 wr_data[0] <= din[i-2]; 114 #60; 115 end 116 end 117 118 always @ (i) 119 begin 120 if (i < 2) 121 wr_ask = 0; 122 else 123 wr_ask = 1; 124 end 125 126 endmodule

仿真结果