1.异步FIFO设计

在看本文之前,需要读者了解异步FIFO的原理及设计,具体可参考博客: 异步FIFO的Verilg实现方法_verilog实现异步fifo_孤独的单刀的博客-CSDN博客

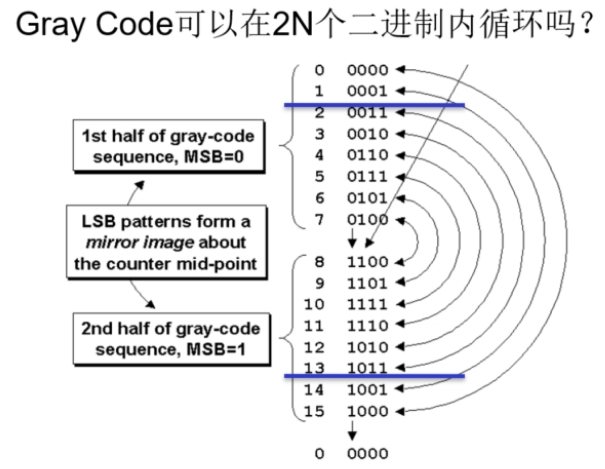

2.偶数格雷码环回

通常情况下,设计的异步FIFO的深度是2的N次方,但事实上,选择这个2^N的原因也是因为格雷码这么取的时候,最大值+1回到最小值时,跳变还是只有1bit。

事实上格雷码可以取2N个进行环回,例如取格雷码个数为12,在2^4=16的基础上,掐头去尾,取中间的12个格雷码,这样从0011到最大值1011中间任意两个相邻数之间只有1bit位的跳变。

那么我们就可以得出一个结论:

任意偶数个数格雷码,都可以实现相邻数字跳变仅有1bit发生变化。

3.任意深度异步FIFO

异步FIFO的关键就在于读写指针跨时钟域传输时,每次跳变仅能有1bit变化,这样无论是变化前还是变化后的读写指针被同步到另一个时钟域,都不会发生“读空继续读”、“写满继续写”这样的逻辑错误。

3.1偶数深度的FIFO

对于偶数深度的FIFO,譬如FIFO深度为4,无论FIFO深度为什么,我们都会对地址进行扩展1bit,来作为标志位,用于产生空满信号。因此FIFO深度为4时,我们的读写指针取值范围为:

{0_110,0_111,0_101,0_100,1_100,1_101,1_111,1_110}

可以看到,任意两个相邻的数字仅有1bit发生跳变,取格雷码回环就按照:在2^4=16的基础上,掐头去尾,取中间的8个格雷码。

3.2奇数深度的FIFO

对于奇数深度的FIFO,譬如FIFO深度为3,无论FIFO深度为什么,我们都会对地址进行扩展1bit,来作为标志位,用于产生空满信号。因此FIFO深度为3时,我们的读写指针取值范围为:

{0_111,0_101,0_100,1_100,1_101,1_111}

可以看到,任意两个相邻的数字仅有1bit发生跳变,取格雷码回环就按照:在2^4=16的基础上,掐头去尾,取中间的6个格雷码。

也就是说,无论FIFO深度是奇数还是偶数,我们都会对读写指针扩1bit标志位,使得扩充后他们的深度一定是偶数。这样我们就可以用第二节提到的偶数格雷码环回特性:任意偶数个数格雷码,都可以实现相邻数字跳变仅有1bit发生变化。让读写指针跨时钟域传输时,相邻数字仅有1bit发生变化,就不会出现FIFO读写错误,所以FIFO深度可以是任意值。