文章目录

0、引言

本篇文章用于总结之前学习的time quest,并且我已经能够利用公式,计算出slack了,并能够根据setup slack来更改优化代码了。时光由隔了1个月,时序分析的路没有终点,本篇文章是对之前两篇的总结,然后time quest就暂告一段落了,以后随着学习IO约束等深入学习再来继续补充。目前的两篇已经能够解决大多数问题了。

https://blog.csdn.net/ciscomonkey/article/details/88046646

1、第一天

1、chip planner

只有在filter(布线)编译后,chip pannner里面才会完成布线。

其中黑色区域代表不可用,蓝色区域时刻用的,且蓝色越深说明使用的逻辑量越大,而一个长的方框就代表一个LAB,一个LAB里面有存在着16个LE,如下图,其中红色代表使用了寄存器,浅蓝色代表使用了LUT,而LUT正是组合逻辑,所有的组合逻辑都是靠LUT(查找表)来实现的。

使用专门的时钟管脚,而不自己分频产生时钟,FPGA使用PLL来产生全局时钟、或者专门的时钟管脚,保证了到达每个LAB的路径几乎都是一样的,减小了clock skew。

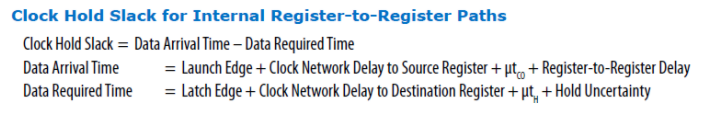

2、计算题

从fpga时钟管脚到达PLL的内部走线延时=2ns

从PLL输出时钟端到REG1的延时=2.5ns

从PLL输出时钟端到REG2的延时=1.5ns

数据到数据路径=3ns

Tcycle=8ns

Tsetup=0.5ns

Thold=0.5ns

求建立时间余量Tsslack?保持时间余量Thold

Tslack=1.5ns+8-0.5-(2.5+3)=9-5.5=3.5ns

Thold=2.5+8+3-(1.5+8+0.5)=3.5ns

以上计算只要理解了必备公式和示意图是非常简单的。