一、绪论

1 计算机硬件

(1)CPU

专用寄存器

程序计数器 保存了将要取出的下一条指令的内存地址

堆栈指针 指向内存中当前栈的顶端

程序状态字PSW 这个寄存器包含了条件码位、CPU优先级、模式(用户态或内核态),以及其他各种控制位。用户程序通常读入整个PSW,但只对其中少量字段写入,在系统调用和IO中,PSW的作用很重要

流水线与超标量CPU

在多数的流水线设计中,一旦一条指令被取进流水线中,它就必须被执行完毕,即便前一条取出的指令是条件转移。

在超标量设计中,通常有多个执行单元。两个或更多的指令被同时指出、解码并装入暂存缓冲区,直至它们执行完毕。只要有一个执行单元空闲,就检查保持缓冲区是否还有可处理的指令,如果有,就把指令从缓冲区中移出并执行。存在一个问题:程序的指令经常不按顺序执行。多数情况下,硬件负责保证这种运算的结果与顺序执行指令时的结果相同。

(2)存储器

| 典型访问时间 | 典型容量 | |

|---|---|---|

| 1ns | 寄存器 | <1KB |

| 2ns | 高速缓存 | 4MB |

| 10ns | 主存 | |

| 10ms | 磁盘 |

(3)磁盘

磁道 盘片上的圆环

柱面 不同盘片上的磁道

扇区 磁道上的不同区间,典型值为512字节

(4)IO设备

设备受设备控制器控制,而操作系统通过驱动程序控制设备控制器,驱动程序一般在内核态运行,需要将驱动程序装入操作系统中。有三个途径:

1 将内核与设备驱动程序重新连接,重新启动 如UNIX

2 在一个操作系统文件中设置一个入口,该文件通知操作系统需要一个设备驱动程序,重启系统。系统启动时即可装在设备驱动程序。如Windows

3 热插拔 如USB\

实现输入和输出的三种方式:

1 忙等待 需要占据CPU,CPU一直轮询设备知道对应的IO操作完成

2 中断的方式

关于中断 https://www.cnblogs.com/funeral/archive/2013/03/06/2945485.html

https://blog.csdn.net/tigerjibo/article/details/6067258

3 DMA

DMA直接内存存取原理是指外部设不通过CPU而直接与系统内存交换数据的接口技术。采用中断传送有它的缺点,对于一个高速I/O设备,以及批量交换数据的情况,只能采用DMA方式,才能解决效率和速度问题。DMA在外设与内存间直接进行数据交换,而不通过CPU,这样数据传送的速度就取决于存储器和外设的工作速度

通常系统的总线是由CPU管理的。在DMA方式时,就希望CPU把这些总线让出来,即CPU连到这些总线上的线处于第三态–高阻状态,而由DMA控制器接管,控制传送的字节数,判断DMA是否结束,以及发出DMA结束信号。DMA控制器必须有以下功能:

1. 能向CPU发出系统保持(HOLD)信号,提出总线接管请求;

2. 当CPU发出允许接管信号后,负责对总线的控制,进入DMA方式;

3. 能对存储器寻址及能修改地址指针,实现对内存的读写操作;

4. 能决定本次DMA传送的字节数,判断DMA传送是否结束

5. 发出DMA结束信号,使CPU恢复正常工作状态。

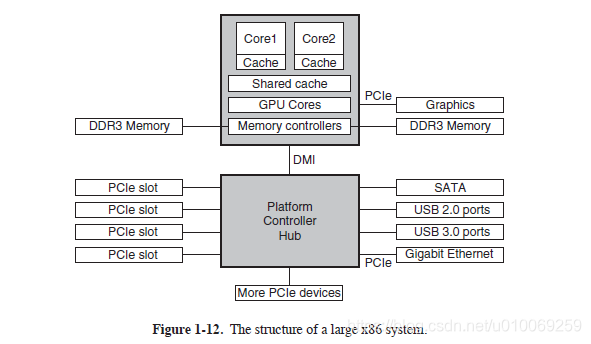

(5)总线

高速缓存、内存、PCIe、PCI、USB、SCSI、SATA和DMI

p18

PCI总线使用并行传输,是共享总线架构,多个设备使用一条总线,由仲裁器决定那个设备可以使用总线;而PCIe使用串行传输,使用分离的端到端的链路

2 操作系统概念

(1)进程

进程基本上是容纳运行一个程序所需要的所有信息的容器

(2) 地址空间

(3)文件

在读写文件之前,首先要打开文件,检查其访问权限,若权限许可,系统将返回一个小整数,成为文件描述符,供后续操作使用。若禁止访问,系统返回一个错误码

特殊文件 提供特殊文件是为了是IO设备看起来像文件一般,这样就使得操作IO设备跟操作文件一样,使用相同的系统调用。有两类特殊文件:块特殊文件,如磁盘等,字符特殊文件,如打印机、其他接收或输出字符流的设备。按照惯例,特殊文件保存在/dev目录中

3 系统调用

异常控制流是机制,中断是技术

陷阱通常由处理器正在执行的现行指令引起,而中断则是由与现行指令无关的中断源引起的。陷阱处理程序提供的服务为当前进程所用,而中断处理程序提供的服务则不是为了当前进程的。中断是由硬件引起的,而异常是由软件引起的;中断是异步的,而异常是同步的。

中断 https://www.cnblogs.com/funeral/archive/2013/03/06/2945485.html

- 外部中断

外部中断是由外部设备引发的中断,而引发中断的设备被称为中断源,中断源大致可以分为以下几种

1 定时器、计时器

2 键盘

3 内部实时时钟

4 通用接口

5 PS/2鼠标

6 协处理器

7 IDE/SATE硬盘

8 串口

9 并口

10 软盘

…

- 可屏蔽中断

- 不可屏蔽中断

外部设备通过"可编程中断控制器(Programmable Interrupt Controller,PIC)"向CPU报告的中断,大致流程如下:

1 外部设备通过中断请求线(IRQ)连接到一个"中断控制器"上

2 当一个外部设备需要发出中断时,会驱动对应的中断请求线进入有信号状态

3 中断控制器检测这个中断是否被屏蔽了(CPU的IF位被置1,则不屏蔽任何外部中断;CPU的IF位被置0,则屏蔽所有外部中断),如果没有被屏蔽就驱动CPU的"INTR中断请求线"进入信号状态

4 CPU随后就能检测到这个中断了(在每次CPU周期的下降沿检测一次中断)

5 如果该中断被屏蔽(CPU中的中断屏蔽寄存器被选中),中断控制器中的寄存器中的某一位位将记录这一请求,等到中断被开启时再驱动CPU的"INTR中断请求线"进入信号状态

6 之后CPU通过"中断应答"从中断控制器的数据线上读取中断号,并通过中断号获取中断向量

7 如果多个设备(外设中断源)在同一时刻通过不同的中断请求线发出中断请求,中断控制器也会将这些请求记录在不同的位中

8 如果这些中断都没有被屏蔽,则中断控制器根据优先级,依次执行优先级高的中断(IRQn的数字n越小优先级越大)

- 内部中断

和外部中断相对的就是内部中断。从CPU的角度看,外部中断是一个异步事件,它可能在任何时候发送,而内部中断是一个同步事件,它是执行某条指令时产生的。

内部中断可以大致分为以下几种- 异常(faults)

CPU在指令执行时产生的,异常是可以修复的。当异常发生时,压入堆栈的是产生异常的"那条指令",当CPU执行异常处理程序结束后,将"重新执行那一条指令"。

1.1) 缺页异常: 14: #PF

1.2) 保护错误(内存或其他保护检查): 13: #GP

1.3) 堆栈段错误(堆栈操作或者加载SS): 12: #SS

1.4) 段不存在(加载段寄存器后访问段): 11: #NP

1.5) 除法错误(DIV/IDIV指令): 0: #DE

1.6) 越界: 5: #BR

1.7) 无效操作码(无效操作指令): 6: #UD

1.8) 对齐校验(内存访问): 17: #AC - 陷阱(traps)

在CPU执行陷阱指令后,立刻通过中断描述表执行预定的陷阱处理例程。陷阱处理例程执行结束后,将返回陷阱指令的"下一条指令"继续执行。

2.1) 系统调用(system call)

系统调用是一种软中断,软中断是一条CPU指令,用以自陷一个中断。由于软中断指令通常要运行一个切换CPU至内核态(Kernel Mode/Ring 0)的子例程,它常被用作实现系统调用(System call)

这是最常使用到的中断,我们在编程中使用到的API最终都会通过系统调用这种内部中断来进行ring3到ring0的切换

2.2) 单步异常(调试异常): 1: #DB

用于单步执行、内存断点

2.3) INT3(断点异常): 3: #BP

2.4) 溢出(指令INT0): 4: #OF - 终止(aborts)

3.1) 双重错误(所有能产生异常、NMI、或者INTR的指令): 8: #DF\

- 异常(faults)

疑问点

计算机使用陷阱而不是一条指令来执行系统调用??

每个线程在操作系统看来就像是单个的CPU??

补充知识点

- L1、L2、L3缓存 CPU与内存间的缓冲,最靠近CPU的是L1缓存,命中率80%

- UNIX进程将其存储空间划分为三段:正文段、数据段、堆栈段;数据向上增长而堆栈向下增长

| 进程的三段 |

|---|

| 堆栈 |

| 空闲区 |

| 数据 |

| 正文 |

- UNIX目录 目录就是包含了(i-编号,ASCII名称)对的集合的文件

- inode 节点 https://blog.csdn.net/Jijiahao95/article/details/53398475