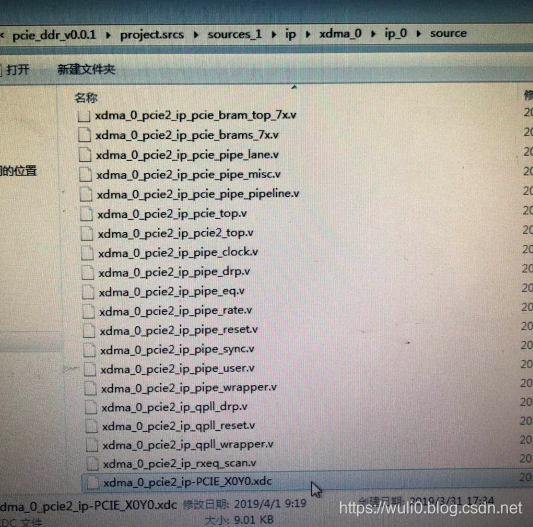

另外需要注意的是在PCIE XDMA编译的时候有出现管脚约束错误的问题,在工程的管脚约束文件里面怎么修改发现都约束不对。这个时候只需要修改下面图片中的文件即可

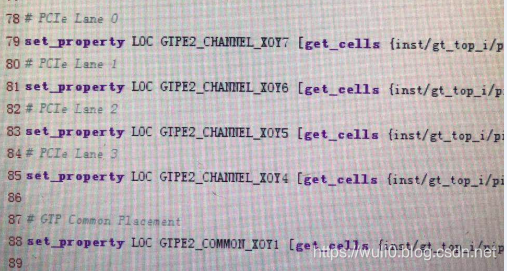

将xdma_0_pcie2ip-PCIE_XOYO中的第79到第85行

#PCIe Line0

set_property LOC GTPE2_CHANNEL_XOY7 [get_cells {inst/gt_top........}]

#PCIe Line1

set_property LOC GTPE2_CHANNEL_XOY6 [get_cells {inst/gt_top........}]

#PCIe Line2

set_property LOC GTPE2_CHANNEL_XOY5 [get_cells {inst/gt_top........}]

#PCIe Line3

set_property LOC GTPE2_CHANNEL_XOY4 [get_cells {inst/gt_top........}]

改成

#PCIe Line0

set_property LOC GTPE2_CHANNEL_XOY4 [get_cells {inst/gt_top........}]

#PCIe Line1

set_property LOC GTPE2_CHANNEL_XOY5 [get_cells {inst/gt_top........}]

#PCIe Line2

set_property LOC GTPE2_CHANNEL_XOY6 [get_cells {inst/gt_top........}]

#PCIe Line3

set_property LOC GTPE2_CHANNEL_XOY7 [get_cells {inst/gt_top........}]

即可,在管脚约束文件里面也就可以正确约束文件了,当然不是每次都得修改这里的文件的,只要在发现PCIE管脚约束不对的时候,才需要看看这个区域是不是有问题

声明:所有文章属于个人在工作中所记下和搜集的笔记,不得转载