1、 常见存储器及其区别

参考《ROM、SDRAM、RAM、DRAM、SRAM、FLASH的区别》

注意不要混淆SRAM和SDRAM: SRAM是静态存储器,而SDRAM是动态存储器DRAM的一种,常用作内存。

2、SDRAM存储结构以及容量计算

参考《深入了解内存》

http://blog.chinaunix.net/uid-20321537-id-1966741.html

以及《详解嵌入式片上资源之SDRAM内存》

http://www.crifan.com/summary_embedded_peripherals_sdram/

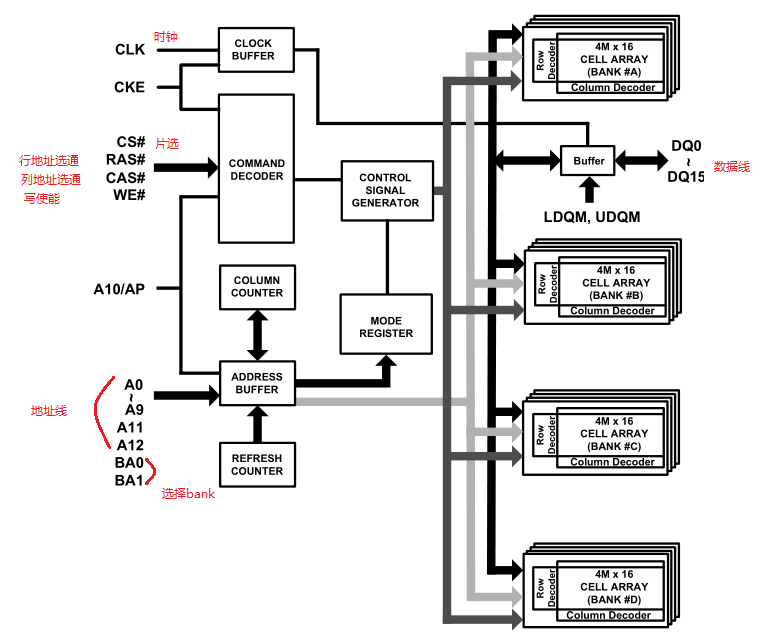

SDRAM由多个bank组成,每个bank又由多个存储单元堆叠在一起组成。这些存储单元分别存储数据的一个bit位,图中每个bank中有4个存储单元堆叠,

因此数据的位宽为4,也就是对于同一个地址一次能取出4个bit的数据。假设上图每个存储单元的大小为4M,那么该存SDRAM通常表示为存储单元大小x位宽 x bank数 = 4M x 4bit x 2bank

3、SDRAM硬件连线方式

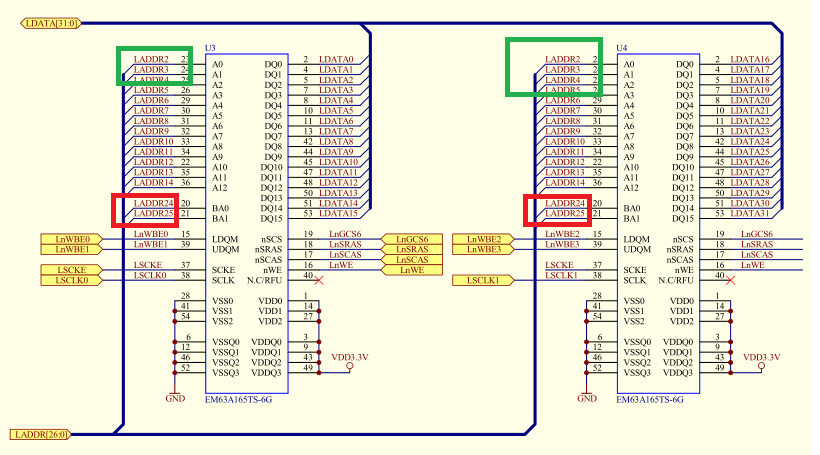

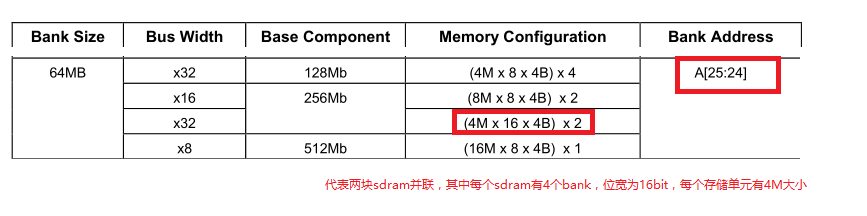

JZ2440_v3内存由两片EM63A165TS-6G并联而成。查看EM63A165TS-6G芯片手册,可知该SDRAM有4个bank组成,每个bank由16个4M大小的存储单元堆叠而成,即位宽为16

“The EM63A165 SDRAM is a high-speed CMOS synchronous DRAM containing256 Mbits. It is internally configured as 4 Banks of 4M word x 16 DRAM”

芯片引脚主要包含时钟、地址数据线、和一些控制线(片选、行地址选通、列选通)

查看JZ2440_V3电脑图,两片SDRAM引脚连接方式如下:

红色框中片选BA0、BA1是接在S3C2440地址线24、25上的。这个是根据S3C2440芯片手册第5章Memory control 中table SDRAM Bank Address Configuration Example而来:

另外绿色框中SDRAM的地址线是从0开始,但是连接到S3C2440,却是从2开始,这是由于SDRAM地址增加一位,数据增加了32bit也就是4个字节,而S3C2440地址线也就是逻辑地址线增加一位,数据应该只增加1个字节。