在学习完下学期的一些简单课程之后,之后的时间就留给了fpga的学习方向,首先用一个小题目来练一练手,回顾一下以前学到的知识

看到这个题我第一个想法就是想直接用计数器来实现,在一个使能信号结束之后,输出dout的波形有些类似于奇分频和偶分频,在之前的学习中,我学到了一些奇分频的方法,如制作两个分频后与运算结合得到奇分频,这次我想试一试用一种我理解的比较简单的方法,就是再做一个clk的翻转,使得我可以得到任意位置的表达值,即unclk,同时对clk和unclk计数,就可以很轻松的得到各个位置的数据,考虑到题目中所给的输出并不是一直执行,所以计数器只需要记一次数就ok,所以再做一个使能型号,如题计数器记到9就可以通过使能信号来停止了,同时注意到了计数器带来的偏差,如果用上述方法(时序逻辑)来实现的话,那么得到的dout是会有一点小瑕疵,即会和上图之间隔了一个clk的周期,所以在利用计数的模块务必要用组合逻辑来实现。

代码:

module demmo(clk,clr,dout);

input clk,clr;

output dout;

reg [3:0]cnt_1;

reg [3:0]cnt_2;

reg en_1;

reg en_2;

reg dout;

assign unclk = ~clk;

assign en = ~clr;

always@(posedge clk or negedge clr)

begin

if(!clr) begin

cnt_1 <= 4'b1;

en_1 <= 1;

dout <= 1'b0;

end

else if(en_1) begin

if(cnt_1 == 4'd9)begin

cnt_1 <= 4'b10;

en_1 <= 1'b0;

end

else

cnt_1 <= cnt_1 + 1'b1;

end

else

cnt_1 <= cnt_1;

end

always@(posedge unclk or negedge clr)

begin

if(!clr) begin

cnt_2 <= 4'b1;

en_2 <= 1;

end

else if(en_2) begin

if(cnt_2 == 4'd9)begin

cnt_2 <= 4'b10;

en_2 <= 1'b0;

end

else

cnt_2 <= cnt_2 + 1'b1;

end

else

cnt_2 <= cnt_2;

end

always@(*)

begin

if(cnt_1 == 4'd2|cnt_1 == 4'd5|cnt_1 == 4'd7|cnt_2 == 4'd4)

dout <= 1'b1;

else if(cnt_1 == 4'd3|cnt_2 == 4'd9|cnt_2 == 4'd5|cnt_2 == 4'd7)

dout <= 1'b0;

else

dout <= dout;

end

endmodule

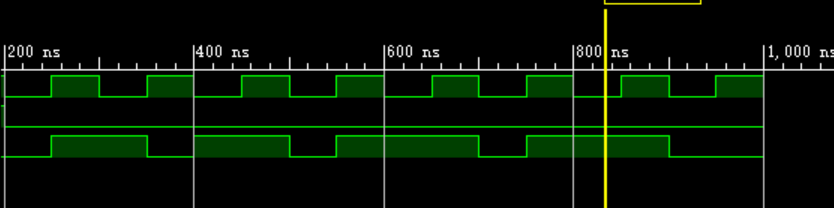

表现如下:

题目虽然简单,但是也帮助我熟悉了代码编辑的过程以及奇分频的利用方法。