有时候,有些BGA下方走线,线宽要求很细,但出了BGA后,通常为了适配阻抗匹配要求,又得变粗,这样,就得需要在BGA下方走特定线宽的线,出了BGA走另一个特定线宽的线。

以下图为例:可以看出,1/2位置处的线宽是不一样的。

根据阻抗匹配的要求,2 地方的线宽可能要是7.6mil,如下表所示,而BGA下方走线要求线宽统一是4mil,这样,通过设置区域规则,就能一劳永逸的解决该问题。

下面是步骤:

第一步:

第二步:

第三步:设计规则,这个是physical的规则,这个规则主要是BGA下方线宽的设置。这个区域设置好了后,在spacing中,也会出现这个规则,只是规则中没有赋值,下一步就是给这个区域附上规则,主要是spacing类型的规则,也即线与线间距,线孔距等。

第四步:

在spacing中,同样的也把刚才的区域规则,设置上,这个规则是线孔距,等,也很重要:

第五步:

指定区域(实测不可以)

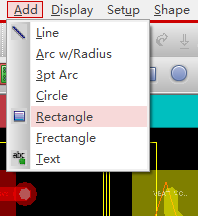

Add->Rectangle;

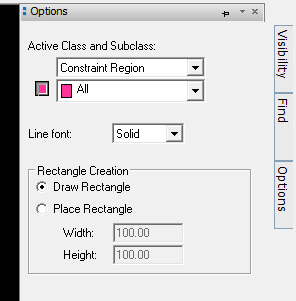

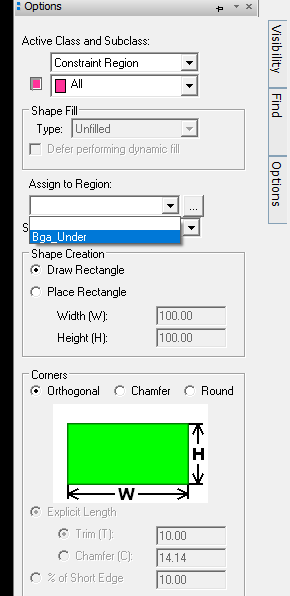

点击右边的Options,Active class and Subclass中选择Constarint region;

Assgion to region 中选择刚才新建的区域规则的名称;

然后再pcb面板中进行拖拽,就可以进行区域规则的设置了。

或者:

点击:

在右侧找到:实测不可以,没有赋值约束的地方

或者:

换另一个方法:

在option中找到:

画上之后的效果:

实验:走一根线,可以看出,BGA下方,线宽和BGA外部,是不一样的。

完毕。

喜欢就关注我的微信公众号:xiaoshi_IC,同步知乎,B站,csdn