本篇是习题专辑

往期回顾:

Part 1(chapter 1 - chapter 5):https://blog.csdn.net/zongza/article/details/83780572

Part 2(chapter 5 - chapter 10):https://blog.csdn.net/zongza/article/details/83933327

Part 3(概念专辑):https://blog.csdn.net/zongza/article/details/84100133

Part 4(习题专辑):https://blog.csdn.net/zongza/article/details/84111578

资料下载:

计算机体系结构-量化研究方法-Hennessy&Patterson著(英文版):https://download.csdn.net/download/zongza/10787837

计算机体系结构-量化研究方法-Hennessy&Patterson著(中文版):https://download.csdn.net/download/zongza/10787840

计算机系统结构教程-第二版-张晨曦著:https://download.csdn.net/download/zongza/10787843

计算机体系结构教程-学习指导与题解:https://download.csdn.net/download/zongza/10793886

流水线

主要知识点:画出停顿示意图(纵坐标用任务),画出流水线时空图(纵坐标用流水段或者任务,视情况而定,如果重复执行相同指令就是流水段时空图,如果执行多条不同指令就是任务时空图),吞吐率 效率 加速比 的计算,流水线改进(增加硬件,旁路等等)

例1:

假设非流水机单条指令经过相应的5个功能部件的执行时间分别为10ns,8ns,10ns,10ns和7ns,如果实现流水线且每个部件增加了1ns的附加开销,不考虑其他延迟因素,那么该流水线的加速比为多少?

例2:

注意这个最大吞吐率的计算! 意思是流水线进入稳定状态后,一定是每max(...)个时间流出一条指令。

例3:

主要考察流水线停顿

注意:

- 先分析相关(考察的就是相关带来的stall)

- 任务时空图是:向下的方向为纵轴 和 向左的方向为横轴

例4:

主要考察动态流水线的时空图

例5:

假设非流水线实现的时钟周期时间为1ns,ALU和分支指令需要4个时钟周期,访问存储器指令需5个时钟周期,上述指令在程序中出现的相对频率分别是:40%、20%和40%。在基本的流水线中,假设由于时钟扭曲和寄存器建立延迟等原因,流水线要在其时钟周期时间上附加0.2ns的额外开销。现忽略任何其他延迟因素的影响,请问:相对于非流水实现而言,基本的流水线执行指令的加速比是多少?

例6:

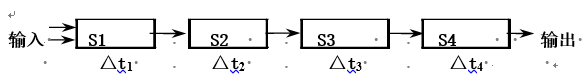

用一条4段浮点加法器流水线求8个浮点数的和: Z=A+B+C+D+E+F+G+H,求流水线的吞吐率、加速比和效率,其中△t1=△t2=△t3=△t4=△t。

答:可对原式作一简单变化,得到:

Z=[(A+B)+(C+D)]+[(E+F)+(G+H)]

7个加法8个数的流水线时空图如下:

CPI计算

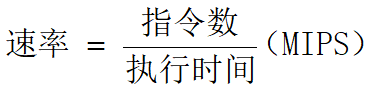

主要知识点:CPI计算,MIPS计算,程序执行时间

例1:

例2:

新CPI的计算 old-

例3:

例4:

新CPI的计算 base+

例5:

例6:

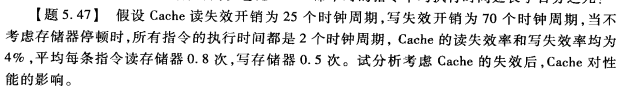

某RISC处理机各类指令使用频率和理想CPI(指令和数据访问Cache命中率为100%时的CPI)如下表所示。而实际测得的指令访问Cache缺失率(miss rate)为5%,数据访问的Cache缺失率为10%,Cache的缺失损失(miss penalty)为40个时钟周期。

1)该机器在无Cache缺失(理想情况)时的CPI是多少?(3分)

2)该机器在无Cache缺失(理想情况)时的速度比有Cache缺失时快几倍?(4分)

| 指令类型 |

ALU操作 |

Loads |

Stores |

Branches |

| 使用频率 |

43% |

21% |

12% |

24% |

| CPI ideal |

1 |

2 |

2 |

2 |

1)CPI=43%X1+21%X2+12%X2+24%X2=1.57

2)对指令讲,指令Cache的访问占全部访问的100%/(100%+21%+12%)=75%

对数据来讲,数据Cache的访问占全部访问的(21%+12%)/(100%+21%+12%)=25%

new_cpi=base+失效率X失效开销

=1.57+(75%X5%+25%X10%)X40=1.57+2.5=4.07

则:4.07/1.57=2.59=2.6 大约快2.6倍

阿姆达尔定律

例1:

例2:

例3:

指令集架构(从多地址的向下扩展)

例1:

某计算机的指令字长16位,设有单地址指令和两地址指令两类指令,若每个地址子段均为6位,且两地址指令有A条,问单地址指令最多可以有多少?

答:

双地址指令结构为:(4位操作码)(6位地址码)(6位地址码)

单地址指令结构为:(10位操作码)(6位地址码)

因此,每少一条双地址指令,则多2^6条单地址指令,

双地址指令最多是2^(16-6-6)=2^4=16条 ,

所以单地址指令最多有(16-X)*2^6条。

例2:

若某机要求有:三地址指令4条,单地址指令192条,零地址指令16条。设指令字长为12位,每个地址码长3位。问能否以扩展操作码为其编码?

答:能,如下:

例3:

若某机要求:三地址指令4条,单地址指令255条,零地址指令16条。设指令字长为12位.每个地址码长为3位。问能否以扩展操作码为其编码?如果其中单地址指令为254条呢?说明其理由。

解:

(1)不能用扩展码为其编码。

指令字长12位,每个地址码占3位,三地址指令最多是2^(12-3-3-3)=8条, 现三地址指令需4条,

所以可有4条编码作为扩展码,而单地址指令最多为4×2^3×2^3=2^8=256条,现要求单地址指令255条,

所以可有一条编码作扩展码

因此零地址指令最多为1×2^3=8条

不满足题目要求,故不可能以扩展码为其编码。

(2)若单地址指令254条,可以用扩展码为其编码。

依据(1)中推导,单地址指令中可用2条编码作为扩展码,零地址指令为2×2^3=16条,满足题目要求

Cache平均访问时间

例1:

答:

例2:

答:

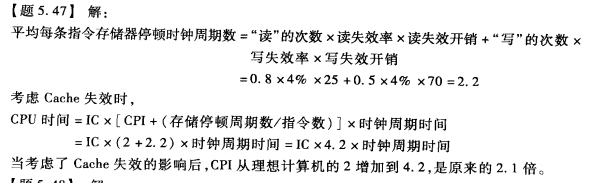

CPU时间(也可以看成CPI的计算)

例1:

答:注意这里不是求平均访问时间,而是计算停顿开销(=miss_rate * miss_pernalty)

页表计算

例1:

一个有快表和慢表的页式虚拟存储器,最多有64个用户,每个用户最多要用1024个页面,每页4K字节,主存容量8M字节。

(1)写出多用户虚地址的格式,并标出各字段的长度。

(2)写出主存地址的格式,并标出各字段的长度。

(3)快表的字长为多少位?分几个字段?各字段的长度为多少位?

(4)慢表的容量是多少个存储字?每个存储字的长度为多少位?

答:

用户号:64=26,虚页号:1024=210,页内地址:4K=212,主存页数:8M/4K=211

(1)多用户虚地址:

用户号(6位)+虚页号(10位)+页内地址(12位) 共28位

(2)主存地址:

主存实页号(11位)+页内地址(12位) 共23位

(3)快表字长27位;分3个字段:用户号6位,虚页号10位,实页号11位

(4)慢表容量为2(6+10),每个存储字长为:主存页号+1=12位。

相关分支预测状态机:

例1:

例2: