版权声明:欢迎转载 https://blog.csdn.net/antony1776/article/details/83743856

四大 CPU 架构:ARM,X86,MIPS,PowerPC

- ARM 功耗低,在无线局域网,3G,手机终端,手持设备,有线网络通信设备应用广泛;

- MIPS:被CISCO公司大量采用在高端路由器上;

- PowerPC:是通信和工业控制领域应用广泛的处理器,华为中兴的设备,

中央处理器体系结构:

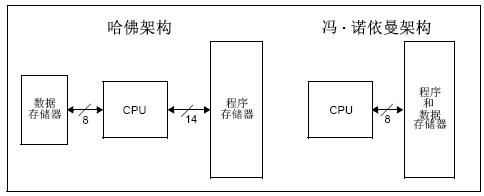

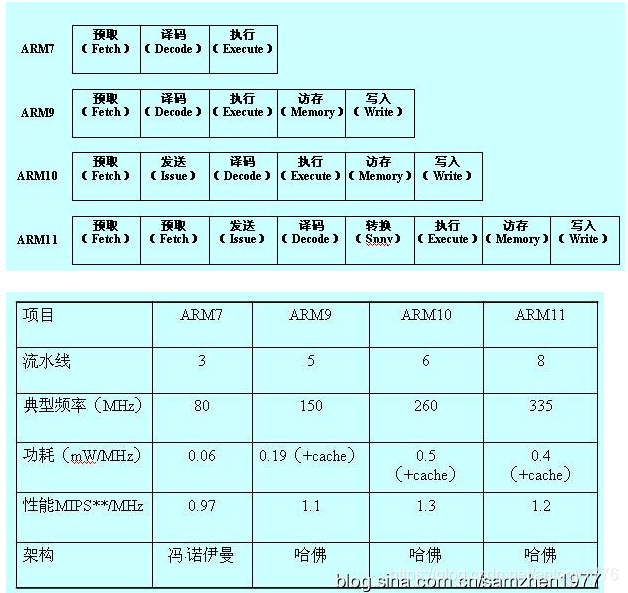

- 冯诺依曼:程序指令存储器和数据存储器合并在一起的存储器结构;

- 哈弗结构: 分开存储;

指令集:

- RISC: 指令少,指令单周期执行,目标代码更大;ARM,MIPS,PowerPC

- CISC: 指令复杂,指令周期长,目标代码多;X86,

ARM 的功耗低的原因说到头就是乱序执行能力不如X86。换句话说,就是用户在使用电脑的时候,他的操作是随机的,无法预测的,造成了指令也无法预测。X86为了增强对这种情况下的处理能力,加强了乱序指令的执行还增强了单核的多线程能力。这样做的缺点就是,无法很有效的关闭和恢复处理器子模块,因为一旦关闭,恢复起来就很慢。为了保持高性能,就不得不让大部分的模块都保持开启,并且时钟也保持高速切换。直接后果就是耗电高。而ARM的RISC指令优化强在确定次序的执行,并且依靠多核而不是单核多线程来执行,这样容易保持子模块和时钟信号的关闭,显然就更省电。

存储器: ROM(只读),Flash(NOR, NAND),RAM(随机存取存储器)

- RAM: 静态RAM(SRAM);动态RAM(DRAM);

- DRAM以电荷形式进行存储,数据存储在电容器中,电容器会由于漏电而导致电荷丢失,需要定期被刷新;

- SRAM:只要供电一次就会保持一个值;

串口与总线:

USB:

以太网接口:

- 由MAC(以太网媒体接入控制器)和PHY(物理接口收发器),分别处于数据链路层和物理层;

- CPU直接跟MAC进行交互,以太网接口的硬件构成分别是,CPU—>MAC---->PHY----->以太网隔离变压器---->RJ45接头;

原理图分析:

- 阅读电路板的原理图获得各种存储器、外设所使用的硬件资源,主要包括存储器和外设控制芯片所使用的片选、中断、和DMA资源;

- 硬件原理图中的元素: 符号,网络, 描述;

- 硬件时序分析:在电路板调试的任务中,掌握时序分析的方法就比较有必要了;

- 仪器仪表使用:万用表,示波器,

寄存器:

- 是中央处理器内的组成部分,是有限存储容量的高速存储部件,他们可用来暂存指令,数据,和地址。32位cpu

- 8086的寄存器:通用寄存器,指令指针,标志寄存器,段寄存器。

工作原理:

- cpu对存储器中的数据进行处理时,往往先把数据取到内部寄存器中,而后再做处理。

- 乱序执行技术:使CPU内部电路满负荷运转并相应提高CPU运行程序的速度。

- 用途:1、 将寄存器内部的数据执行算术及逻辑运算,2、存于寄存器内的地址可用来指向内存的某个位置,寻址,3)读写数据到电脑周边设备。