链接:https://www.cnblogs.com/xiaomeige/p/7084539.html

Can't place multiple pins assigned to pin location Pin_F16

在我们芯航线FPGA开发板上,使用了一片128Mbit的SDRAM存储器。当大家在自己建立工程,或者移植其他家的工程时候,往往之前一切顺利,但是在最终分配完引脚进行全编译时,都会报错,报错内容如下:

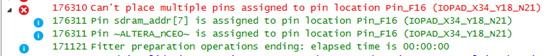

| "Can't place multiple pins assigned to pin location Pin_F16 (IOPAD_X34_Y18_N21)" |

这句提示翻译成中文的意思是"无法将多个引脚分配到Pin_F 16这个管脚上"。很多第一次遇见这种问题的朋友会很郁闷,回去检查完引脚分配后,发现并没有重复(况且引脚分配器那里也不让重复分配)。然后就摸不着头脑了。

其实,我们可以点击这个报错信息前面的三角符号,查看子级的细节提示,如下图所示:

通过细节信息我们可以知道,ALTERA_nCEO引脚也被分配到了F16引脚,而nCEO引脚又是什么呢?我们在Cyclone IV Device Handbook中第224页找到了关于该引脚的描述:

| Output that drives low when configuration is complete. In a single-device configuration, you can leave this pin floating or use it as a user I/O pin after configuration. In a multi-device configuration, this pin feeds the nCE pin of the next device. The nCEO of the last device in the chain is left floating or used as a user I/O pin after configuration. 当FPGA器件的配置过程完成后,该引脚输出低电。对于一个只配置一个器件的系统,用户可以将此引脚悬空,或者在配置完成后当做普通用户IO使用。在一个需要配置多设备的系统中(链式结构,使用一个Jtag链配置多个FPGA器件),该引脚连接到下一个器件的引脚的nCE。链的最后一个设备的nCEO悬空或在配置完成后作为普通用户I / O引脚使用。 If you use the nCEO pin to feed the nCE pin of the next device,use an external 10-k pull-up resistor to pull the nCEO pin high to the VCCIO voltage of its I/O bank to help the internal weak pull-up resistor.(对于多器件配置系统,翻译略) If you use the nCEO pin as a user I/O pin after configuration, set the state of the pin on the Dual-Purpose Pin settings 如果用户希望将该引脚在FPGA配置完成后作为普通用户IO使用,需要设置该脚的状态为双功能引脚。(具体见后文图文说明) |

通过这两段话我们知道,这个引脚主要用于链式系统中,即当一个系统(单板)上有多个FPGA器件,使用一个JTAG链配置时,该引脚主要用于器件的级联控制。如果在只需要配置一个器件的系统中,则该引脚可以设置为悬空或者在器件完成配置后作为普通用户IO使用。

在我们芯航线FPGA学习套件上,只使用了一片FPGA,因此不存在链式配置结构,因此,我们将该引脚作为了普通用户IO使用,并且连接到了SDRAM芯片的addr7上。故而编译时会有此提示。解决方案就是按照手册中摘录的第三段话设置,将该引脚设置为双功能引脚。具体设置步骤如下:

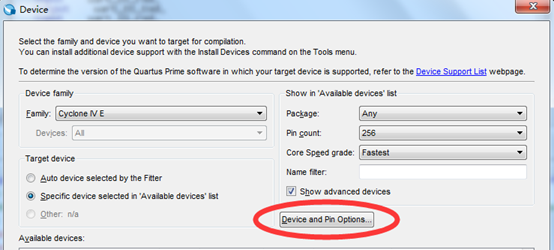

Quartus II中依次点击【Assigments】-> 【Device】,在弹出的界面中选择"Device and Pin Options"

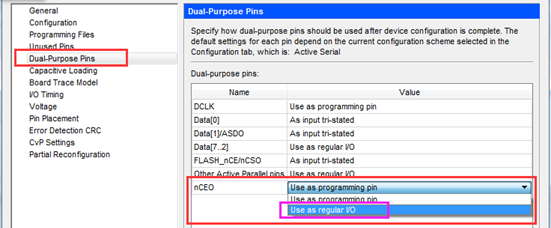

在弹出的选项卡中,选择Dual-Purpose Pins,在右侧双击nCEO的值,在弹出的下拉选项中选择Use as regular I/O即可。

然后点击OK退出,重新全编译工程,就没有这个错误啦。

大家在使用自己的开发板时,如果也提示这样的错误,可以按照这个解决思路来进行,不同的开发板,可能就是该引脚分配的功能不一样(我们芯航线FPGA开发板是分配到了sdram的addr7上),解决方案并无任何区别。