版权声明:本文为博主原创文章,未经博主允许不得转载。 https://blog.csdn.net/xiong3110/article/details/54583824

所述内容都是从自个做的一个项目得来,与一般的会有些区别,持续更新,纠正错误。

先简单概括下

组成:两根串行线,一根双向数据线DATA, 一根时钟线CLK

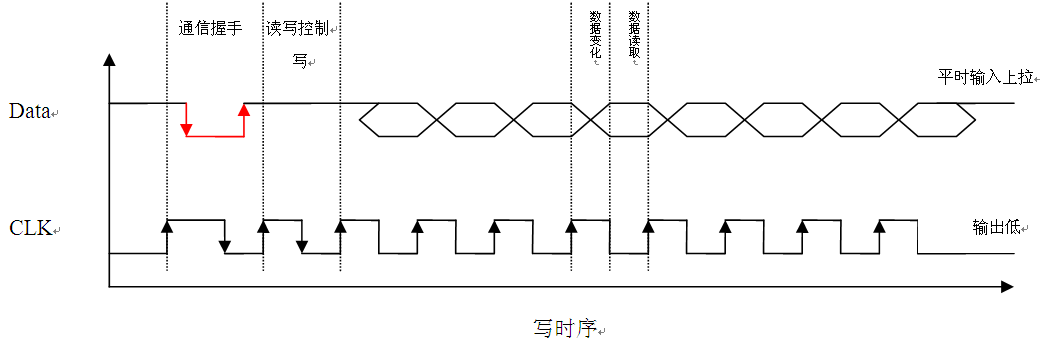

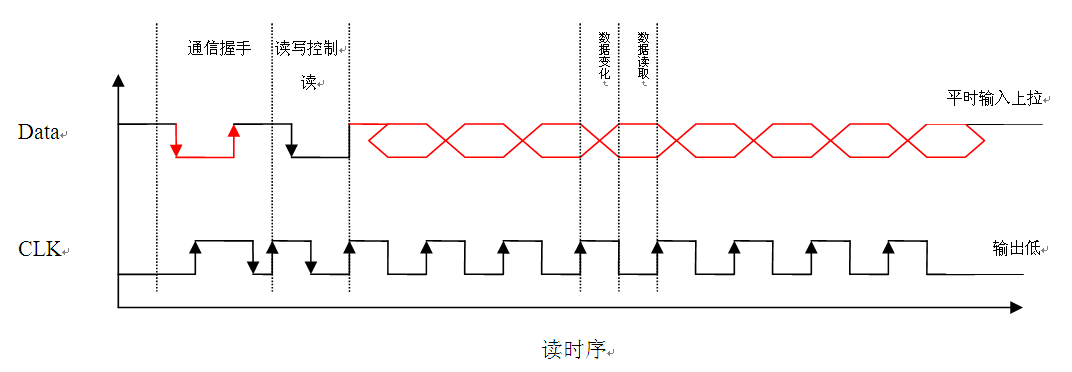

特点:常态下 ,主机控制CLK输出低电平,从机控制DATA输出高电平; 在时钟信号的上升沿开始写数据,下降沿读数据

主机写时序(请求发数据):

1、主机先将CLK线拉高,持续200ms,等待从机响应 ---> 从机检测到拉高后将DATA线拉低,做出回应

2、收到应答后主机拉低CLK线,读取一位data(开始信号),等待从机释放data线控制权 --> 从机检测到clk拉低后拉高data线,并设置data线为输入口,等待主机的读写控制信号

4、主机检测到data线拉高后,再延时20us,来获得data控制权,然后将clk线拉高,同时改变data线的电平(低/高 代表读/写数据 ),将其输出给从机 --> 从机开始准备接收数据(从下次clk线的上升沿开始)

如下图:

主机读时序:

1、从机拉低data线,持续200ms ,等待响应--> 主机检测到后 拉高clk线 来应答

2、从机检测到回应后拉高data线。释放控制权,将data线转为输入口,等待主机输出读写控制信号 --> 主机拉低时钟线,延时20us 来读取一位data(开始信号),然后拉高clk线,同时改变data线的电平(低/高 代表读/写数据 ),将其输出给从机

3、从机在下个时钟上升沿开始发送数据