前段时间,一直在调SDRAM与VGA的驱动,搞了很长一段时间,参考了很多资料,最终终于思路理清了,不过鉴于手上没有相关的硬件电路,所以暂时搁置了,回归正题,先来看IIC之间的通信吧。

首先,IIC通信与UART,还有SPI统称为串行接口通信,不过它们之间还是有区别的,如UART的负电平逻辑,还有UART通信不需要时钟,只需要特定的波特率即可,SPI与IIC都可以有一个主机,多个从机的情况,不过IIC适用于短距离传输,如片间通信,摄像头的配置等场景。

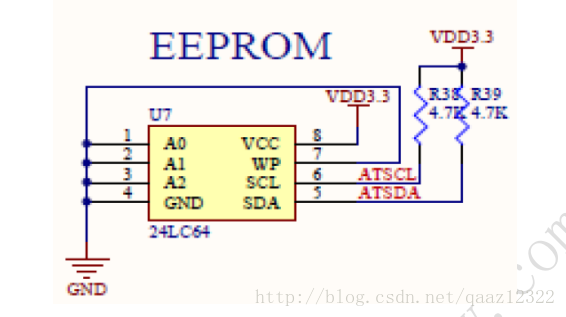

要搞定IIC首先来看IIC的硬件接口:

如图所示,我们知道IIC一个主机可以悬挂多个从机,所以地址线A2,A1,A0 可以实行片选的功能,那么WP这个引脚的功能就是当WP悬空或者接地的时候,表示这时的EEPROM既可以读,也可以写,当WP接电源时,则只可以读而不能写。

SCL与SDL这两个引脚,必须上拉,否则驱动能力不够,无法进行正常的IIC通信。

OK,硬件接口已经介绍清楚了,那么我们现在开始来看协议了。

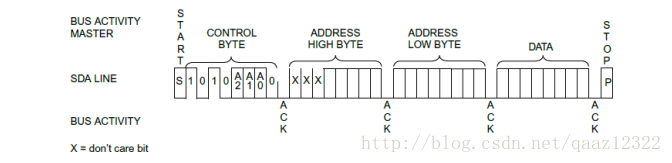

首先IIC分为字节读写和页面读写,首先来看字节读写的协议:

如上图所示,如果我们要向EEPROM中写入一个字节的数据,得有如下几个步骤:

1.开始信号——在SCLK的高电平器件,拉低SDA的信号(由1 变为0)。

2.控制字节——即器件地址,就是你操作那一块EEPROM。

3.ACK信号——由从机发出,主机为接收,所以在此阶段,sda_link必须置为0,即为读取这个应答信号,所以在SCLK的高点平期间。

4.字节地址——即某一块EEPROM里面的哪一个地址。

5.ACK信号——与上述相同。

6.数据信号——即你往某个地址里面写入的8位数据。

7.ACK信号——上述相同。

8.结束信号——在SCLK的高电平期间,拉高SDA信号,表示通信结束。

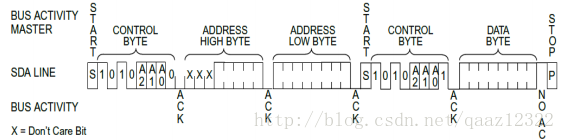

再来看读的时序:

由上图可看出读时序的前面处理方式与写相同,不同的时在第三个ACK信号来了之后,如果是读,那么会又有一个起始信号,紧接着读器件地址,然后应答,再然后读数据,再然后在SCLK的低电平期间发送一个NO ACK信号,要记住这个信号由主机发出,然后紧接着一个结束信号。

由上述读写时序我们可知,通信的起始均在SCLK的高电平期间发生跳变,这就据定了我们其他信号跳变均在SCLK的下降沿,SCLK高电平期间数据稳定,适用于读(即低电平改变数据,高电平采集数据)。

具体过程如下:

首先板子上电来个初始化需要来个延时,具体多少用计数器自己搞定。

代码如下:

reg [6:0] hadware_initial_delay;

wire hadware_initial_delay_done;

always@(posedge clk or negedge rst_n)

if(!rst_n)

hadware_initial_delay<=7’d0;

else

if(hadware_initial_delay<=7’d49)

hadware_initial_delay<=hadware_initial_delay+1;

else

hadware_initial_delay<=hadware_initial_delay;

assign hadware_initial_delay_done=(hadware_initial_delay==7’d50)?1’b1:1’b0;

OK,我们要知道IIC的速率一般就几百KH而我们的系统时钟为50M,所以需要分频:

代码如下:

reg [8:0] sclk_cnt;

always@(posedge clk or negedge rst_n)

if(!rst_n)

sclk_cnt<=9’d0;

else

if(hadware_initial_delay_done)

begin

if(sclk_cnt<9’d499)

sclk_cnt<=sclk_cnt+1;

else

sclk_cnt<=0;

end

assign sclk=(sclk_cnt<=9’d249)?1’b1:1’b0;

OK,我们知道SCLK高电平期间采集数据,低电平期间改变数据,那么当然,这个“期间”肯定时时钟沿中间最好啦,毕竟更容易满足建立时间与保持时间,很稳定的。

具体代码如下:

wire sclk_posedge_middle=(sclk_cnt==9’d124)?1’b1:1’b0;

wire sclk_negedge_middle=(sclk_cnt==9’d374)?1’b1:1’b0;

OK,读写定义了那么多个过程,当然需要状态机来搞定啦,定义变量如下:

parameter IDLE = 4’d0 ;

parameter START1 = 4’d1 ;

parameter ADD1 = 4’d2 ;

parameter ACK1 = 4’d3 ;

parameter ADD2 = 4’d4 ;

parameter ACK2 = 4’d5 ;

parameter DATA = 4’d6 ;

parameter ACK3 = 4’d7 ;

parameter STOP1 = 4’d8 ;

parameter START2 = 4’d9 ;

parameter ADD3 = 4’d10;

parameter ACK4 = 4’d11;

parameter DATA_READ = 4’d12;

parameter NO_ACK = 4’d13;

parameter STOP2 = 4’d14;

OK,再来个宏定义,假设写入是这几个地址,这几个数据。

define DEVICE_READ 8'b1010_0001 define DEVICE_WRITE 8’b1010_0000

define WRITE_DATA 8'b0001_0001 define BYTE_ADDR 8’b0000_0011

SDA双向端口,这个记住,一般这样搞;

reg sda_link;

reg sda_out_r;

assign sda=sda_link?sda_out_r:1’bz;

当作为输出时,对吧,使sda_link拉高,作为输入时,输入高阻。

各过程如下:

reg [3:0] current_state;

//reg [3:0] next_state;

reg [7:0] db_r;

reg [3:0] num;

reg [7:0] data_out_reg;

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin

sda_link<=0;

db_r<=0;

num<=0;

current_state<=IDLE;

sda_out_r<=0;

data_out_reg<=8’b0;

end

else

begin

case(current_state)

IDLE:begin

sda_out_r<=1;

sda_link<=1;

if(!sw1_r||!sw2_r)

current_state<=START1;

else

current_state<=IDLE;

end

START1:if(sclk_posedge_middle)

begin

sda_out_r<=0;

db_r<=`DEVICE_WRITE;

current_state<=ADD1;

end

else

current_state<=START1;

ADD1 :

if(sclk_negedge_middle)

begin

if(num==4'd8)

begin

sda_link<=0;

num<=0;

current_state<=ACK1;

sda_out_r<=1;

end

else

begin

current_state<=ADD1;

sda_out_r<=db_r[7-num];

num<=num+1;

end

end

else

current_state<=ADD1;

ACK1:

if(sclk_posedge_middle)

// begin

// if(!sda)

// begin

begin // */

current_state<=ADD2;

db_r<=`BYTE_ADDR;

end

else

current_state<=ACK1;

ADD2:begin

sda_link<=1;

if(sclk_negedge_middle)begin

if(num==4'd8)

begin

sda_link<=0;

current_state<=ACK2;

num<=4'd0;

sda_out_r<=1;

end

else

begin

num<=num+1;

current_state<=ADD2;

sda_out_r<=db_r[7-num];

end

end

else

current_state<=ADD2;

end

ACK2:

if(sclk_posedge_middle)

////begin

//if(!sda)

begin

if(!sw1_r)

begin

db_r<=`WRITE_DATA;

current_state<=DATA;

end

else

if(!sw2_r)

begin

current_state<=START2;

sda_out_r<=1;

end

end

else

current_state<=ACK2;

DATA: begin

sda_link<=1;

if(sclk_negedge_middle)

begin

if(num==4'd8)

begin

num<=4'd0;

current_state<=ACK3;

sda_out_r<=1;

sda_link<=0;

end

else

begin

num<=num+1;

current_state<=DATA;

sda_out_r<=db_r[7-num];

end

end

else

current_state<=DATA;

end

ACK3: if(sclk_posedge_middle)

// begin

// if(!sda)

current_state<=STOP1;

// end

STOP1:

begin

sda_link<=1;

sda_out_r<=0;

if(sclk_posedge_middle)

begin

sda_out_r<=1;

if(sw1_r)

// 你要是不等它松开才恢复初始状态,那么你一旦恢复初始状态SW1_r就为低电平,他又开始写了,所以为了避免重复写入数据。

current_state<=IDLE;

else

current_state<=STOP1;

end

else

current_state<=STOP1;

end

START2:begin

sda_link<=1;

if(sclk_posedge_middle)

begin

sda_out_r<=0;

sda_link<=1;

db_r<=`DEVICE_READ;

current_state<=ADD3 ;

end

end

ADD3: begin

if(sclk_negedge_middle)

begin

if(num==4'd8)

begin

num<=0;

sda_link<=0;

sda_out_r<=1;

current_state<=ACK4;

end

else

begin

num<=num+1;

sda_out_r<=db_r[7-num];

current_state<=ADD3;

end

end

else

current_state<=ADD3;

end

ACK4:

if(sclk_posedge_middle)

// begin

// if(!sda)

current_state<=DATA_READ;

else

current_state<=ACK4;

// end

DATA_READ:

begin

sda_link<=0;

if(sclk_posedge_middle)

begin

if(num==4'd8)

begin

sda_link<=1;

sda_out_r<=1;

current_state<=NO_ACK;

num<=4'd0;

end

else

begin

num<=num+1;

current_state<=DATA_READ;

data_out_reg[7-num]<=sda;

end

end

end

NO_ACK:

if(sclk_negedge_middle)

begin

sda_out_r<=1;

current_state<=STOP2;

end

else

current_state<=NO_ACK;

STOP2:begin

sda_out_r<=0;

sda_link<=1;

if(sclk_posedge_middle)

begin

sda_out_r<=1;

current_state<=IDLE;

end

else

current_state<=STOP2;

end

default:current_state<=IDLE;

endcase

end

assign data_out=data_out_reg;

endmodule

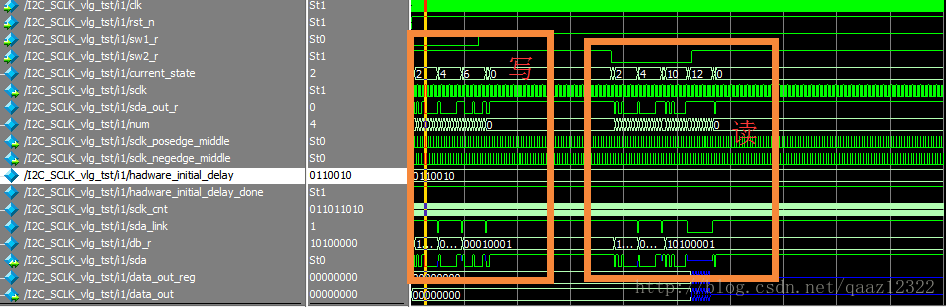

仿真结果如下:

OK,搞定,输出当然可以连接数码管,连接LED等来显示是否正确。