折腾了近一个星期的代码,终于调通了。显示屏总算输出正常了,简直开心到飞起啊,哈哈哈哈哈哈,虽然只是小事,但还是很有成就感。毕竟一次次上电一次次失望,累积起来更多的期望。自己写的bug,跪着也要改完!

正题,总结一下。

-------------------------------------------------分割线-------------------------------------------

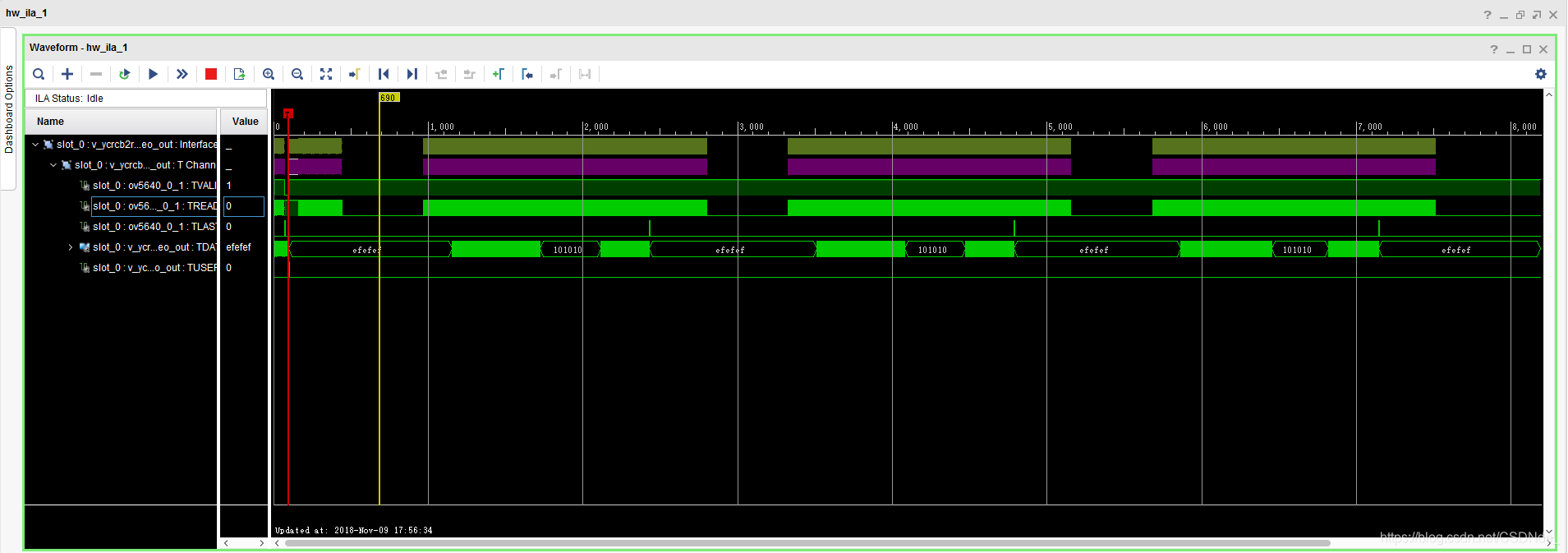

之前写的代码,因为只用做最后仿真探取数据,所以并未考虑信号与数据同步的问题,仿真结果出的那么多数据,用matlab对比出的结果往往注重的是整体。到真正上板接显示屏的时候问题就显而易见了,显示屏的电源信号灯都没有被点亮,说明并没有数据通过。之前说过的添加system ila核,open hardware manager,触发。在这里为了说明后面出现的问题,放上一张原工程的正确输入数据和信号:

第一次问题:user有输入无输出。从上图可看到,user信号在输入端是存在的,但在第一次的仿真输出数据中没有:(还好当时跟朋友吐槽的时候顺手截了一张图)

检查代码,因为当时写的是user的if条件是输入的user和输出端的valid,ready同时有效时才输出,观察波形并没有这种时候啊。。。所以先去掉这个自以为的条件。。。(这里也强调一点!逻辑清晰真的很重要!很重要!很重要!!!重要的事情说N遍!就拿这个来说,不要急着急着就下手写代码,搞清楚信号的逻辑关系,最好自己在纸上规划好,再去研究怎么实现,不要想一出是一出,想到哪里写哪里。)

第二次问题:正常的ready输入一段有一段无,而我的ready输入就显示一直ready,虽然可以理解为这个模块可能是有那么多余量来ready信号的输入,但师父说这个工程里这个ready信号和另一个模块很大关系,很可能是我的输出有问题,反馈到那个模块,导致后来ready的输入有问题。另一个模块:

如图所示,v_tc_0为控制ready的模块,旁边的video_in为gamma模块的输出。那么问题来了,这一次又是因为脑子不会转弯,画张粗略的图来说明这次问题所在!

真的是随手画的,哈哈哈哈哈哈,时间有限,不过要是能熟练使用visio这种画图工具还是很有用的。正题,这里由于m_tvalid和m_ready的时序错开,导致输出的数据last部分很可能会丢失。如果last丢失,那反馈到v_tc_0模块的信号也会出错,自然,下来的ready信号也不对。找到了问题所在,那面临的就是要是信号和数据同步,至少last信号对应的确实是last的数据。按照师父的说法,为了避免控制ready信号时的尴尬,我们可以在数据输出时增加一个fifo的IP核,使数据和信号同步输入,同步输出,ready作为输入输出的判断。

接着,加一个fifo,连一些接口(用的还是axis,可以参考官方手册),调试,看schematic的连线。如果有必要可以写一个testbench先做个验证。这里要注意的大概就是接口该wire的要wire吧,总之耐心点看看message和Tcl Console,有错误解决不了可以去xilinx官网的forum里找找。

下午终于上电一次pass了,给我开心的啊。不方便上实物图,就上个正确的仿真图吧。

后面还要加一些其他功能,慢慢来吧。攻城狮,对于我最苦的可能是看英文文献的时候吧,datasheet,message,forum这些都是英文版的,还好有翻译软件。。。还有不要浮躁,沉下心。能沉下心,那一切都清晰了。

FPGA series #gamma模块加入工程上板接显示屏

猜你喜欢

转载自blog.csdn.net/CSDNde_/article/details/84072846

今日推荐

周排行