System Generator从入门到放弃(三)-Digital Filter

本文转自:https://blog.csdn.net/fpgadesigner/article/category/6985565/3

文章目录

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成HDL文件,或者网表,可以在ISE中进行调用。或者直接生成比特流下载文件。能够加快DSP系统的开发进度。

一、Digital Filter

1、简介

2、产生正弦信号

2.1 本部分设计使用到的block

3、数字滤波器的设计

3.1 本部分设计使用到的block

3.2 数字滤波器设计

3.3 FPGA系统配置

3.4 将设计导出到FPGA

3.5 打开Vivado示例工程

4、FDATool block的使用

5、生成说明文档与testbench

5.1 生成说明文档

5.2 生成testbench

6、资源分析与时序分析

6.1 查看分析结果

6.2 时序分析

6.3 资源分析

6.4 资时序/资源分析失败的说明

以上内容请移步

https://blog.csdn.net/Pieces_thinking/article/details/83656785

7、Gateway In和Gateway Out详解

7.1 Simulink到FPGA的转换

Simulink中的仿真模型为连续时间系统,数据格式多种多样;而FPGA中为离散时间系统,数据必须用一定的位数进行量化。两者之间必须要进行从连续到离散的转换、数据格式的转换,否则无法进行正确的FPGA设计。Xilinx Blockset中提供了相应的解决方案。

Gateway In和Gateway Out这两个block便是Simulink与FPGA之间的转换接口。经过转换后,Gateway In对应的是HDL模型中input;Gateway Out对应的是HDL模型中的output。可以说,所有的System Generator设计中必须包含至少一个Gateway In和Gateway Out。

7.2 Gateway In block

7.2.1 数据类型转换

Gateway In block可以完成从Simulink数据类型到FPGA数据类型的转换:

借助于此功能,在Simulink中搭建仿真模型,外部信号可以传入FPGA系统,方便的进行仿真测试。数据类型转换势必会牵扯到量化和溢出的问题,Gateway In block也对此做了相关支持,具体可参考参数设置小节。

7.2.2 block特性

除了数据类型转换功能外,Gateway In block还具有如下特性功能:

- 定义了FPGA设计中的输入端口,修改block名称即可修改HDL端口信号名称;

- 使用System Generator生成testbench时,软件会将输入到Gateway In

block的Simulink仿真信号按照设置的数据格式转换并存储到dat文件中,在testbench中调用(具体可参考本系列上一篇博文)。

7.2.3 参数设置

(1).在Output Type和Arithmetic type中可以设置转换后输出数据的格式:

- Boolean:布尔逻辑值,在HDL模型中对应单比特信号。

- Fixed-point:定点数,包括“Signed(2’s comp)”带符号数二进制补码和“Unsigned”无符号数两种。

- Floating-point:浮点数,Floating-point

Precision可以设置数据为单精度(Single)、双精度(Double)或自定义的浮点数格式(Custom,自行规定指数与尾数位宽)。

(2).用有限位宽表示Simulink中的数据类型,必然会产生量化误差。在Quantization中可以选择数据的量化方式:

- Truncate:直接舍弃不需要的低位。

- Round(unbiased:+/-Inf):以四舍五入的方式量化。

(3).数据转换过程中还可能会出现溢出(设置的数据格式无法表示Simulink中的值),Overflow中可以设置不同的处理方式:

- Wrap:舍弃掉需要表示的值的高位。

- Saturate:溢出的数转换为(所设置的数据格式能表达的)最大值或最小值。

- Flag as error:溢出时Simulink会报错(这个选项只在Simulink仿真时有效,在导出到FPGA时仍当作wrap处理)。

这里可以设置Gateway In转换到FPGA设计后的接口类型:“None”表示作为HDL设计的输入端口;“AXI4-Lite”表示会被当作AXI4-Lite总线(目前不会用到,相关配置也暂时不做介绍)。

IOB timing constraint设置该端口的时序约束:“None”表示不作约束;“Data rate”会将System Generator block中的系统时钟周期设置作为IO时钟约束。

如果System Generator的设计中,Gateway In恰好对应于FPGA硬件设计中的某个管脚,可以选中“Specify IOB location constraints”,根据提示完成管脚位置与IO电平标准的设置。

7.3 Gateway Out block

7.3.1 block特性

与上一个block相反,Gateway Out block是完成从FPGA数据类型到Simulink数据类型的转换。其具有如下特性:

定义了FPGA设计中的输出端口,修改block名称即可修改HDL端口信号名称。Gateway Out还可以只作为测试端口,此时只是为了观察DSP系统内部,不会导出到FPGA设计中。

使用System Generator生成testbench时,软件会把从Gateway Out block输出的Simulink仿真信号存储到dat文件中,在testbench中调用来帮助设计中检查设计是否符合预期。

7.3.2 参数设置

当System Generator设计的DSP系统后续还接入了其它Simulink仿真模块时(即System Generator仅作为Simulink仿真的一个子系统),需要选中“Propagate data type to output”,将FPGA数据类型转换为相应的Simulink数据类型。

当选中“Translate into output port”时,该block将会作为FPGA设计的输出端口;如果没有选中,则该block会被视作为了观察DSP系统内部信号的测试端口,同时该block在Simulink中显示为灰色,如下图:

“Implementation”标签下的设置与上一个block基本相同,不再赘述。

8、设计优化与导入MATLAB变量

8.1 优化设计

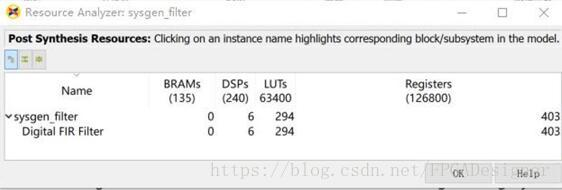

在第4篇中我们进行了设计的资源分析,结果如下:

该设计使用了6个DSP单元,这是因为该FIR滤波器系数有11个,且具有对称性,因此需要使用6个乘法器并行运算。打开FDATool,点击上方的“Filter Coefficients”按钮,可查看滤波器系数:

System Generator中FPGA时钟设置为20MHz;Gateway In block的采样率也为20MHz。这样每个时钟都要处理一个数据,因此在实现滤波器时采用了并行结构,占用了6个乘法器。

我们可以设置过采样模式来优化设计的资源使用率。在System Generator block中将FPGA clock period设置为8.33ns(120Mhz);Simulink system period设置为1/120e6(120MHz);Gateway In的采样率比便。这样每6个时钟处理一个数据,期望所有的乘法操作能共用一个乘法器。

点击Generate导出设计,此时Simulink会提示一个警告:

主要提示我们采样率和时钟的设置,本设计是故意采用这种设置方式的,因此不用在意这个警告。运行结束后,生成资源分析报告:

看到DSP单元只使用了一个,其它资源也节省了超过一半,符合预期。总而言之,在进行System Generator设计时,要综合考虑设计指标和硬件实际情况来对设计进行针对性优化。

8.2 导入MATLAB变量

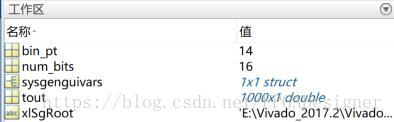

Simulink已经提供了足够强大的功能,但有些设计还是需要在MATLAB中进行(比如考察位宽对数据量化的影响)。System Generator提供了该特性:可以将MATLAB的workspace中的变量直接用于block参数配置。

假设在MATLAB中已经确定某一数据的最佳位宽,workspace如下:

打开Gateway In block(或其它需要配置该值的block),在编辑框里直接输入workspace中的变量名称即可:

所有的block都支持该特性。

9、选择最佳数据类型

目前,还有些问题需要解决:

- 如何选择一个最合适的数据类型(以最少资源达到性能需求)?

- 如何选择系统的输出位宽(保证信号不失真)?

传统的HDL模型设计方法中,博主通常会用MATLAB进行仿真,确认位宽对数据量化的影响;或在Vivado中仿真,截取合适的滤波器输出位数。System Generator提供的相关特性可以大大简化该流程,本文将对此做介绍。

9.1 本设计使用到的block

Xilinx block

- Convert(->Basic Elements):数据格式转换

- Reinterpret(->Basic Elements):数据格式转换

其它block

- Digital Filter Design(DSP System Toolbox->Filtering->Filter

Implementations):设计数字滤波器

这里给出了设计中用到的所有block在库中的路径,后文不再提及(前文用过的block没有给出;同一block会包含在多个库中,为了寻找方便这里只列出一个路径)。

9.2 FPGA设计与理想情况对比

虽然在第2篇的设计中观察到输出信号的频谱图确实符合设计要求,但由于经过数据转换,数据类型、位宽等问题都会影响到计算精度,我们很难评估该结果与理想情况的偏差。

Simulink环境可近似为理想环境,因此我们将System Generator滤波结果与Simulink的滤波结果作对比。添加Digital Filter Design到model中,该block的配置界面与FDATool工具完全相同,对输入信号进行滤波。此时model如下:

将Digital Filter Design与Digital FIR Filter的滤波器参数设置为完全相同(20Mhz采样、1.5MHz通带截止、8.5MHz阻带截止、0.01dB通带衰减、100dB阻带衰减)。运行,理想情况(左)与System Generator的输出频谱对比如下:

可以看到System Generator设计的滤波器,由于数据格式、位宽的影响,与理想情况下的频谱结果并不完全相同。对于设计者而言,需要考虑的就是这种差异是否可以接受,即是否会影响到实际的系统性能。

9.3 不同字长定点数据的对比

如果System Generator和理想情况之间的差异不能接受,就该考虑修改设计。FPGA设计可以考虑使用定点数据类型(Fixed-point)或浮点数据类型(Floating-point),但后者消耗的资源几乎是前者的十几倍甚至更多,设计中通常都采用定点数据格式。

在System Generator再添加一组滤波器设计(可以复制粘贴),将Gateway In的数据格式设置为32-30Bits定点(32表示整体位宽,30表示小数部分位宽),与原来的16-14Bits定点数据格式作对比。此时的model如下:

如果运行后想观察整个model中的数据类型变化,可以在System Generator的General->Block icon display中选择“Input data types”或“Output data types”。运行完成后相关信息会显示在block上。

Fixed_32_30(右)与Fixed_16_14(左)的输出频谱对比如下:

可以看到提高了定点数的位宽后,计算精度明显提高,输出信号频谱与理想情况的频谱已经几乎相同。导出设计到FPGA,运行资源分析:

可以看到增加了数据位宽后,系统使用的FPGA资源几乎增加了一倍(FIR single与FIR fixed相比)。设计者需要在资源和性能之间衡量,选择最合理的设计。用类似的方法也可以比较不同滤波器系数位宽对FIR滤波系统的影响。

9.4 系统输出位宽选择

当使用Fixed_16_14格式时,FIR滤波器的输出位宽系统会自动设定为Fixed_36_33,这是全精度输出结果。而在FPGA设计中我们经常需要截位,否则位宽在整个系统中不断积累,大大增加资源的消耗。如何确定截取的位数呢?

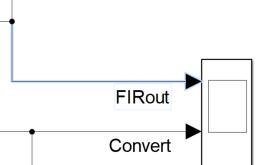

System Generator中有两个与此相关的block:Convert和Reinterpret,都可以进行数据的转换。Convert可以实现不同数据类型、不同位宽之间的转换,且可以设置量化和溢出的处理方式;Reinterpret可以实现数据类型之间的转换,还可以重新定义输出数据小数点的位置。

添加这两个block到model中,按下图连接:

使用Convert将FIR输出的Fixed_36_33数据转换为Fixed_16_13数据;使用Reinterpret将小数点重定位在第31bit(即数据放大4倍),具体配置可参考本系列第8篇。运行仿真:

从频谱图对比可以看出,经过Convert转换后,输出信号的频谱情况进一步恶化,设计者需要考虑截位是否会影响到系统性能。

使用Scope分别观察FIR输出、Convert转换后、Reinterpret转换后的信号:

可以看到Fixed_36_33和Fixed_16_13两种数据格式的信号波形几乎完全相同(第一和第二个波形)。Reinterpret由于将小数点从33bit重新定义到了31bit,相当于放大了4倍,输出信号的范围扩展为-4~4(Sine Wave block输出信号的幅度设置为1)。

将用作测试端口的Gateway设置为不作为output,导出到FPGA中后,滤波器输出位宽只有16Bits(第2篇没有截位的设计为输出36Bits)。

9.5 Scope使用技巧

在第2篇中已经介绍了如何用Scope观察多路信号,本文不再赘述。这里在介绍两个设计技巧:

设置显示范围

在View->Configuration Properites:Scope->Display中可以设置波形显示范围。Active display选择信号通道,设置Minimum和Maximum。点击Apply即可应用该设置。

设置信号名称

在Simulink模型中,双击接入Scope的连线,即可出现一个编辑框(同时线变为蓝色),输入的名称将作为Scope中波形窗口的title(也可以在上图中的“Title”编辑框中设置)。

10、Reinterpret和Convert详解

本文将对其中使用到的Reinterpret和Convert模块进行详细介绍。

10.1 模块功能概述

- 数据转换,数据类型、位宽等问题都会影响到计算精度,对于设计者而言,需要考虑的就是相关影响是否可以接受,即是否会影响到实际的系统性能。FPGA设计中还经常需要截位,否则位宽在整个系统中不断积累,大大增加资源的消耗。

- 数据类型的转换和截位是FPGA系统设计的重要内容,博主在《FPGA数字信号处理》系列的很多设计中都有详细讨论。而在System Generator设计中,完成这项任务的便是Reinterpret和Convert模块。

- 数据类型转换模块在导出到FPGA设计中(定点与浮点之间的转换、浮点与浮点之间的转换),会使用Floating-Point IP核实现,具体可参考《FPGA数字信号处理》,本系列不详细介绍。

10.2 Reinterpret block

10.2.1 block特性

这个block可以完成以下数据转换功能:

- 将无符号数转换为带符号数;

- 将带符号数转换为无符号数;

- 通过重新规定小数点位置来定义数据范围。

需要注意的是,“转换”在这个block中的含义更接近于其英文直译“重新解释”。事实上,数据在经过该block后,其位宽与每一位的值都没有发生任何改变,变化的只有其所表示的“意义”。正如博主在《FPGA数字信号处理》系列中强调的一样,一个二进制数是无符号数还是带符号数、小数点在哪一位仅仅取决于设计者如何规定和看待它。而Reinterpret改变的便是这种“规定和看待”方式。

比如,“1100”这个数,当视作UFix_4_0(无符号定点数、4Bits位宽、小数部分0bit)时,其值为12;当视作Fix_4_2(带符号定点数、4Bits位宽、小数部分2Bits)时,其值为-1。因为reinterpret实现的只是一种意义上的转换,因此其在转换为FPGA设计后,不会消耗任何资源。

既然reinterpret的输出和输入完全相同,那么加入此模块有什么作用?

- 从FPGA设计转换到Simulink环境中时会按设定的“意义”解析数据格式;

- 完成不同格式数据之间的的拼接。

10.2.2 参数设置

(1).选中“Force Arithmetic Type”后,输出数据格式的“意义”将转换为(没有选中,则输出与输入的表征意义相同):无符号数(Unsigned)、带符号数二进制补码(Signed(2’s comp))、浮点数(Floating-point)。

(2).选中“Force Binary Point”后,可以重新规定输出数据的小数点位置。比如设置为31时,表明数据中的低31Bits为小数部分。

10.3 Convert block

10.3.1 block特性

该block不仅可以完成数据类型的转换,还具有如下特性:

- 重新设置数据的量化、溢出方式;

- 重新设置定点数格式(进行数据截位)。

10.3.2 参数设置

其中大部分参数设置方法与Gateway In模块的设置完全相同,具体可参考本系列第5篇。这里只讲述两者不同的地方。

(1).Convert模块的量化方式可以配置为“Round(unbiased: even values)”,这是针对“四舍五入”量化方式的缺点所作的改进:

- 传统的四舍五入所有的中间值(如1.5、2.5)都会向更大的值量化,即不是完全对称的,这样会导致一组数据量化后平均值高于量化前的平均值。

- unbiased: even

values在处理中间值时会向更接近的偶数量化。比如1.5会量化为2;2.5仍然会量化为2(因为二者最接近的偶数都是2)。这样量化规则在整体上会呈现出对称性。

(2).选中“Provide enable port”后,block会增加一个en使能管脚,只有当使能有效时convert block才会执行数据转换功能,否则将保持当前状态不变。

(3).Latency设置了Convert输出数据要经过多少个采样时钟周期的延时。注意不要混淆“采样时钟周期”和“FPGA时钟周期”的概念,在过采样系统中,一个采样时钟周期可能等于多个FPGA时钟周期。

前文提到Convert在导出到FPGA中时会以Floating-Point IP核的方式实现,“Implementation”标签下可以设置Latency在FPGA中的实现方式:

●选中“Pipeline for maximum performance”时,Latency以流水线的方式实现,即在计算过程中增加中间级寄存器,以更多的资源实现更快的计算速度和更大的数据吞吐量。

●未选中“Pipeline for maximum performance”时,Latency以在IP核末尾增加一级移位寄存器的方式实现,这样只是单纯的实现了延时功能。