【转自微信公众号 智联网事】

本文介绍了RISC-V指令集从发布到目前的发展路程,及基于RISC-V的芯片研发进展及芯片配套软件开发生态的更新.

文章目录如下:

-

一些基本概念

-

RISC-V 二三事

-

RISC-V 有多强

-

ARM的担忧

-

基于RISC-V的芯片开发生态

-

一些市场的消息

-

个人看法

一些相关基本概念

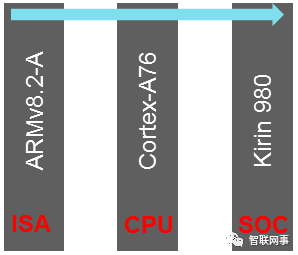

以麒麟980举例:华为的麒麟980是一款处理器(SOC, System on a chip),其基于ARM Cortex-A76微架构(CPU,Central processing unit),而Cortex-A76是基于ARM公司的ARMv8.2-A指令集(ISA,Instruction SetArchitecture)设计的。

从上面,我们引出了指令集的概念。 指令集作为硬件和软件的一个接口,是对计算机的抽象描述。知名的指令集有ARM、PowerPC、X86等,国内也有自主产权指令集的公司,如被阿里收购的中天微。更多关于ISV,CPU和SOC的描述,请参考文章 谈谈ISA,CPU和SOC。

RISC-V二三事

RISC-V (pronounced “risk-five”) is an open, free ISA enabling a new era of processor innovation through open standard collaboration. Born in academia and research, RISC-V ISA delivers a new level of free, extensible software and hardware freedom on architecture, paving the way for the next 50 years of computing design and innovation.

RISC-V指令集,是加州大学伯克利分校于2011年发布的开放免费指令集,由于是第五代,因此取名RISC-V。在如今ARM大行其道,从芯片到生态到终端用户都齐全的时代,RISC-V这样一个指令集,究竟如何生存壮大起来的?它有哪些特点优势? 这也是我尝试了解回答的问题。 (只想看总结的可往下速滑)

记得十年前的手机品牌,诺基亚,摩托的,索尼等,各自的系统都不一样,现在大家用的手机,除了苹果,基本都是基于安桌系统。安桌的两大特点是开源和免费,这样不仅给广大应用开发者很大的灵活度,而且发展了非常丰富的生态。Android的开发者GOOGLE, 也是RISC-V的白金会员之一。 RISC-V的研究团队认为,指令集ISA作为软硬件接口的一种说明和描述规范,不应该收费,而应该开放和免费。这也是RISC-V创造者的初衷之一。

当然,仅仅具有开源和免费也是完全不够的,就如工作,有一个好的主意,没有任何配套的行动,策略,主意永远是一个概念。一个产品能不能用,好不好用,能否给终端应用厂商,给市场带来价值?针对这些质疑,RISC-V伯克利研究团队从下面几方面开干:

-

第一招 基于指令集推出CPU及芯片原型

这直接将RISC-V的指令落地到终端可以使用,评测的芯片。这一过程,不仅仅将理论,概念实体化,解决了许多技术上的问题及挑战,而且也带动建立了研发SOC的生态。这大大降低了RISC-V用户的开发难度,成本,风险。

-

第二招 成立非盈利组织RISC-V基金会,加快生态建设

RISC-V基金会自2015年成立以来,会员数目增长如图,不可谓不猛。

且从其会员构成类别看很丰富。截至2018年3Q, RISC-V 基金会已发展115个会员,其中包含 NVIDIA, QUALCOMM, NXP, SAMSUNG,HUAWEI这样的超一流大厂,许多一流学术机构及C SKY,SIFIVE等商业化IP公司。

除了上诉的CPU SOC开发相关,成员还包括IAR,SEGGER,TSMC等应用开发,芯片生产相关的企业!

第三招积极开“大”会

2015年 RISC-V第一次全球研讨会举行,截至2017,已经举行七届。除了全球的研讨会,还包括在全球各地举行的专项研讨会。这些会议给RISC-V的爱好者,使用者提供了很好的沟通,分享,交流平台,促使RISC-V的加速发展。

如下,我们以时间的角度梳理下RISC-V的发展

-

2011年 发布开放指令集RISC-V,随后基于RISC-V的ROCKET IP成功流片

-

2015年 发布BOOM IP

-

2015年 RISC-V创始人成立SIFIVE,加速推进RISC-V商业化

-

2017年 基于BOOM IP的芯片流片

-

2015年 RISC-V 基金会成立,加速RISC-V的指令集规范的演进以及软硬件生态系统的发展

-

201x年 更多消息请往后看

总结来说,RISC-V 以开放,免费的模式,从基础指令集落地到芯片,赋能客户,广建生态,积极扩大影响,集结了强大的联盟。

与ARM的恩仇录

如果老大哥看也不看你,说明你太弱了。RISC-V的快速发展也引起了来自ARM的关注及担忧。2017年6月,ARM建立了一个专门的网站,从成本,生态,碎片化风险,安全及设计验证等方面指点RISC-V。在RISC-V反击发布后,ARM主动关闭下线了网站。(相关资料可从下面链接获取 https://github.com/arm-facts/arm-basics.com/blob/master/index.md)

第一刀 成本

ARM:虽然RISC-V 指令架构集(ISA)开源,免费,但是ISA的授权只占有商业处理器总成本的一小部分

RISC-V:显性成本你这么贵,却谈说不清楚的隐性成本。而且我们通过开放,吸引更多贡献者来完善设计,这也有利于降低研发成本。

第二刀 生态

ARM:针对一个指令架构,能有一个全球化的,成熟的,覆盖软件,服务,涉及支持等的生态,是非常重要的。而RISC-V目前的生态还不够

RISC-V:谁没有喝奶的时候,我们正在飞速的发展完善中。

第三刀 碎片化风险

ARM:由于RISC-V的指令集架构允许CPU IP 供应商定制化,这种“碎片化”可能使得ISA的生态兼容性更加困难。

RISC-V:你自己已经碎片化了,ARM ISA (ARMv6/7/8, Thumb1, Thumb2, ThumbEE,Jazelle, ARM v8, v8-M, NVIC/VIC/GICv2/3/4等)。而我可以在开始阶段就可以到如何更精简。

第四刀 安全

ARM:网络威胁需要芯片具有很好的安心性能。基于RISC-V的产品目前还比较新,有待专家及其合作伙伴的观察。

RISC-V的:自己的屁股没擦干净(ret2usr问题),而RISC-V可以在设计的最初,而且也正是RISC-V的安全组正在做的事情。

第五刀 设计验证

ARM:IP的设计过程,验证及确认可能占总设计时间的75%。而RISC-V的ISA允许修改,可能带来昂贵的验证ueren成本及对应的软件工具定制化费用。这都将增加设计的成本。

RISC-V:开源,可以借助更多的专业力量参与设计的过程,这有利于加速开发和降低成本。

我们可以看到ARM提出的点,其实也正是RISC-V开始就考虑到且在减小影响的点。截止目前,基于RISC-V的开源免费CPU及SOC原型已经不少。后面会提到。

RISC-V性能情况

截止目前,伯克利的研究团队公布了基于RISC-V的Rocket以及BOOM两个CPU。其CoreMark性能情况如下图。

在论文《RISC-V Compiler Performance:A comparison between GCC and LLVM/clang》 中,我们可以看到实际基于RISC-V的芯片和ARM的对比结果。可以看到,在编译器开启O1以上优化情况下,RISC-V的性能可以做到和ARM接近。这是实际的跑分结果。和网友在SIFIVE的开发板上的结论相近

RISC-V的芯片开发生态

我们先看下,芯片开开发需要的基础工具:编译器,调试器,软件开发包

编译器方面:SiFive 公司已经提供FreedomStudio,另外,还有GCC Toolchain, GNU MCU Eclipse也有对RISC-V的支持

调试器方面: Lauterbach及Segger已经支持RISC-V,而IAR也宣布2019年将提供RISC-V的支持。

软件开发包:SiFive针对其Freedom ESDK,而系统方面,Linux 4.15官方内核将支持RISC-V

可以看出,基于RISC-V的芯片的开发工具链也是越发完善。