概述

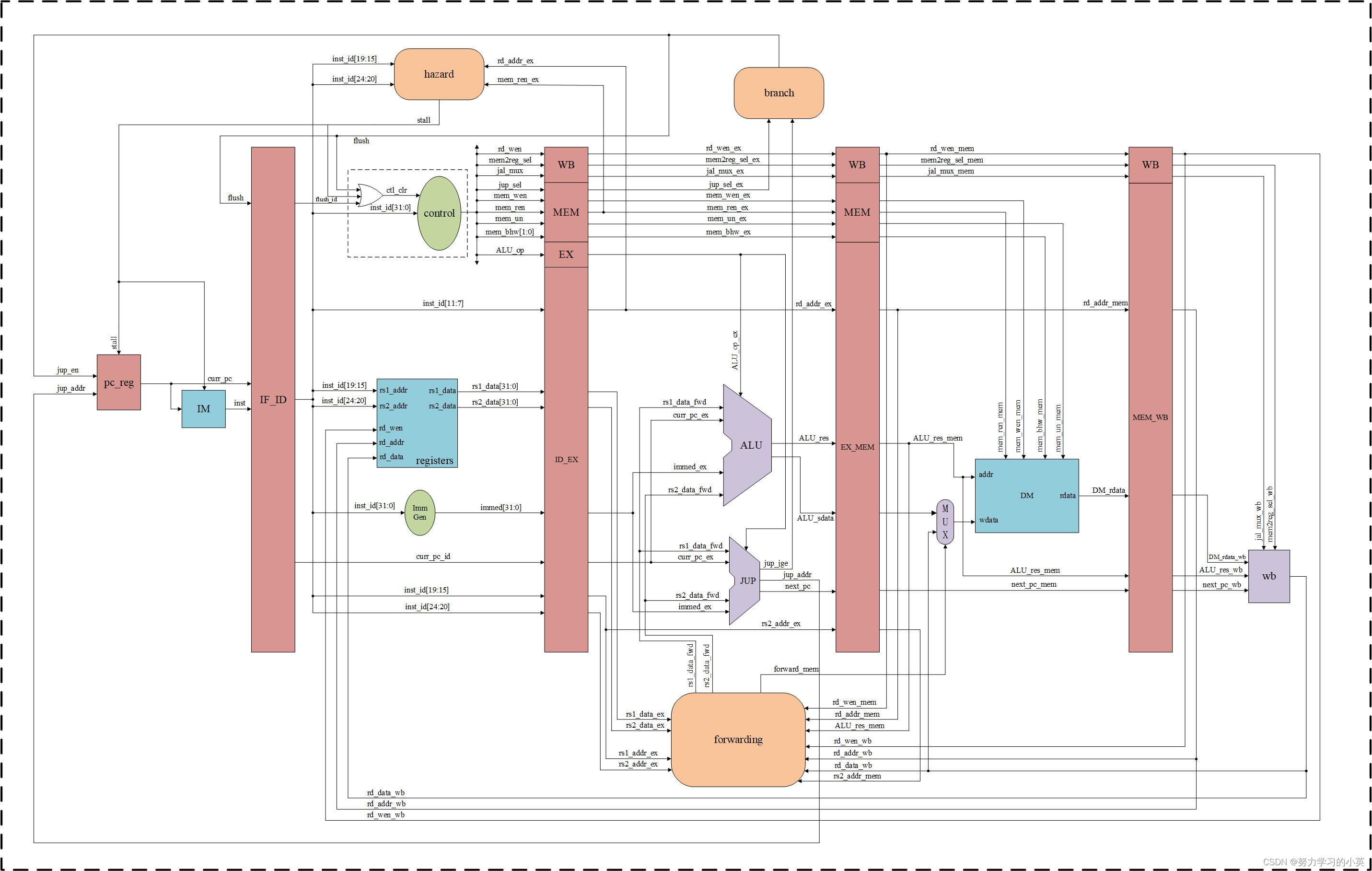

2022年暑假的时候开始接触到RISC-V,一开始只是照着《计算机组成与设计RISC-V版本》这本书写了一个五级流水线32位单发射的RV32I处理器,写的很简单,其流水线结构示意图如下:

是一个比较典型的取值、译码、执行、访存和写回处理器,实现了RV32I的所有指令。但对于真正的RISC-V处理器来说,这些可能还很皮毛。所以最近准备更深入的了解一下RISC-V。

首先来了解一下RISC-V的指令集架构发展史:

- RISC-V V1.0: RISC-V V1.0发布于2011年,是最早的RISC-V版本,该版本定义了基本指令集,包括32位和64位两种版本,以及一些可选的扩展指令集。该版本主要面向嵌入式系统等应用。

- RISC-VV2.0: RISC-VV2.0发布于2014年,是在V1.0基础上的扩展版本。该版本增加了原子操作指令集(A) 、浮点指令集 (F)等扩展,同时也对基本指令集进行了修订和优化。

- RISC-V V2.1: RISC-V V2.1发布于2016年,是在V2.0基础上的修订版本。该版本主要修正了V2.0中的一些错误,并增加了一些新的指令。

- RISC-V V2.2: RISC-V V2.2发布于2017年,是在V2基础上的修订版本,该版本主要修正了V2中的一些借误,并增加了一些新的指令和扩展,如压宿指令集 (C) 和向量指今集 (v) 等

- RISC-V V23: RISC-V V2.3发布于2019年,是在2.2基础上的修订版本,该版本主要修正了22中的一些错误,并增加了一些新的指令和扩展,如密集型计算指令集 (B) 和加密扩展指令集 (E) 等。

- RISC-V V2.4: RISC-VV2.4发布于2020年,是在V23基础上的修订版本,该版本主要修正了V23中的一些错误,并增加了一些新的指令和扩展,如内存扩展指令集 (Z) 和人工智能扩展指令集 (N) 等。

可以看到RISC-V还是一个非常年轻的指令集架构,同时其十分瞩目精简、开源的特性也十分有利于我们学习,所以在未来的一段时间内,将把主要精力放在对RISC-V的指令集架构,包括基本指令集和拓展指令集的学习,不定时在此更新,大家有兴趣的话可以点进主页在RISC-V栏目里看到相关内容~~

另外,本文即后续所有对RISC-V指令集的学习除非特别说明都仅针对V2.1版本。

最后列出一些RISC-V的相关基本可拓展指令集:

- RV32I/RV64I:基本整数指令集,包括整数的算术、逻辑、移位、比较和控制指令。

- RV32M/RV64M:乘法扩展指令集,添加了基于32位或64位整数的乘法和除法指令。

- RV32F/RV32D/RV64F/RV64D:浮点扩展指令集,包括单精度或双精度浮点数的算术、转换、比较和控制指令。

- RV32A/RV64A:原子操作扩展指令集,支持原子读-修改-写操作,用于多线程同步。

- RV32C/RV64C:压缩至零扩展指令集,将常用指令压缩为16位指令,可以减少指令存储空间。

- RVV:向量扩展指令集,支持向量化计算,以提高向量计算的效率和性能。

如果不出意外的话,将对上述的扩展指令集逐一学习、介绍。