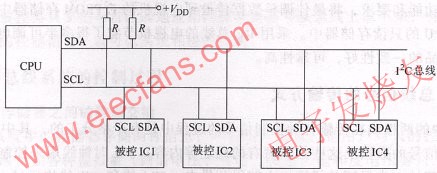

1.I2C总线架构图:

2.Gemini Lake 平台所支持的PMIC 是哪种类型?

POR 是SVID PMIC, i2c PMIC 会影响性能。

3.SerialVID, 总共有三个信号线 时钟(clock) , 信号(data) Alert (报警) 组成的。 是一种串行同步接口。

4.VID(Voltage Identification,电压识别)是一种电压识别技术,装上不同的CPU,会产生不同的电压。

VID可分压PVID(并行VID)和SVID(串行VID)。

VID(Voltage Identification)是一种电压识别技术,可分为PVID(并行VID)和SVID(串行VID)。

在AMD早期和INTEL 5系列芯片组之前,都采用PVID,其基本原理就是在CPU上设置了4-8个VID 识别脚,并通过预设在这些识别脚上的高低电平值,形成一组VID识别信号,这些信号传输到CPU供电电路中的电源管理芯片后,电源管理芯片根据所得到的VID信号使CPU供电电路输出的电压与预设的VID所代表的值一致。

AMD从AM2+ CPU开始,CPU包含两部分电压,一是CPU的核心电压,另一是CPU内集成的北桥的电压。并行VID控制模块无法在同一时间内异步控制这两种电压,除非再提供一组并行VID控制CPU中的北桥电压,但这样会增加芯片的复杂度。于是AMD率先推出新一代电压调节模块规范,采用串行VID(SVID)模式来解决这一问题。串行VID是一种总线类型的协议。从硬件上来看,所需要的外部接口由以前的多个VIDXX引脚变成SVC(串行时钟)、SVD(串行数据)两个引脚,简单了很多。不过,串行VID的实现需要软件的配合。

传统便携式笔记本、一体机、台式机等一般都是采用intel的技术架构。其待机、休眠、高负载环境下的电压调节都有一套成熟的应用方案,英特尔从6系列平台开始,导入VR12(VoltageRegulator电压调节)规范,也就是SVID(SerialVoltageIdentification串联电压识别)模式,通过CPU自身SVID总线侦测CPU的电压,即CPU作为PMBUS(PowerManagementBus电源管理总线)的主设备,SVID模块通过DATA(数据)和CLK(时钟)总线向VRM(VoltageRegulatorModule电源管理模块)芯片发出呼叫,等待着VRM芯片来读取电压设置信息。当VRM芯片对CPU内SVID模块的呼叫做出应答,并读出电压设置信息,CPU主供电VCORE(VoltageCore核电压)产生,之后依据CPU电压来调控PWM(PulseWidthModulation脉宽调制)供电的相数。硬件电路和通信机制都已经形成一种固定机制,每一系列的CPU主板必须兼容相应的PWM控制器,由于CPU和VRM必须通过SVID总线进行通信,而SVID是一种总线工作模式,整个链路需要软件的配合,硬件成本较高。

VID调节CPU电压

VID(Voltage Identification,电压识别)是一种电压识别技术,装上不同的CPU,会产生不同的电压。VID可分压PVID(并行VID)和SVID(串行VID)。

在AMD早期和INTEL 5系列芯片组(HM55等)之前,都是属于PVID,其基本原理就是在CPU上设置了4-8个VID 识别脚,并通过预设在这些识别脚上的高低电平值,形成一组VID识别信号,当VID识别脚上为高电平时,则为二进制的1状态,当VID识别脚上为低电平时,则为二进制的0状态。根据这些1与0的组合,就形成了一组最基本的机器语言信号,并由CPU传输到CPU供电电路中的电源管理芯片,电源管理芯片根据所得到的VID信号,调整输出脉冲信号的占空比,迫使CPU供电电路输出的直流电压与预设的VID所代表的值一致。

INTEL公司为其不同时间生产的各款CPU制定了相应的电压调节模块(Voltage Regulation Model——VRM)设计规范,从Prescott核心微处理器开始,电压调节规范改用VRD(Voltage Regulation Down)来命名,在笔记本电脑中,使用的是移动电压配置IMVP(Intel Mobile Voltage Positioning),各版本供电设计规范中的VID位数、电压调节精度和电压调节范围都各不相同。

这种模式的VID,可以通过装入假负载把CPU电压”骗”出来:当装上假负载后,将VID0-VID7其中的一个或多个VID信号接地,此时电源IC的VID0-VID7引脚上就得到了新的电压组合,电源IC会根据这个不同的组合,控制发出相应的电压。也就是说,让CPU供电芯片误以为是真CPU装入。

由下表可以看出,伴随着VRM/VRD/IMVP标准的增高,VID位数在逐渐增加,电压调节精度变小,电压范围也随之变小。

使用PVID的芯片,引脚上必然有VID*信号,如下图ISL6262芯片中37-43脚:

AMD从AM2+ CPU开始,CPU包含着两部分电压(AMD称之为Dual-Plane),一个是CPU的核心电压,一个是CPU内集成的北桥的电压,一组并行VID控制模块无法在同一时间内异步控制这两种电压,除非再提供一组并行VID控制CPU中的北桥电压,但这样会显得比较复杂。于是AMD率先推出新一代电压调节模块规范,采用串行VID(SVID)模式来解决这一问题。串行VID是一种总线类型的协议。从硬件上来看,所需要的外部接口由以前的VID0~VID5共6个变成SVC(串行时钟)、SVD(串行数据)两个,可以说是简单了很多。不过,由于串行VID是一种总线工作模式,所以需要软件的配合,但同时也意味着后期调整的可操作性会更强。前期大部分AMD主板为了兼容AM2/AM2+/AM3,采用了PVI/SVI兼容的PWM控制器。

英特尔在5系列平台搭配的Core i3/i5/i7 CPU集成了显示核心,为了更好地控制这两组电源,因此提供了两组PVID接口以分别控制CPU的核心电压和显示核心电压,这两组电压都符合英特尔 VRD11.1的规范,这显然是稍显复杂了一些。

英特尔从6系列平台开始,导入VRD12规范,也就是串行VID模式,和AMD SVID模式如出一辙。INTEL平台的SVID有三根线:SVD(串行VID数据),(SVC串行VID时钟),ALERT#(警示信号)。采用SVID的电源管理芯片,引脚上必须有这几个信号。如下图芯片4-6脚:

下图为INTEL平台SVID信号波形截图,黄色线为SVC信号,蓝色线为SVD信号。

根据INTEL 6系列芯片组收据手册得知,CPU是在获得了PROCPWRGD后,才发出SVID信号,INTEL 6系列标准时序图截图:

所以,新的6系列及以后的主板,如果出现没有CPU供电的情况,应使用示波器抓取CPU是否发出SVID信号给电源管理芯片。

如果没有波形,则应按照时序图先查CPU是否获得PROCPWRGD这个高电平信号,若PROCPWRGD不正常,需要追查PCH的相关PG信号,以及PCH是否追查读取BIOS等。

另外,CPU内集成显卡的供电是在CPU核心供电出来之后才产生。同样是由SVID控制。