写这个博客的原因是看到了这个题:

时钟周期为T,触发器D1的时钟沿到来到触发器Q变化的时间Tcq(CLK--Q)最大为T1max,最小为T1min,逻辑组合电路的延迟时间最大为T2max,最小为T2min,问触发器D2的建立时间和保持时间。

之后又在面试时候又被问到了相关的问题,因此想要总结一下。

什么是保持时间(hold time)?保持时间就是指的对于一个触发器来说(如下图的D触发器),在时钟信号上升沿到来以后,数据要稳定不变的时间。在一些试题中这个意思有点混淆,例如描述一个信号可以说他的保持时间是多少,也可以描述一个触发器的保持时间是多少那么此时指的就是如果数据想要被打入触发器,信号的保持时间需要满足的保持时序条件。如果信号不满足保持时间(其保持时间低于最低要求),那么信号将如无法被打入触发器。

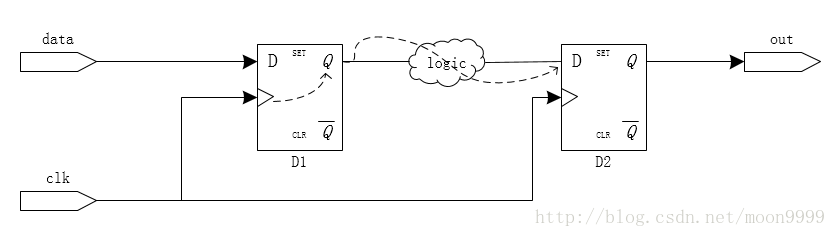

如何要保证信号能够打入触发器,那么一个触发器保持时间的范围是什么呢?来看下图,里面涉及了几个时序:时钟沿到来到触发器Q变化的时间Tcq,就是时钟沿采好了D的值到把这个值传到Q使Q跳变的时间;辑组合电路的延迟时间Tcom(图中用logic表示了,这两个一个意思吧);时钟周期T(虽然最后没用他);当然还有对于触发器D端口的保持时间Thold。我们要计算的是D2触发器的保持时间范围。(下图的out画反了,悲伤)

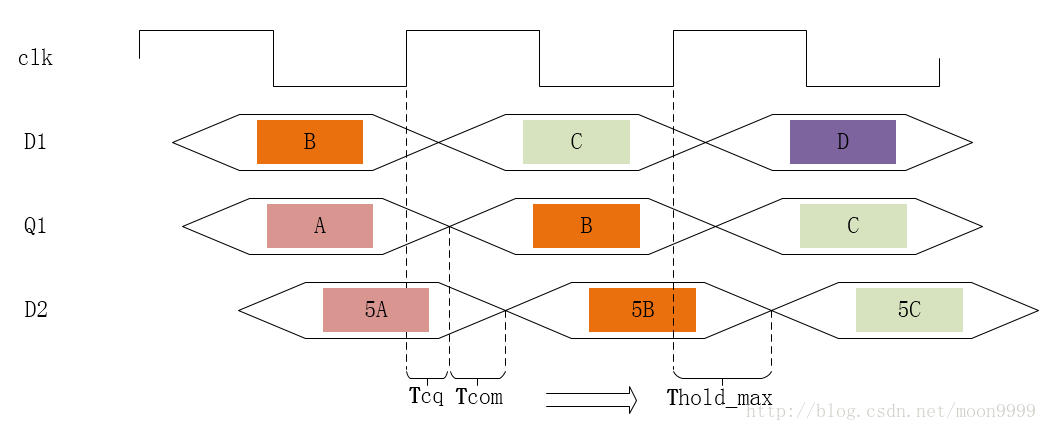

现在让我们来思考这个事情,什么时候D2触发器当前的信号输入会发生改变呢?比如说此时上升沿采样开始采样,D2(D2寄存器的D输入端)的数据是5A,那么当D1触发器成功的把数据传出即D1->Q1,并且Q1信号经过了组合逻辑的延时后,就会到达了D2端,那么D2的数据必然就会发生改变(Q1->logic->D2),对于其信号来讲也就是保持时间结束了,那么寄存器的保持时间要求必须要小于这个时间。然我们看看时序图就懂了。

如上图我们看B信号。在第一个时钟上升沿,clk对D1xz.net进行采样,之后花了Tcq的时间把B传给了Q1,之后Q1经过了Tcom的时间走过了组合逻辑(信号变成了5B)到达了D2端。也就是说对于D2端口来说,他的数据会在时钟沿的(Tcq+Tcom)时间后发生变化,仔细看图就应该可以看出来的,因此我们可以得出结论:D2触发器的保持时间应该满足Thold<Tcq+Tcom。

这样还不完全,鉴于触发器和组合逻辑的延时都有一定的波动范围,因此要写为:Thold<(Tcq+Tcom)min。

继续问保持时间余量(hold time stack)的话,就比较简单了:

hold time stack = Tcq+Tcom-Thold 即可。

继续看,现在我们把时钟偏移引进来。

那么当把时钟偏移纳入考虑范围时,就要对上面的公式进行修正。我们看下如果寄存器D1的时钟偏移了的话(自然是向后为正了),对保持时间是有利的,因为Q1跳变的时间变晚了嘛;而D2的时钟偏移了的话,对保持时间是不利的,因为采样的时间变晚了,D2信号就得保持更长的时间才可以。因此将公式修正如下:

hold time stack =(Tclk_d1s+ Tcq+Tcom-Tclk_d2s)-Thold

有时记Tclk_d2s-Tclk_d1s=△T,因此记为:

hold time stack = Tcq+Tcom-△T-Thold

可见△T>0太大了的话是不行的,造成保持时间违例。而△T<0太小会是建立时间违例,最好还是使用质量好的同步时钟吧,让△T=0是最好的了。