记录TJU第一次数电课的实验,老师提供下去的使用的是vivado2017.2 版本的安装包进行编程实验,由于往届所用的编程环境都没有在window10 环境下运行,所以在此写一篇博客记录,顺便把我们第一节课相关的小项目的编译,运行过程也记载下来。

VIVADO2017.2安装包链接: https://pan.baidu.com/s/1dqyGkY 密码: gjf9。里面有安装教程,安装教程里的版本为免费版本,不需要license。

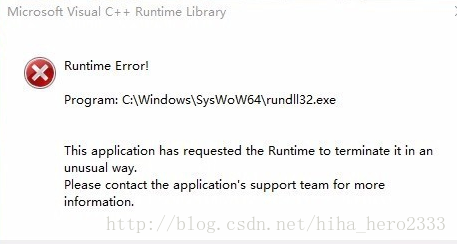

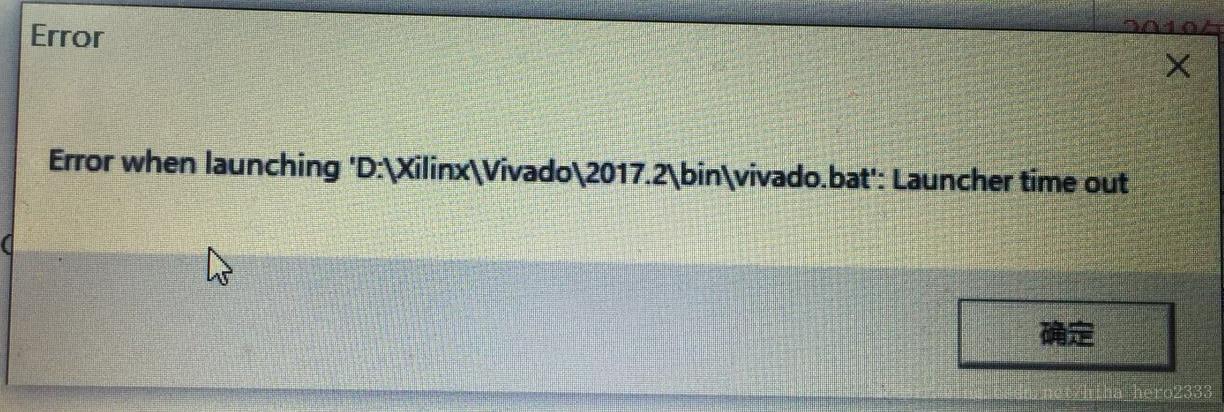

我这里使用的是win10的系统,跟着安装教程傻瓜式安装,在安装完成以后,在桌面上会自动产生“vivado 2017.2” 和“vivado HLS2017.2” 这两个快捷方式,我在双击vivado 2017.2 这个文件,会提示错误:

google一下马上找到了解决办法:

https://forums.xilinx.com/t5/Installation-and-Licensing/runtime-error-vivado-2017-2/td-p/807780

https://www.xilinx.com/support/answers/69908.html

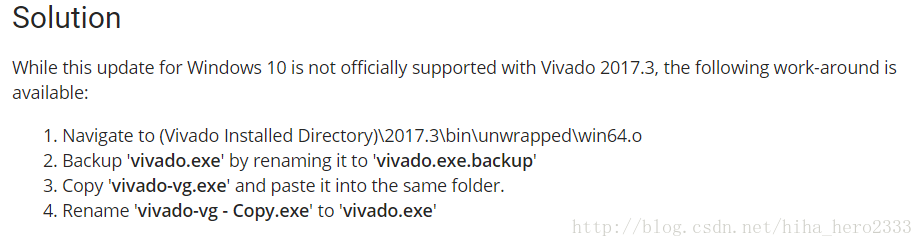

中文意思就是win10官方不能很好地支持vivado2017.3,我们找到安装vivado的目录

- 在 (Vivado Installed Directory)\2017.3\bin\unwrapped\win64.o路径下

- 找到vivado.exe文件,重命名为vivado.exe.backup.

- 再找到vivado-vg.exe,复制一份副本,重命名为vivado.exe

- 接下来打开桌面图标就可以了

(我亲自尝试,成功了)

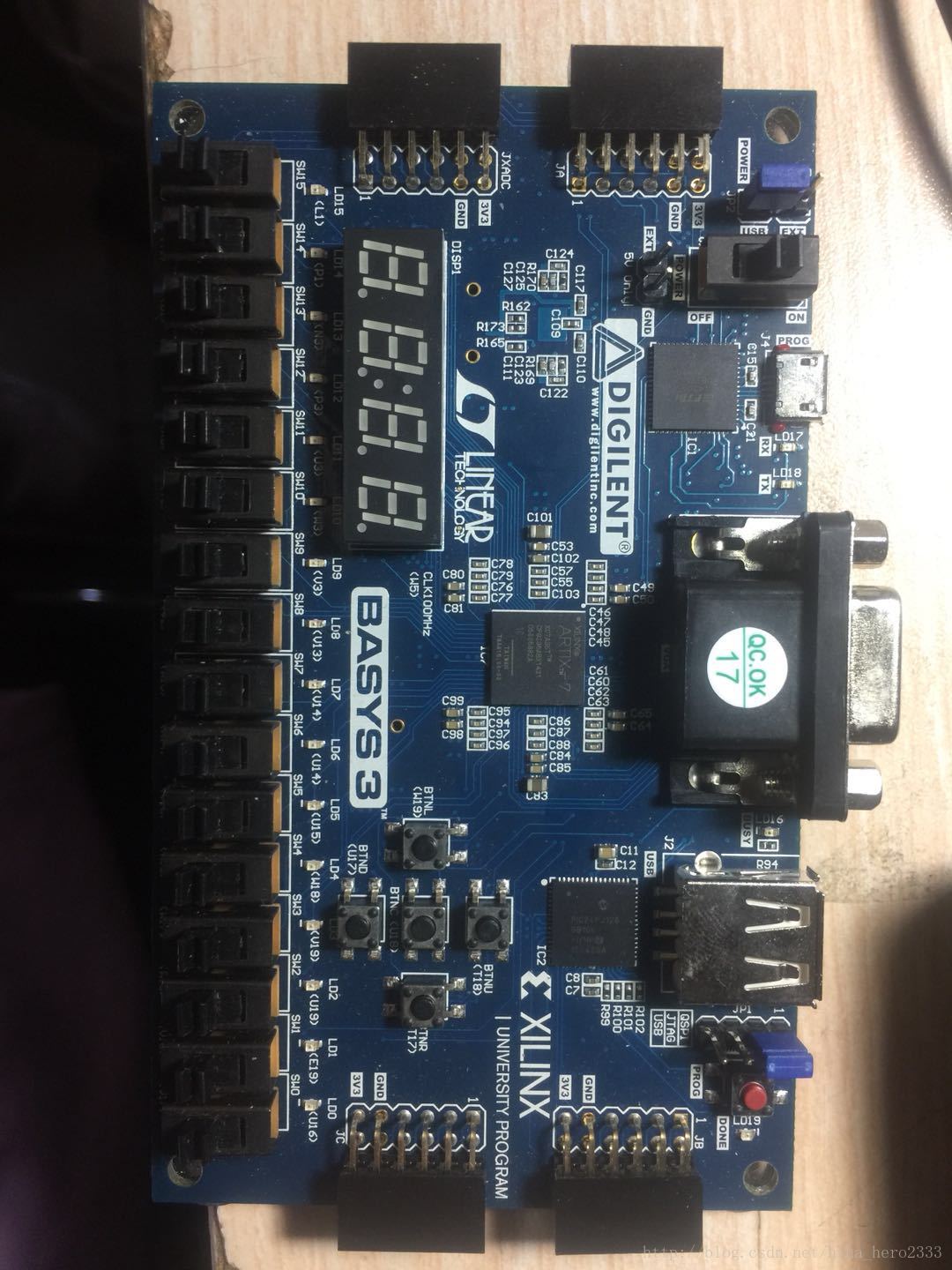

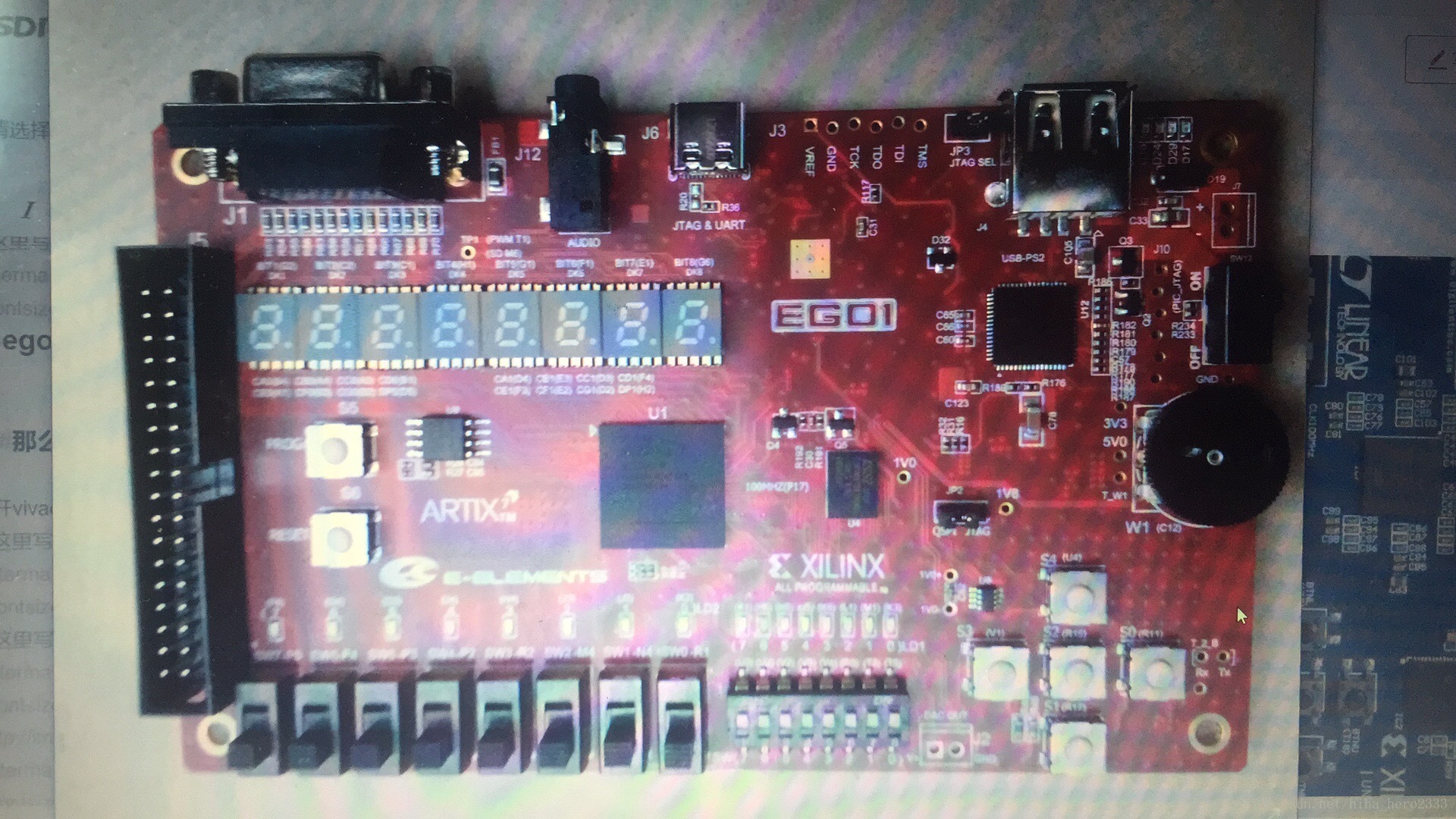

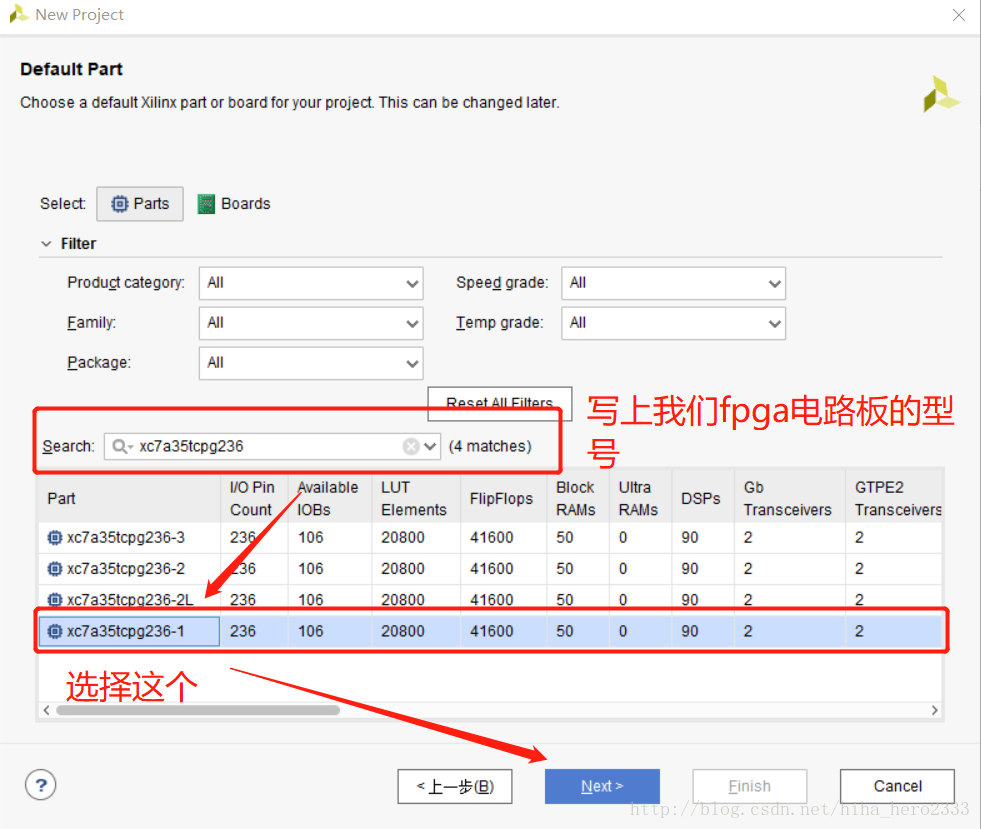

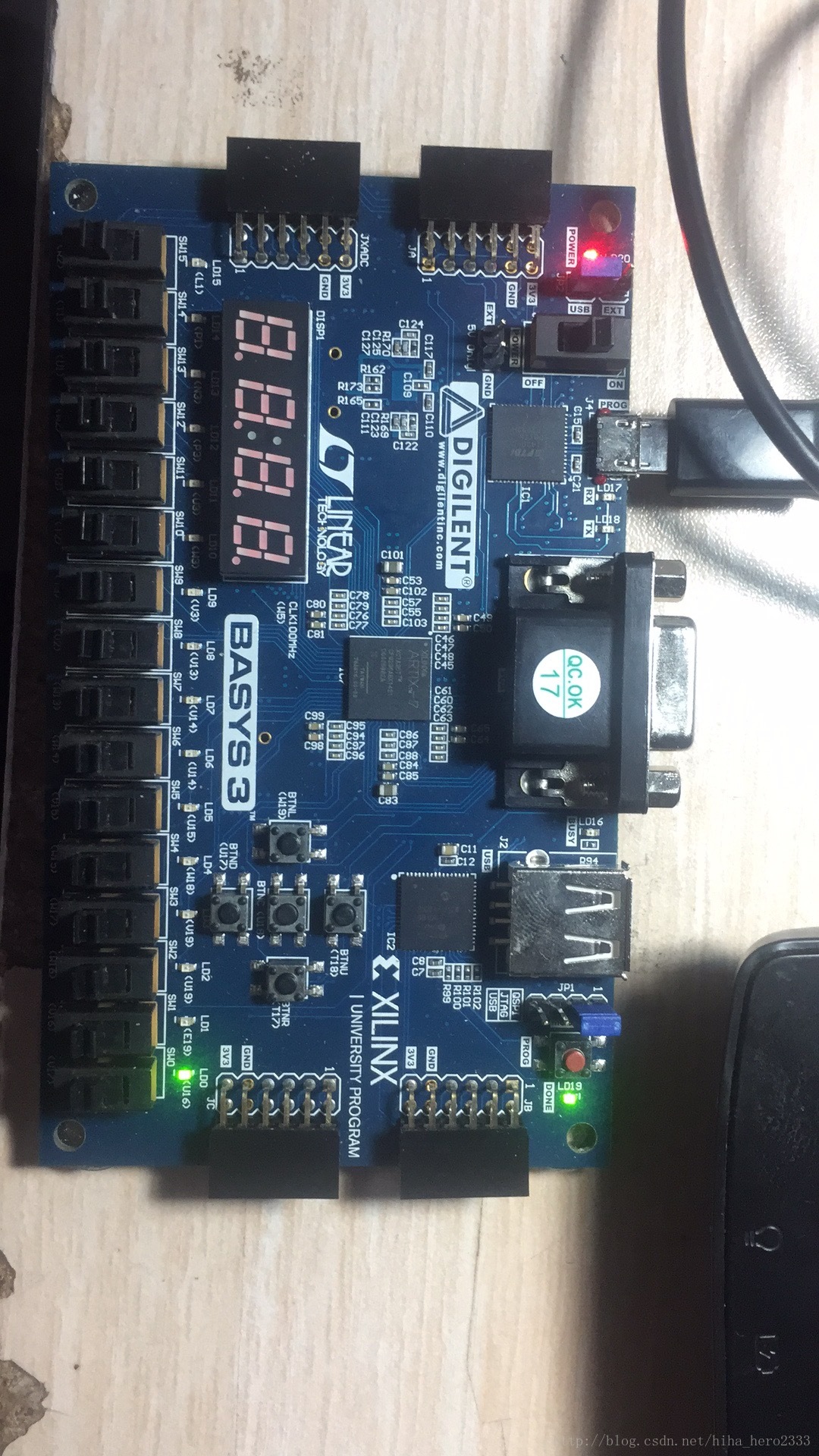

我们整门课程将会用到的两个板子:

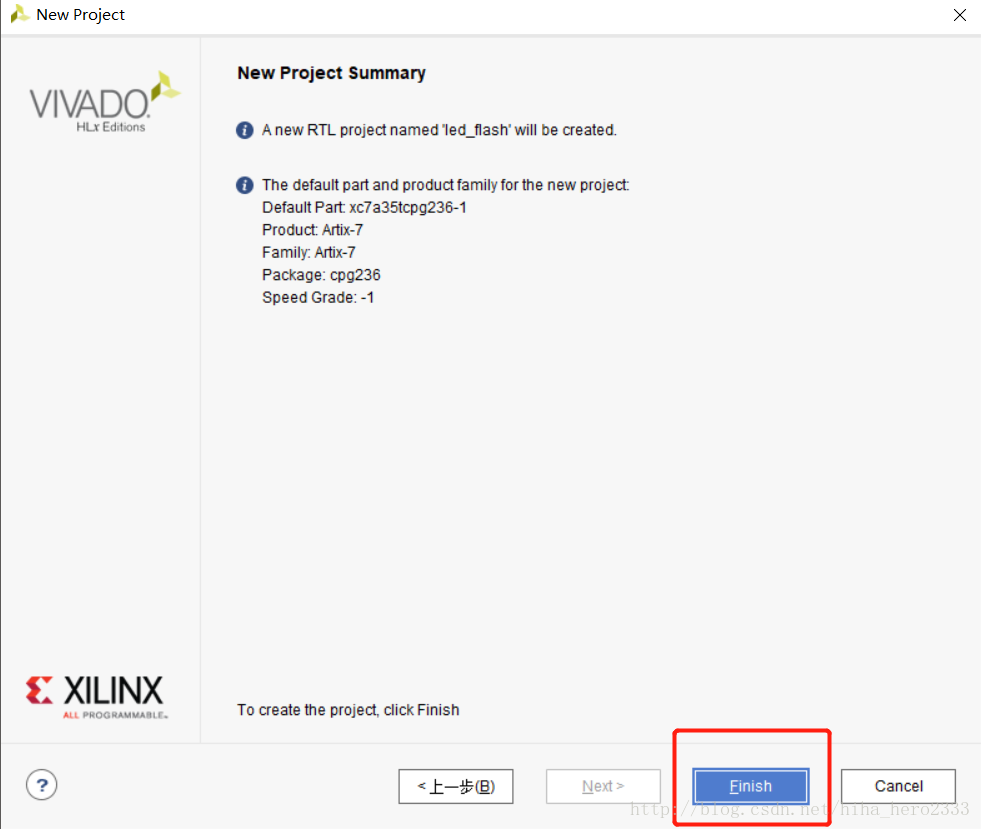

BASYS3 蓝色板子 型号:xc7a35tcpg236-1

ego1 红色板子 型号: xc7a35tcsg324-1

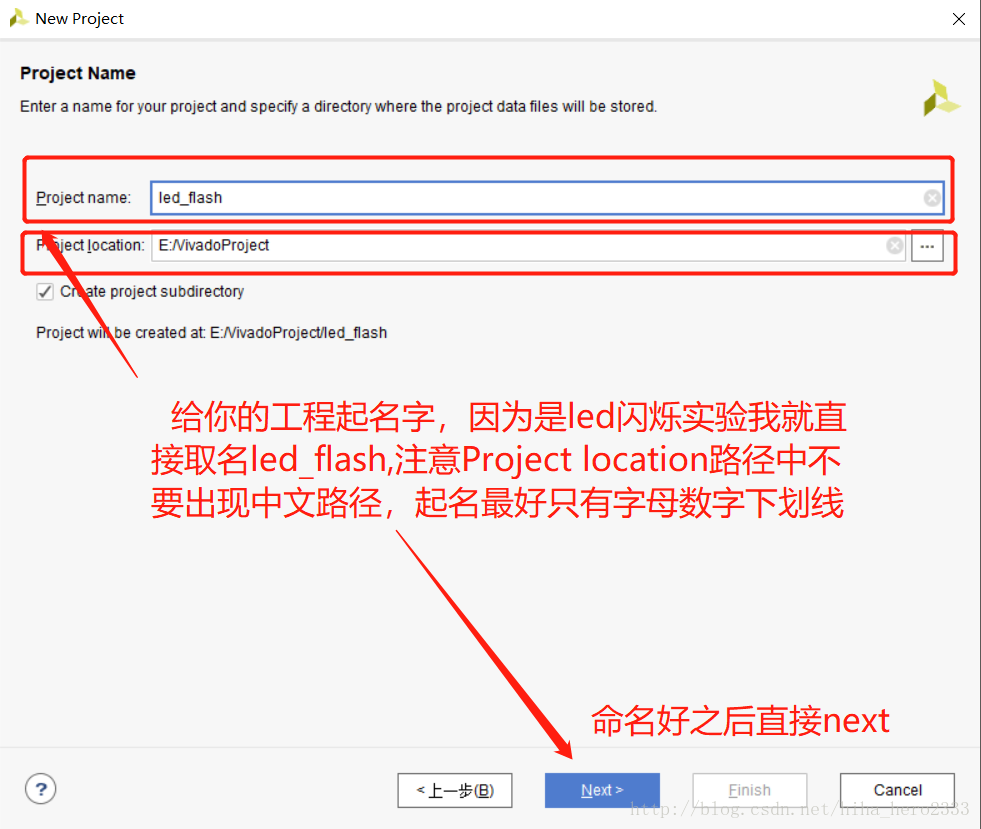

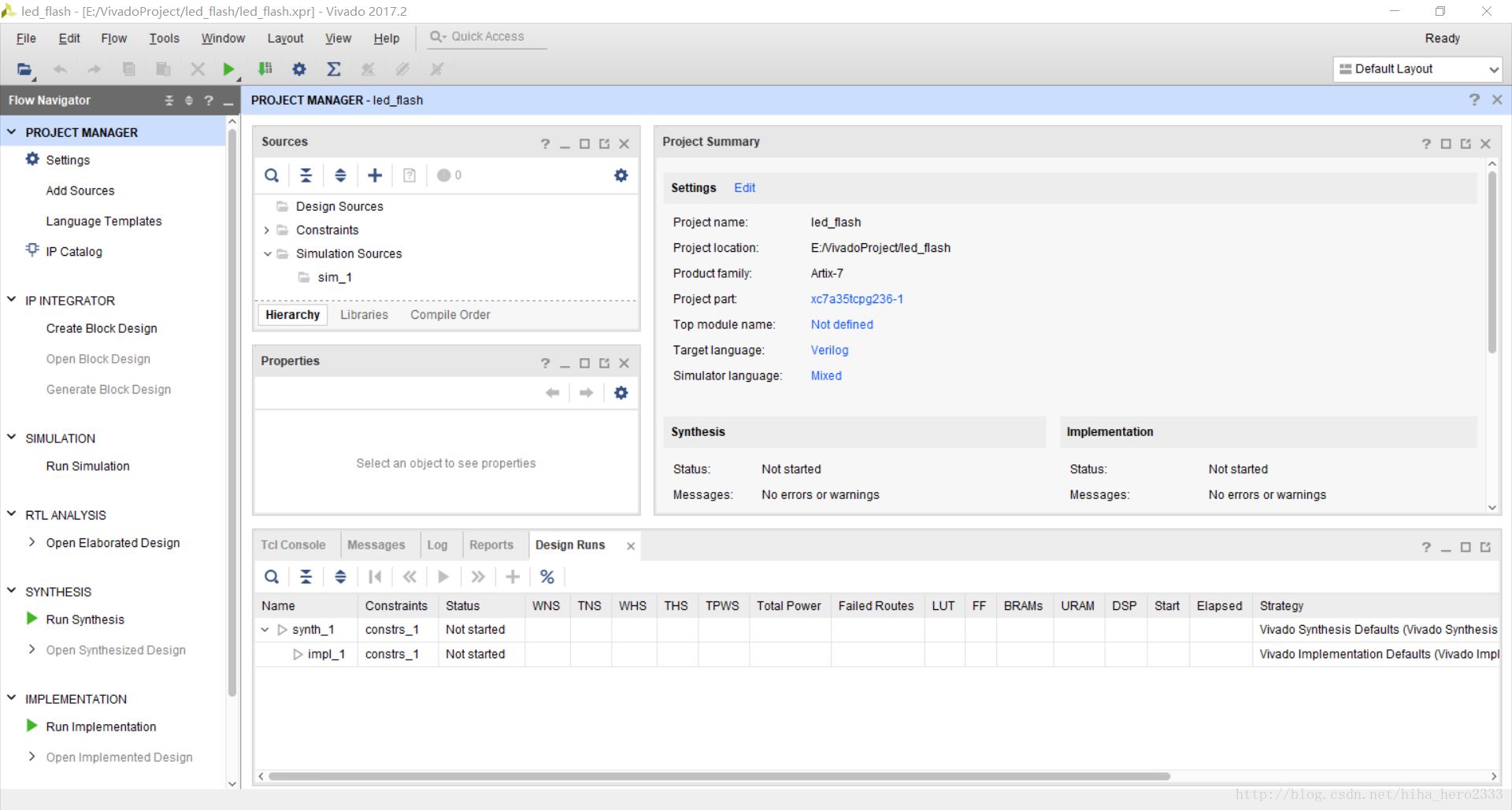

那么接下来就是一步一步构建工程,制作我们第一个数电实验——led闪烁实验

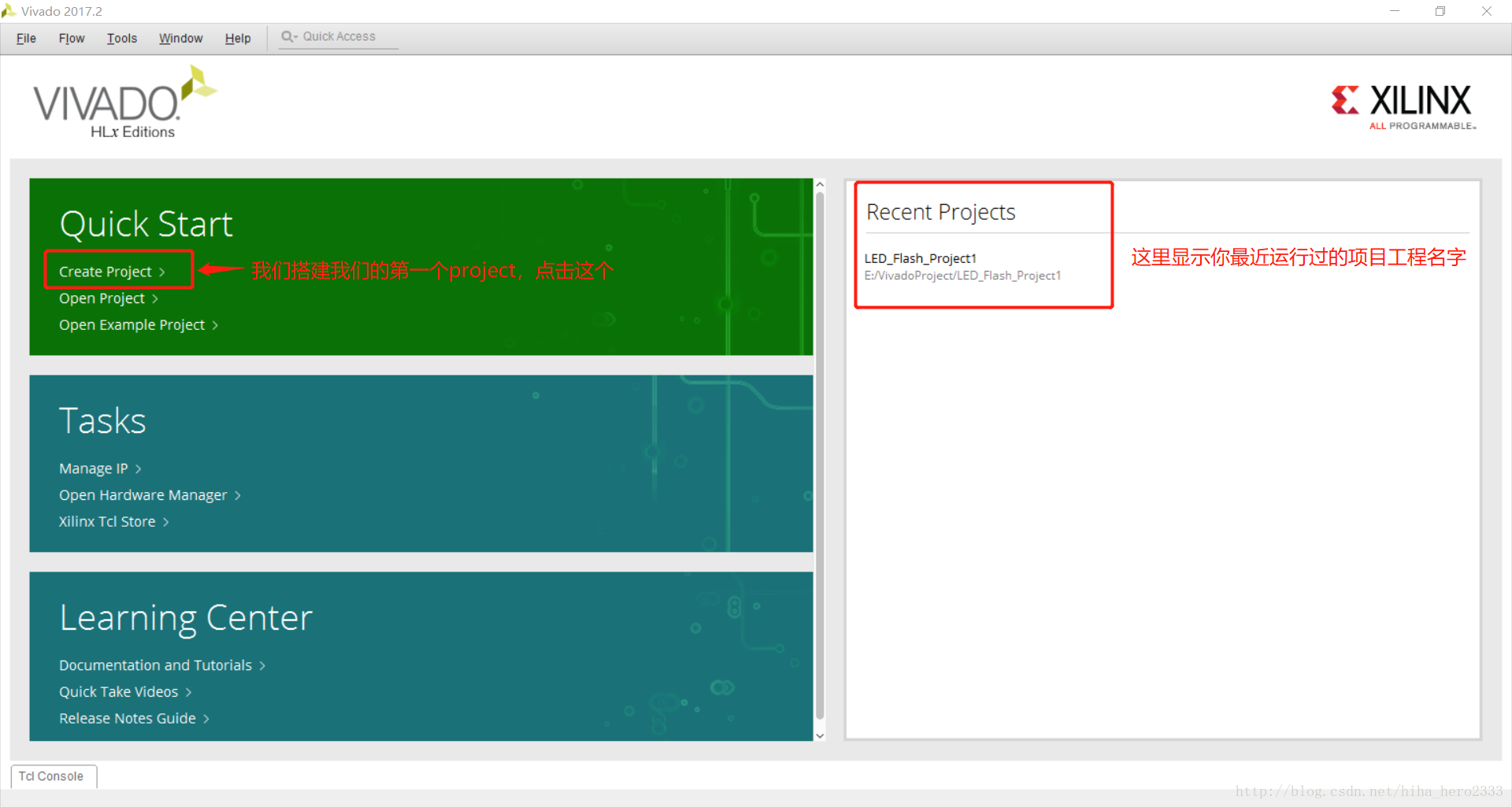

打开vivado

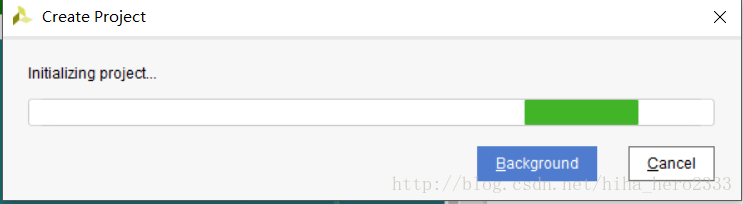

接下来我们就可以看到它在初始化工程了

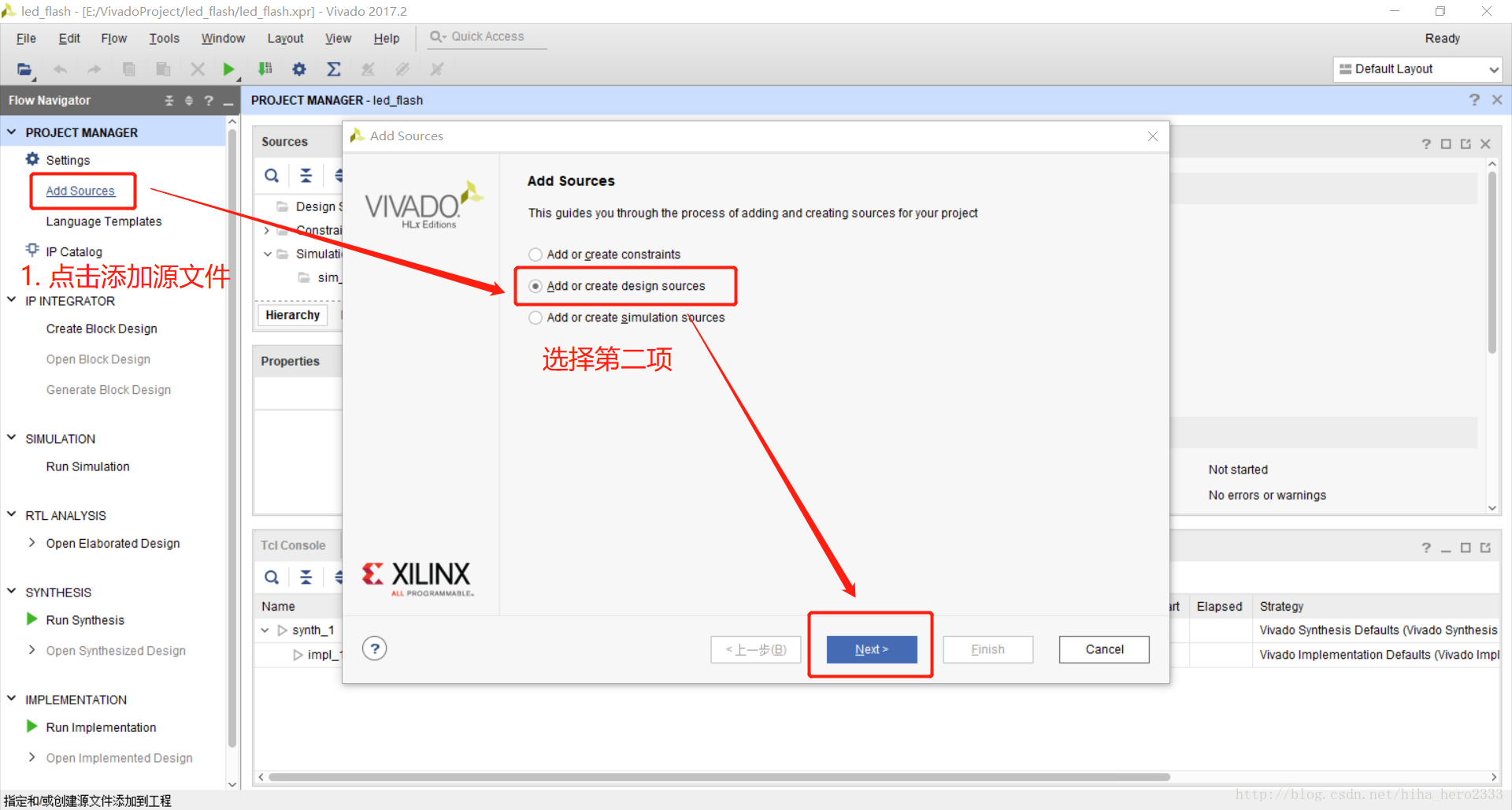

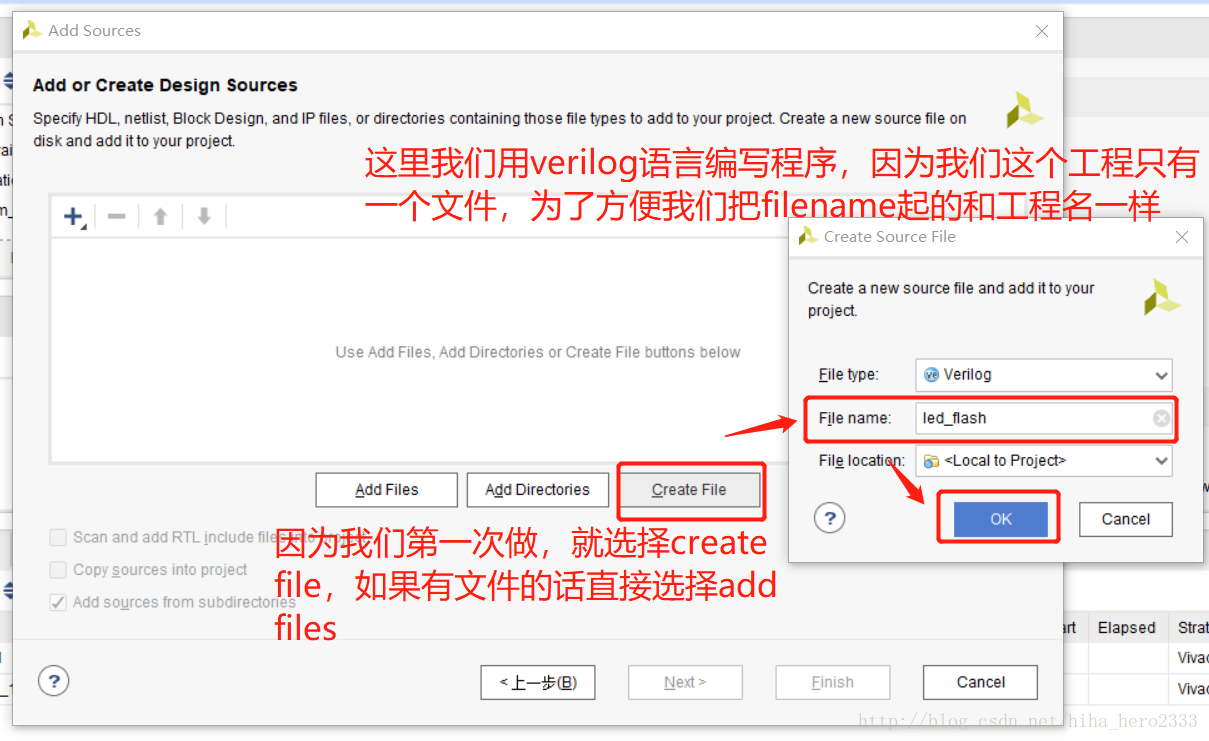

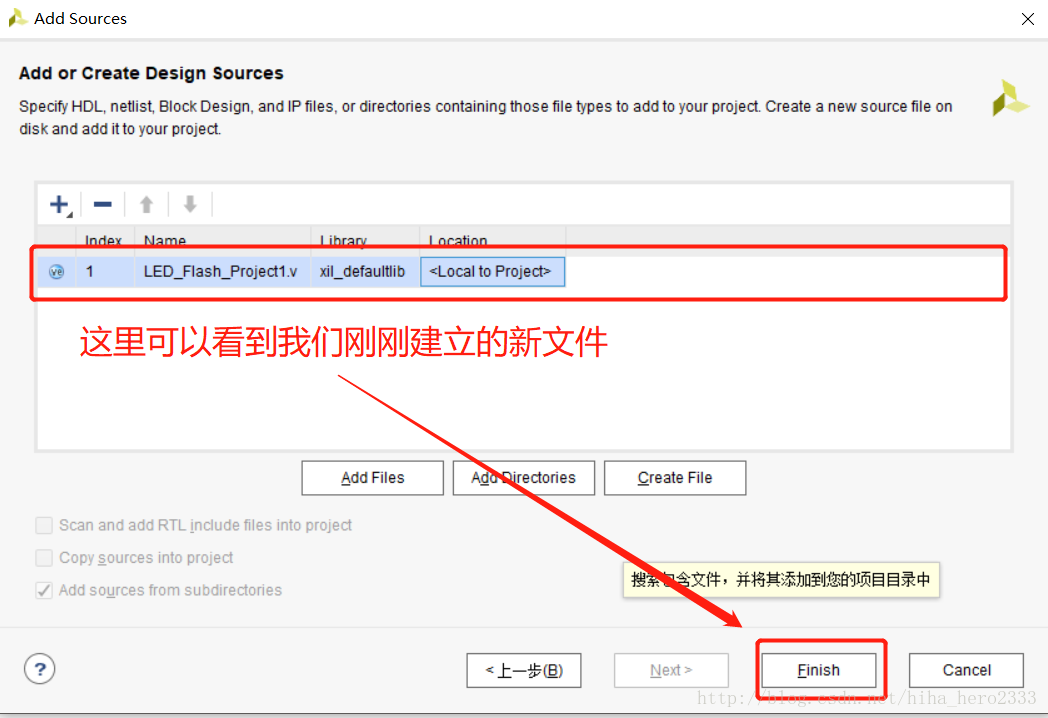

上图在给File name起名的时候,文件默认扩展名为.v文件,扩展名可以不用我们写。到了这一步,就可以在列表中看到我们刚刚创建的文件了,点击Finish。

(这里我操作快了,用的另一次创建时保留的图,可见文件名不样)

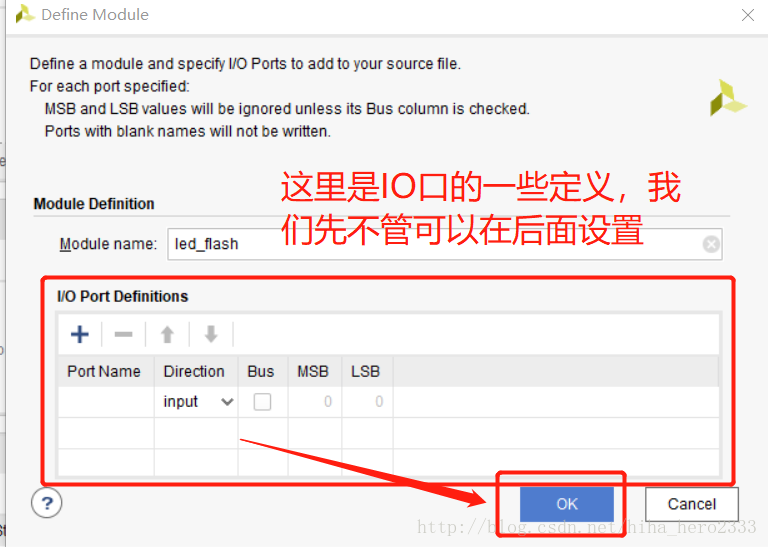

接下来会弹出一个窗口如下:

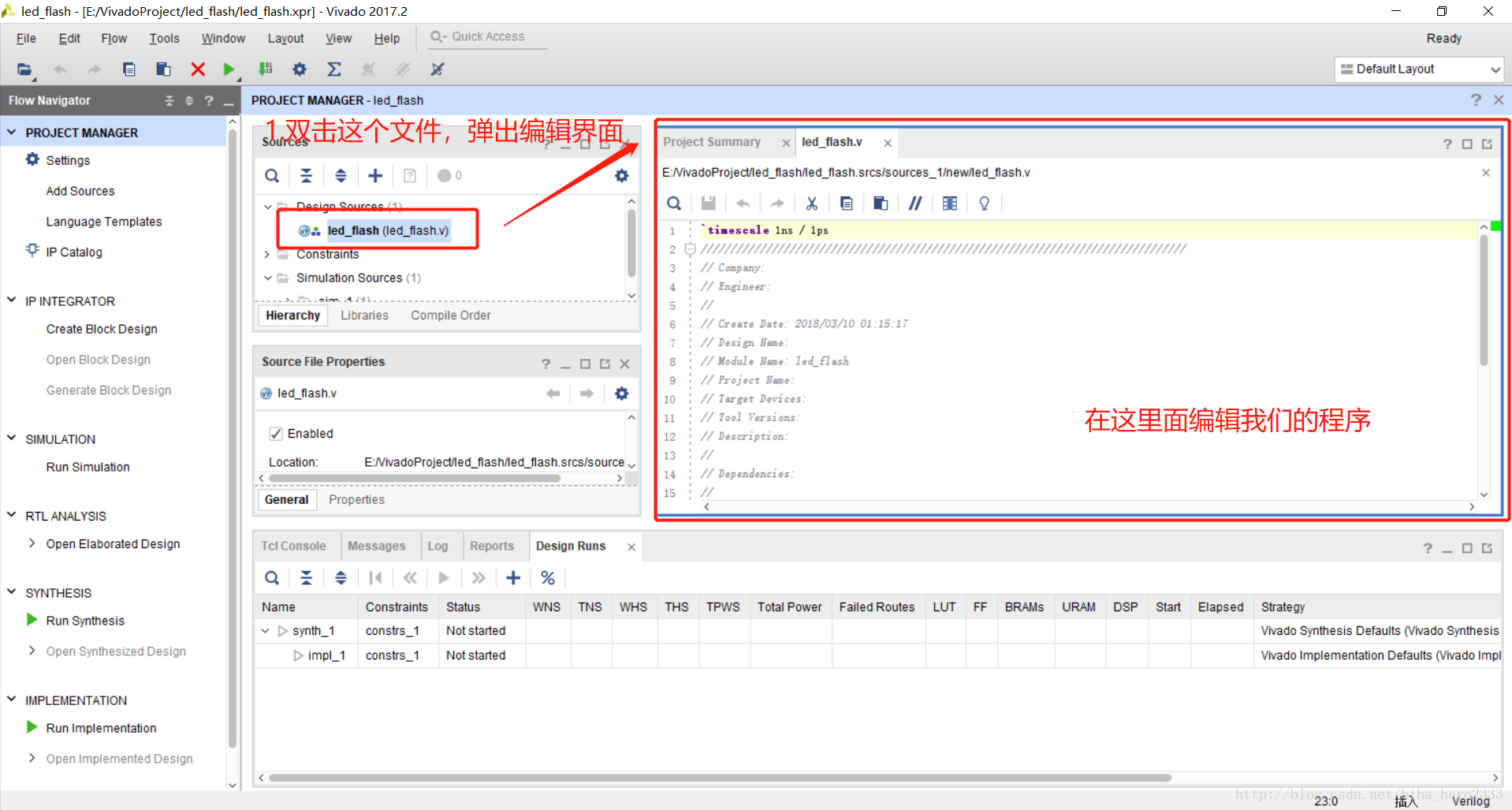

代码写好了,注意接下来的三步走:

综合(synthesis) > 运行应用(IMPLEMENTATION) > 生成bitstream文件

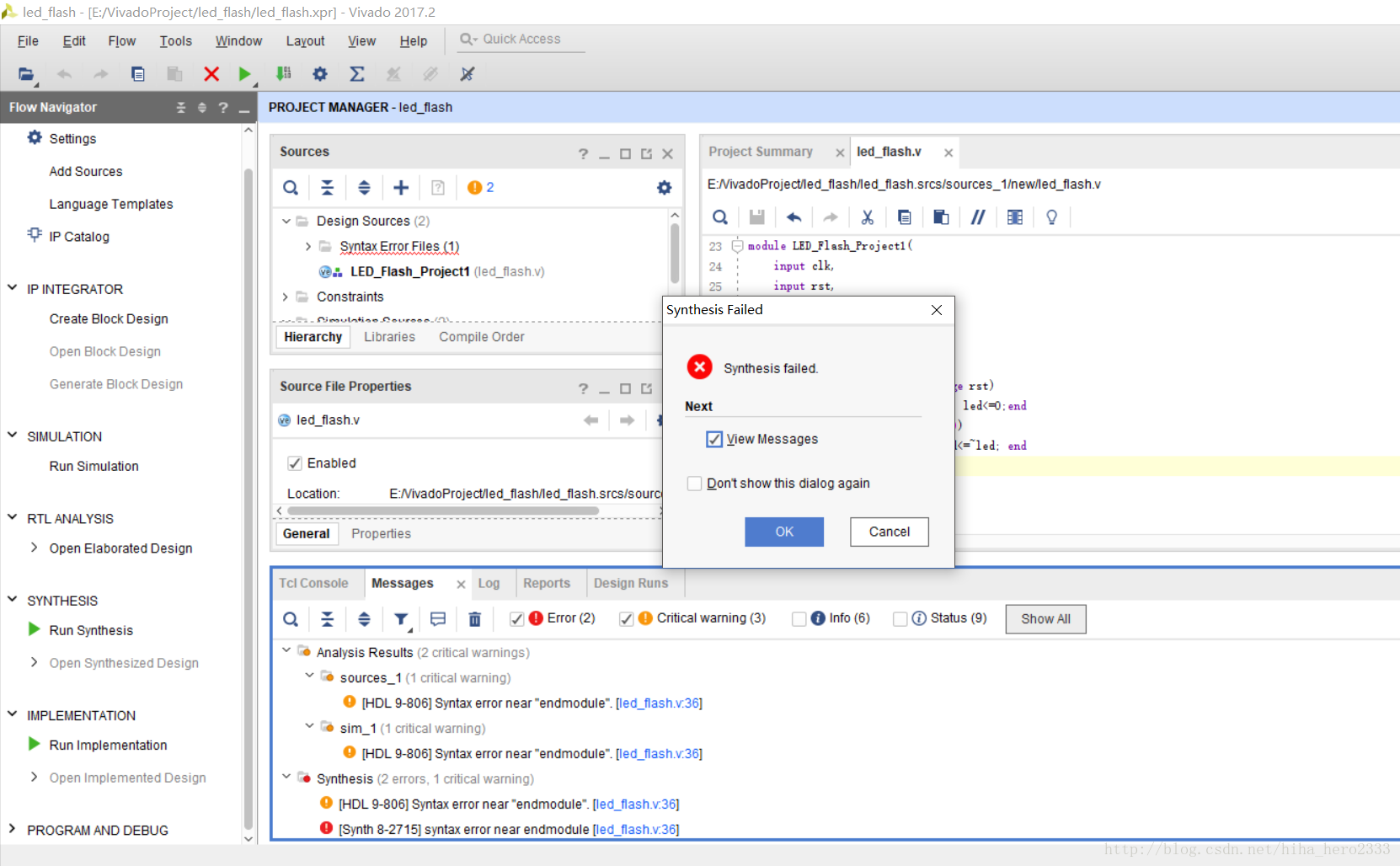

1.综合

当我们代码有错误的时候,“Run Synthesis”就会无法通过,并且下方会提示你的代码出错的报错信息,像这样:

改完错误继续Run SYNTHESIS

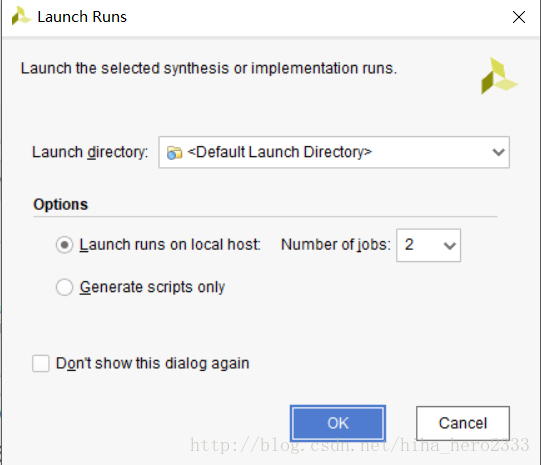

* 如果弹出这样的界面就直接点击OK

2. implementation + 设置我们的I/O管脚

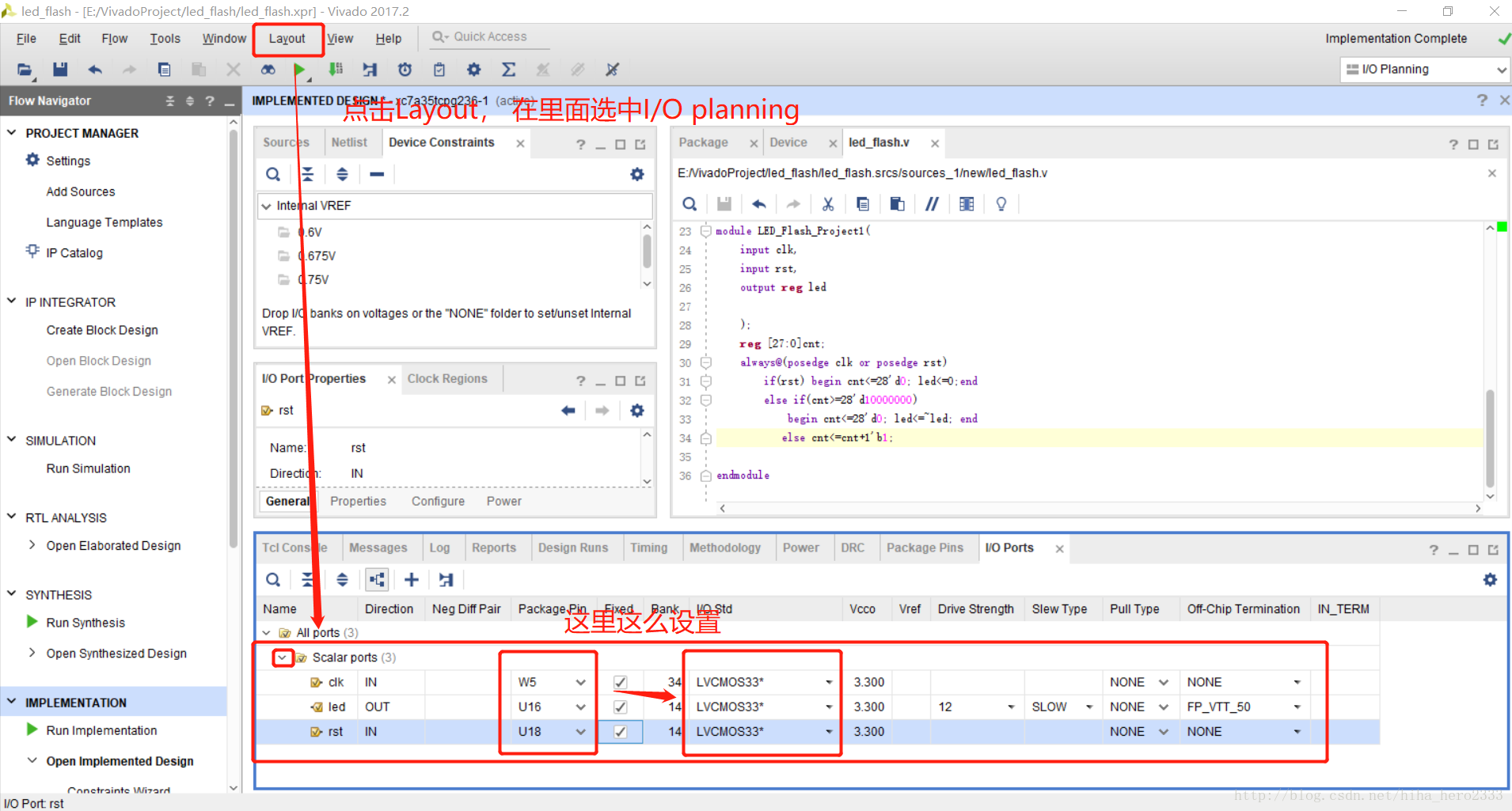

运行综合(run synthesis)之后,打开综合分配管脚:点击菜单栏的Layout >> I/O Planning, 进入下面的界面

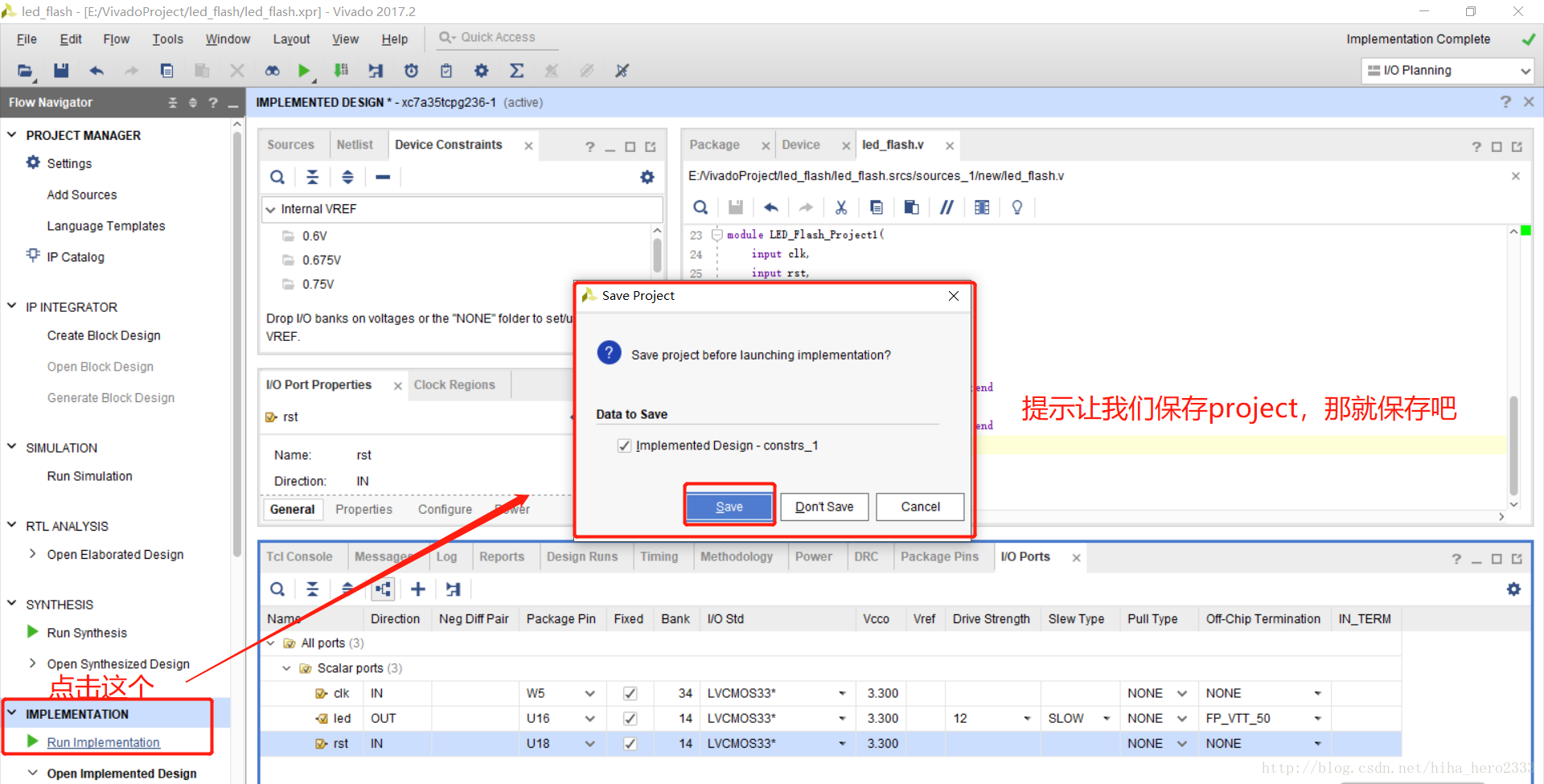

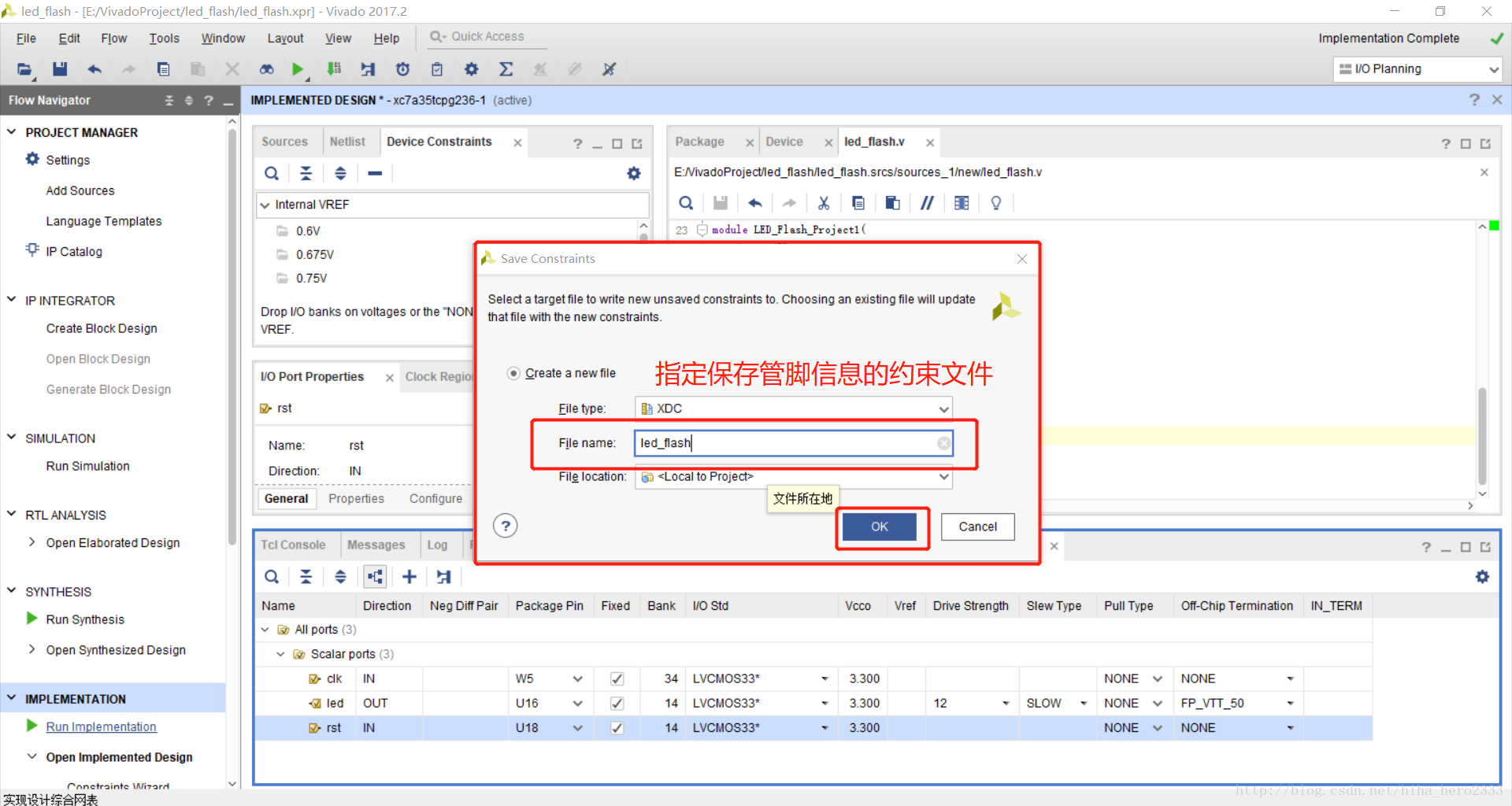

然后运行应用 (点击左边Run Implementation),之后提示你要保存,指定保存的文件名然后才执行“运行应用”,顺带着指定 “保存了管脚分配信息的约束文件”

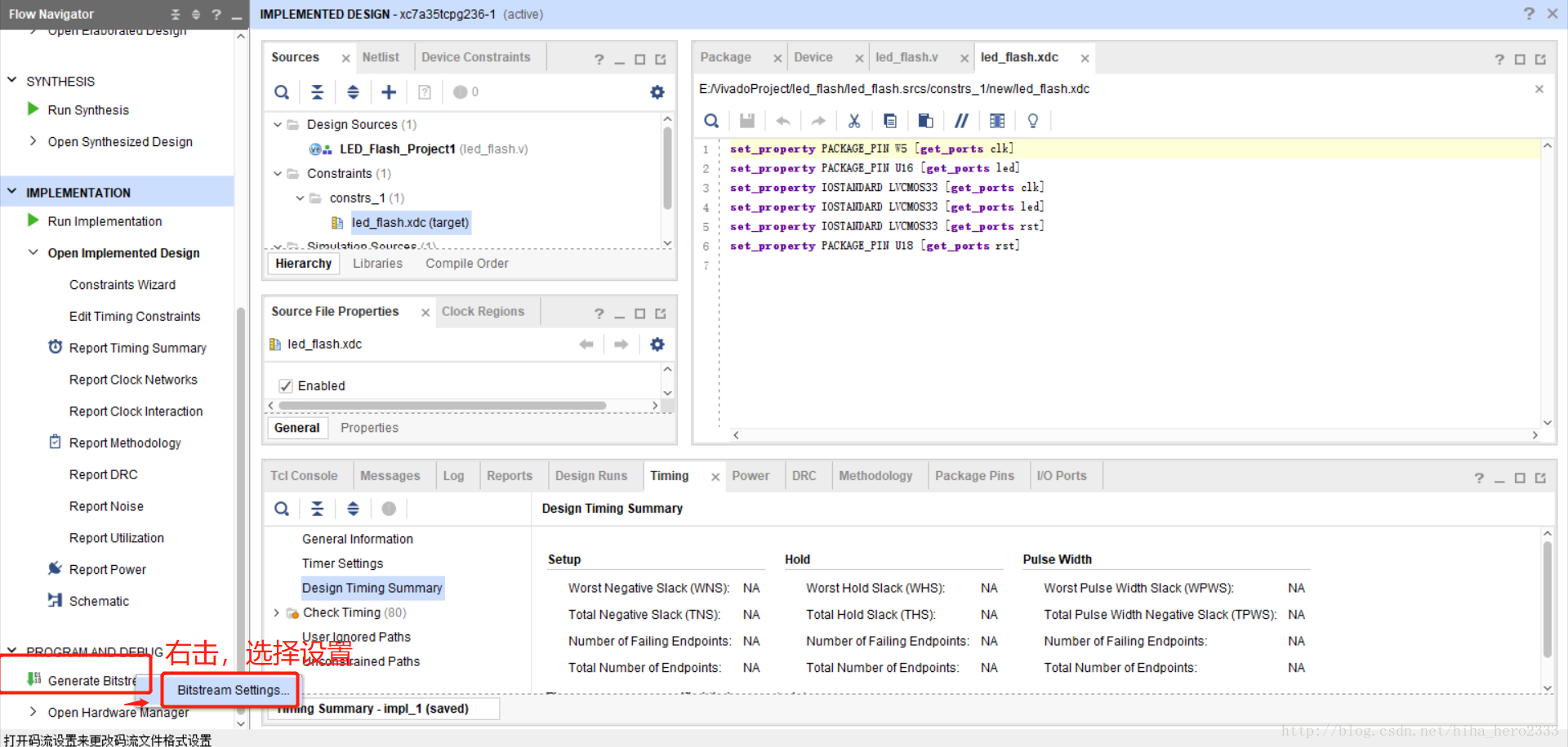

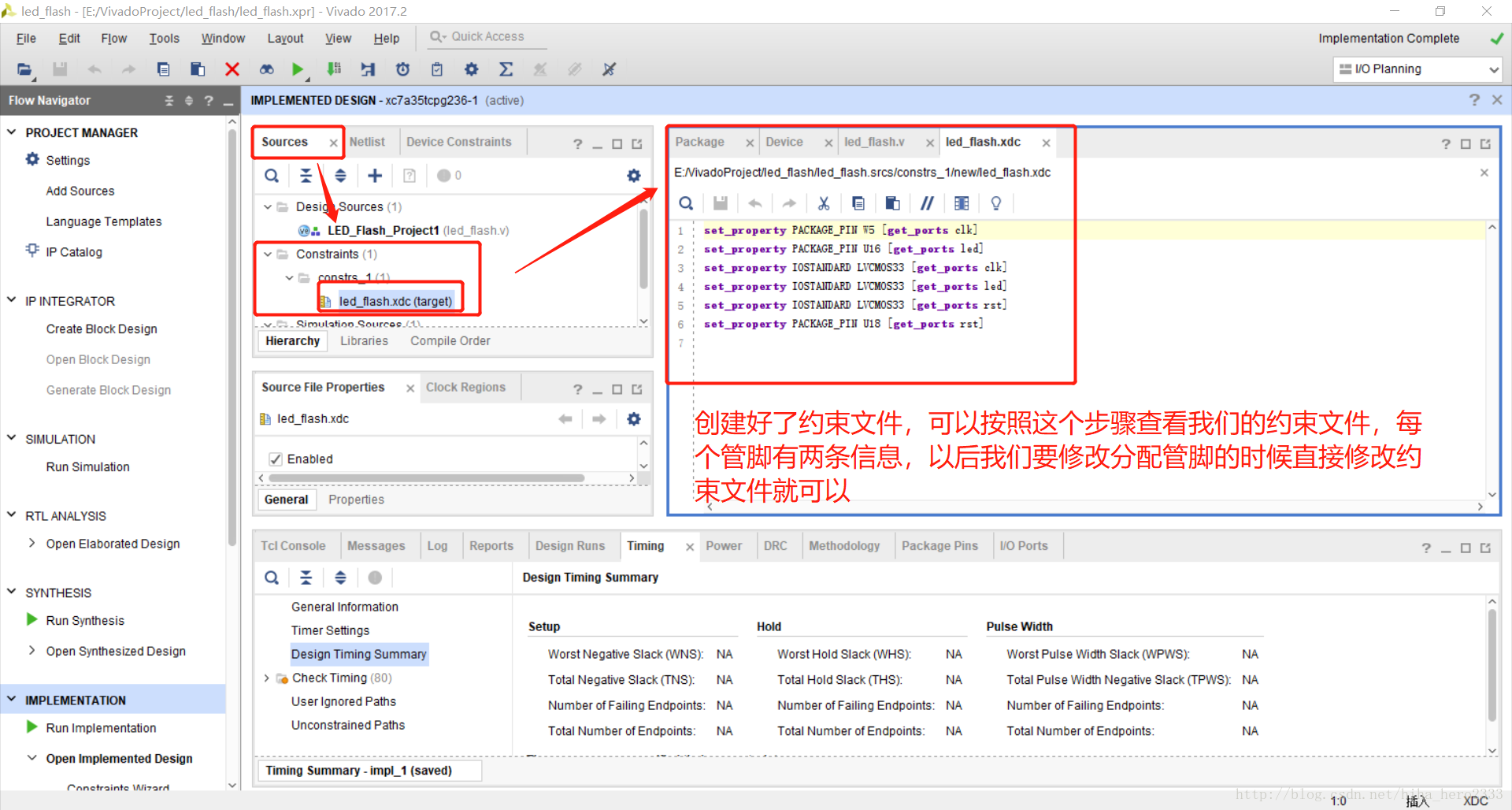

那么什么是约束文件呢?通俗的说,约束文件实际上就是将你的verilog中定义的端口号与FPGA板子上的IO口建立起联系,也同样是告诉软件该如何分配你所定义的端口号以生成对应的bit文件。

注意约束文件扩展名是 .XDC

我们备份约束文件,就可以在下一次新建工程的时候直接调用,不需要反复定义了,为了方便老师提供了我们使用的蓝色板子BASYS3和红色板子ego1的完整约束文件:

蓝色的BASYS3板子:链接:https://pan.baidu.com/s/1lMG3EDAo74PU8M6ep5L3AA 密码:fd5q

红色的ego1板子:链接:https://pan.baidu.com/s/1DijTWnjIYx4GVFdmj2ZEXQ 密码:8jjd

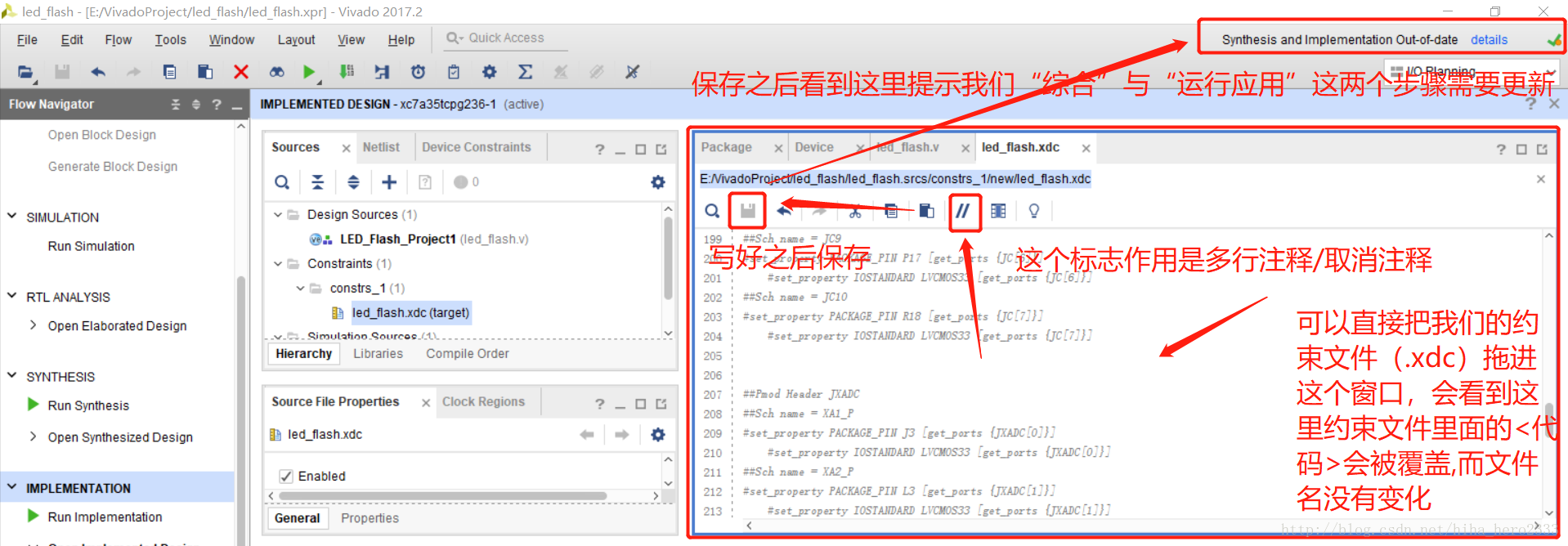

更新约束文件之后,我们重新 run synthesis >> run implementation 即可

注意,我们看到约束文件里面的代码,每个I/O port 对应的端口是两条代码语句(内容分别为 IOSTANDARD和 PACKAGE_PIN),如果我们要使用已有的约束文件,要注意我们源代码文件(.v文件)里面定义的端口名称和约束文件中的端口变量名称一致

这里是关于约束文件里面内容的介绍:

http://blog.csdn.net/feiliantong/article/details/78011665

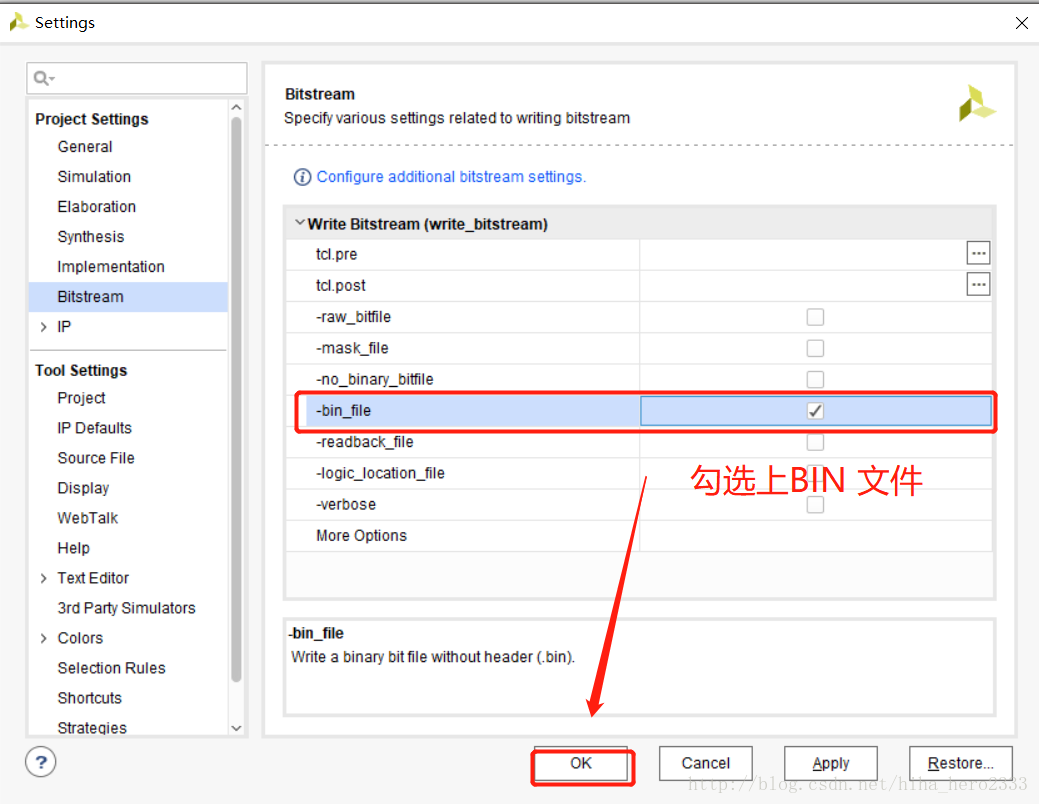

2.5 genearte bitstream之前设置一下文件生成属性

这一步的意思就是,每当我们 generate Bitstream 的时候,顺带着生成一个bin文件,bin文件是用来写给fpga的配置芯片的,而generate Bitstream会生成bit文件是用来写给fpga的。

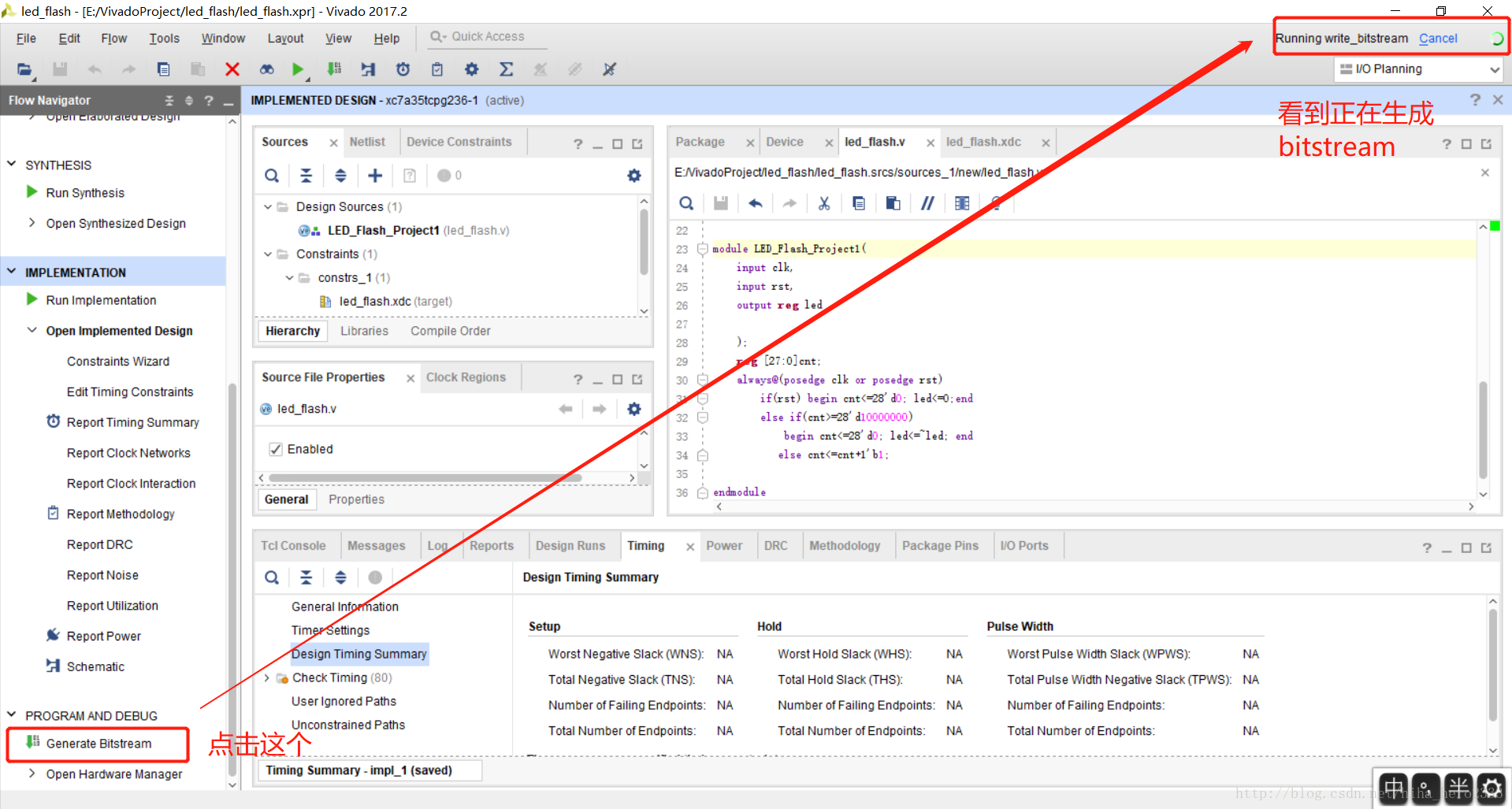

3.生成位码流文件(bitstream),按照如下操作:

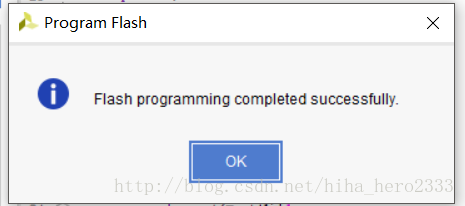

完成之后会有窗口提示complete。

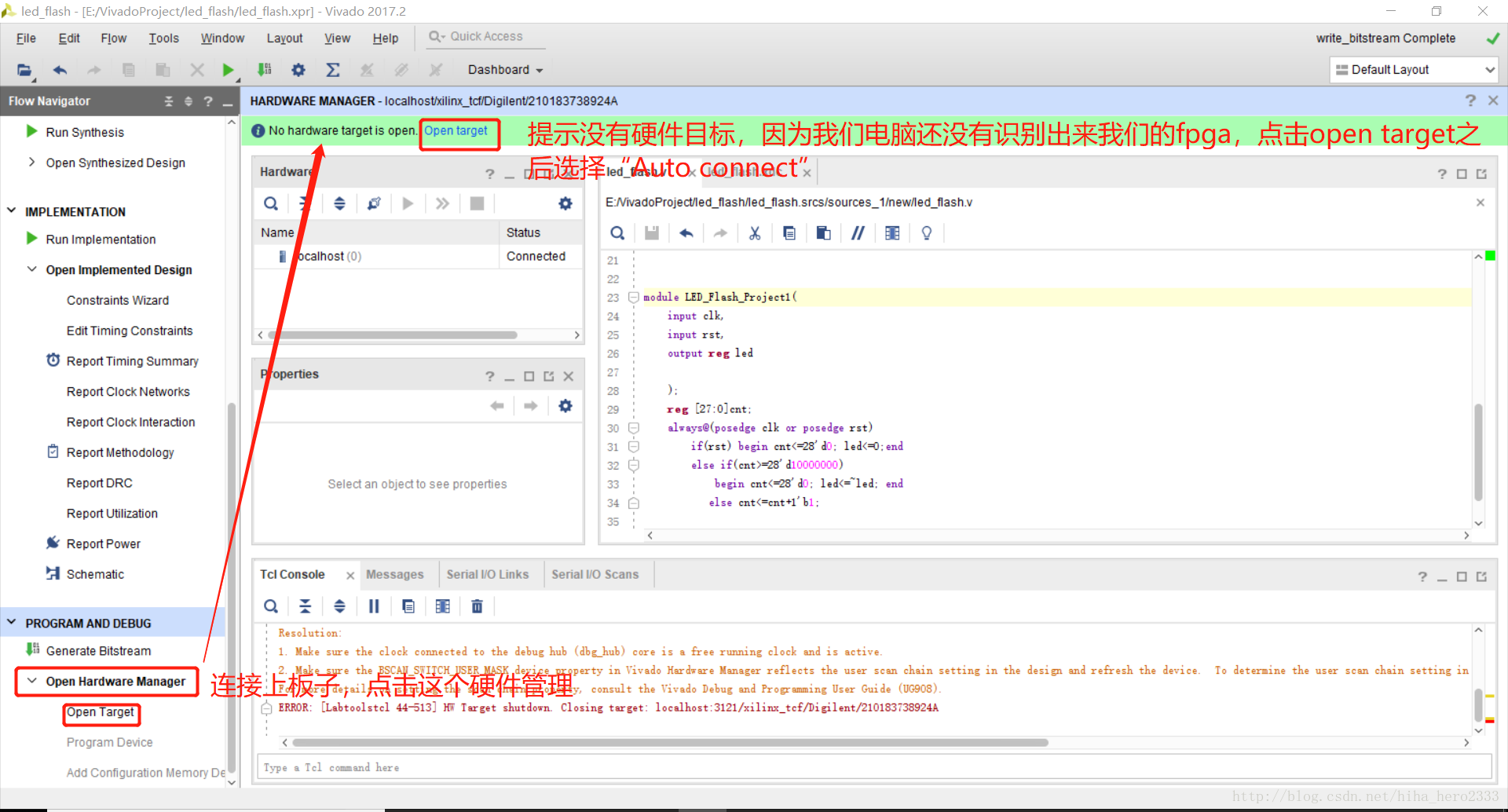

现在文件什么的都有了,我们可以把板子插上电脑进行实验了。

到现在为止,我们可以看到fpga上面小灯闪烁了

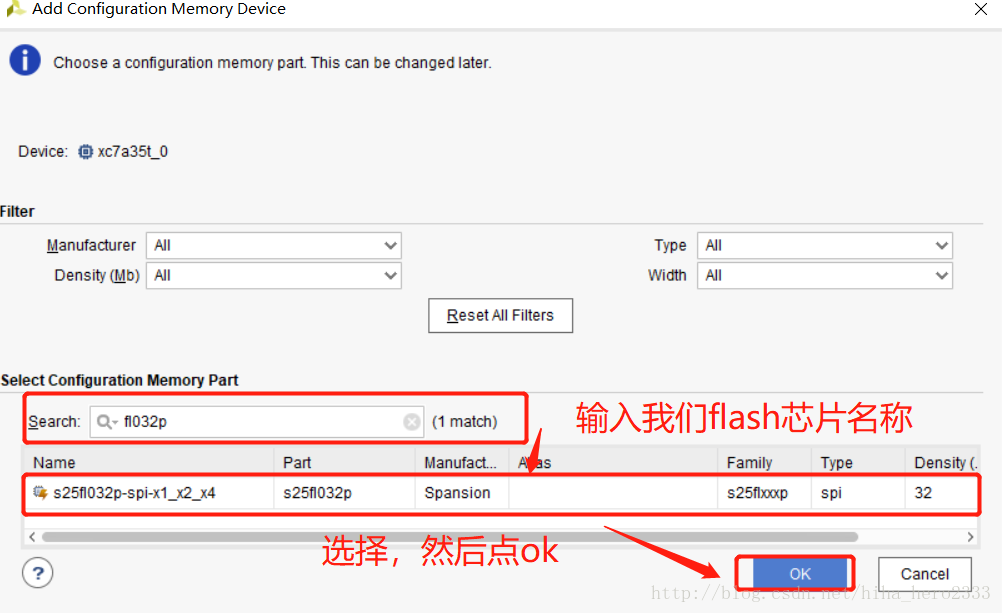

注意一下,fpga没有记忆功能,即下载到fpga里面的bit文件断电后丢失,如果我们想让程序在fpga里面一直保留,并且上电就能运行,那么我们就要将我们生成Bitstream文件时附带的bin文件下载到fpga上配置Flash的芯片才能记忆

如果我们想对程序代码修改,就直接对.v文件修改,然后再generate bitstream就可以了。

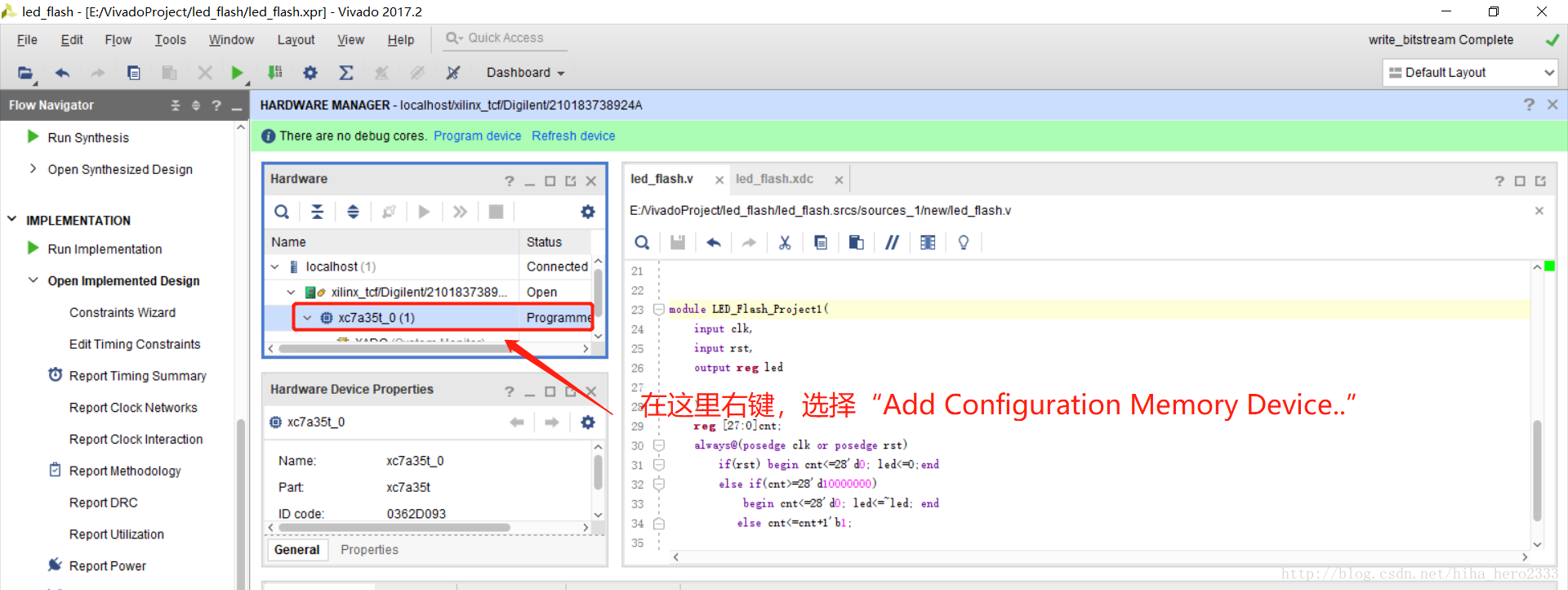

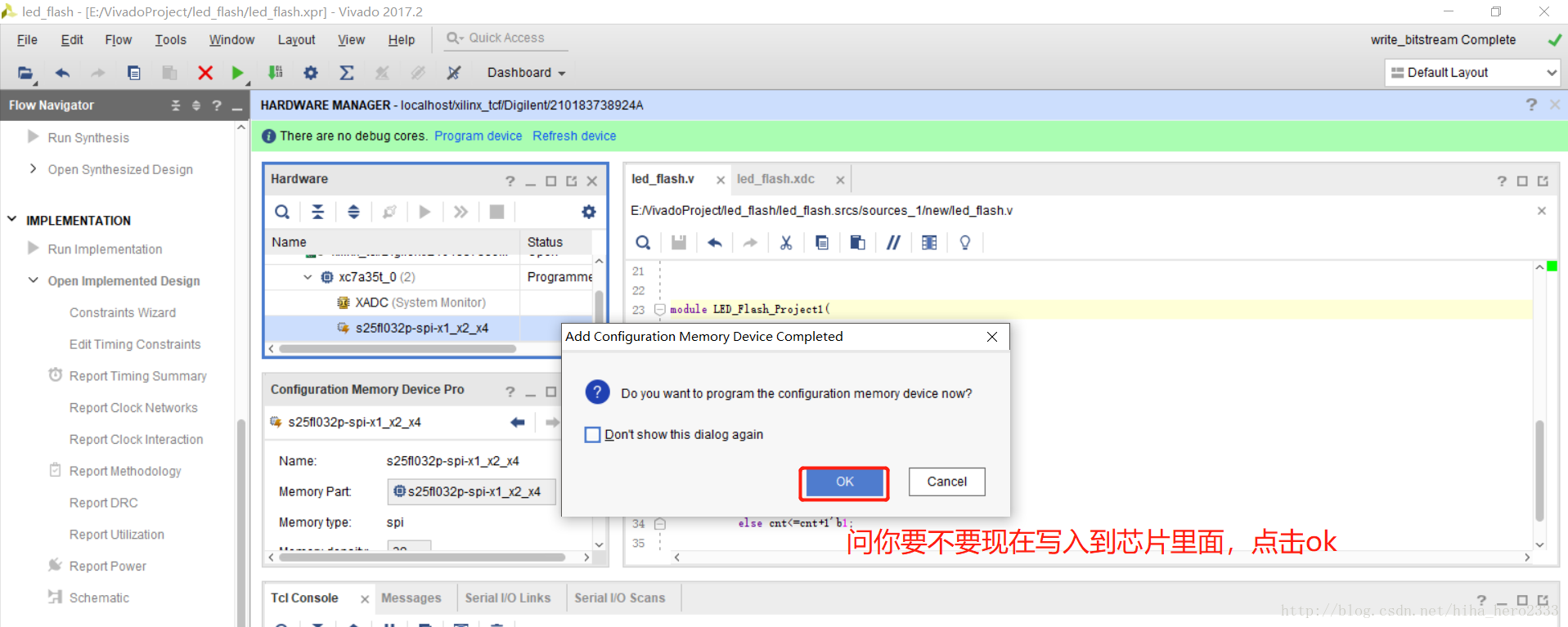

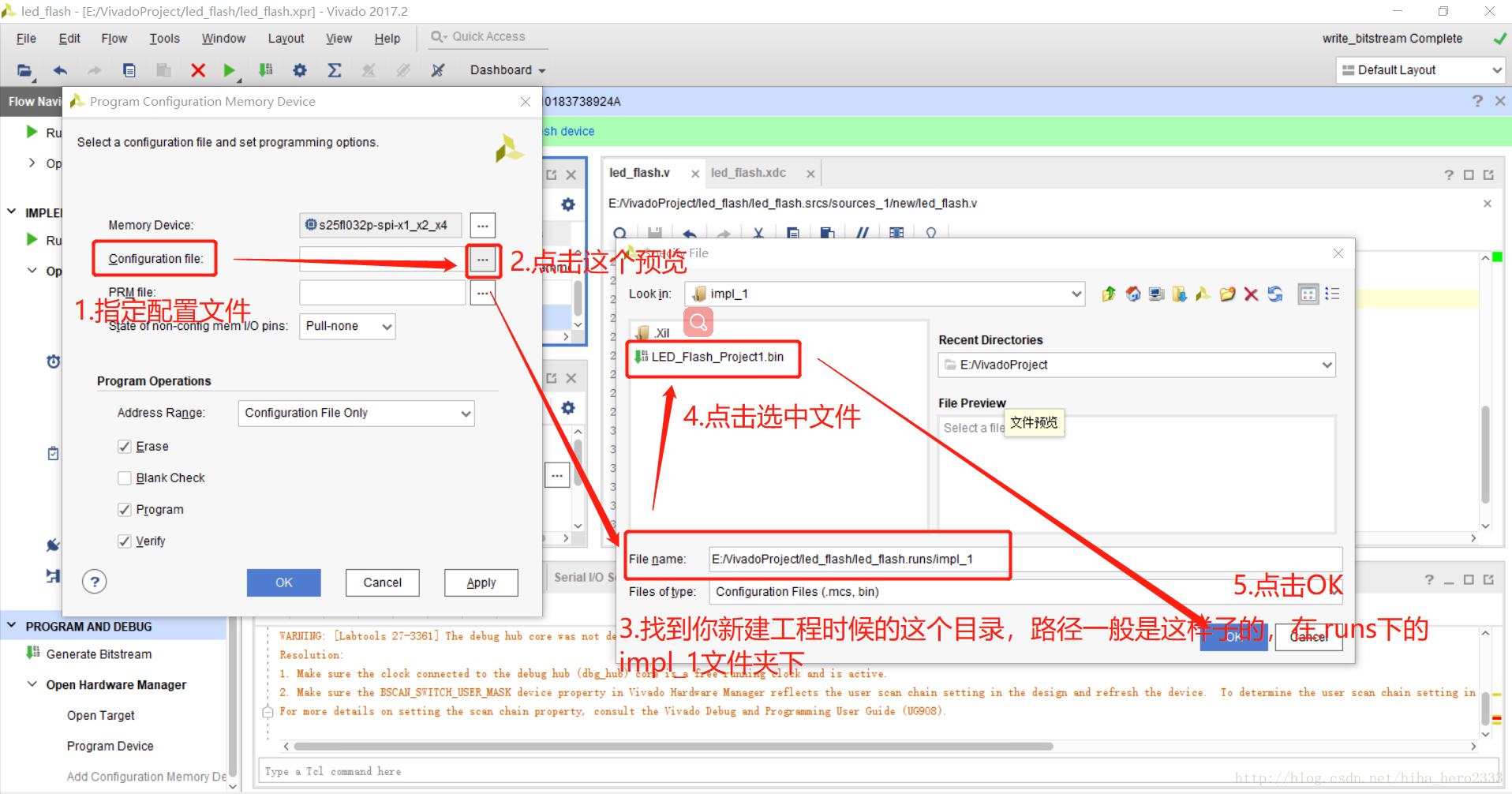

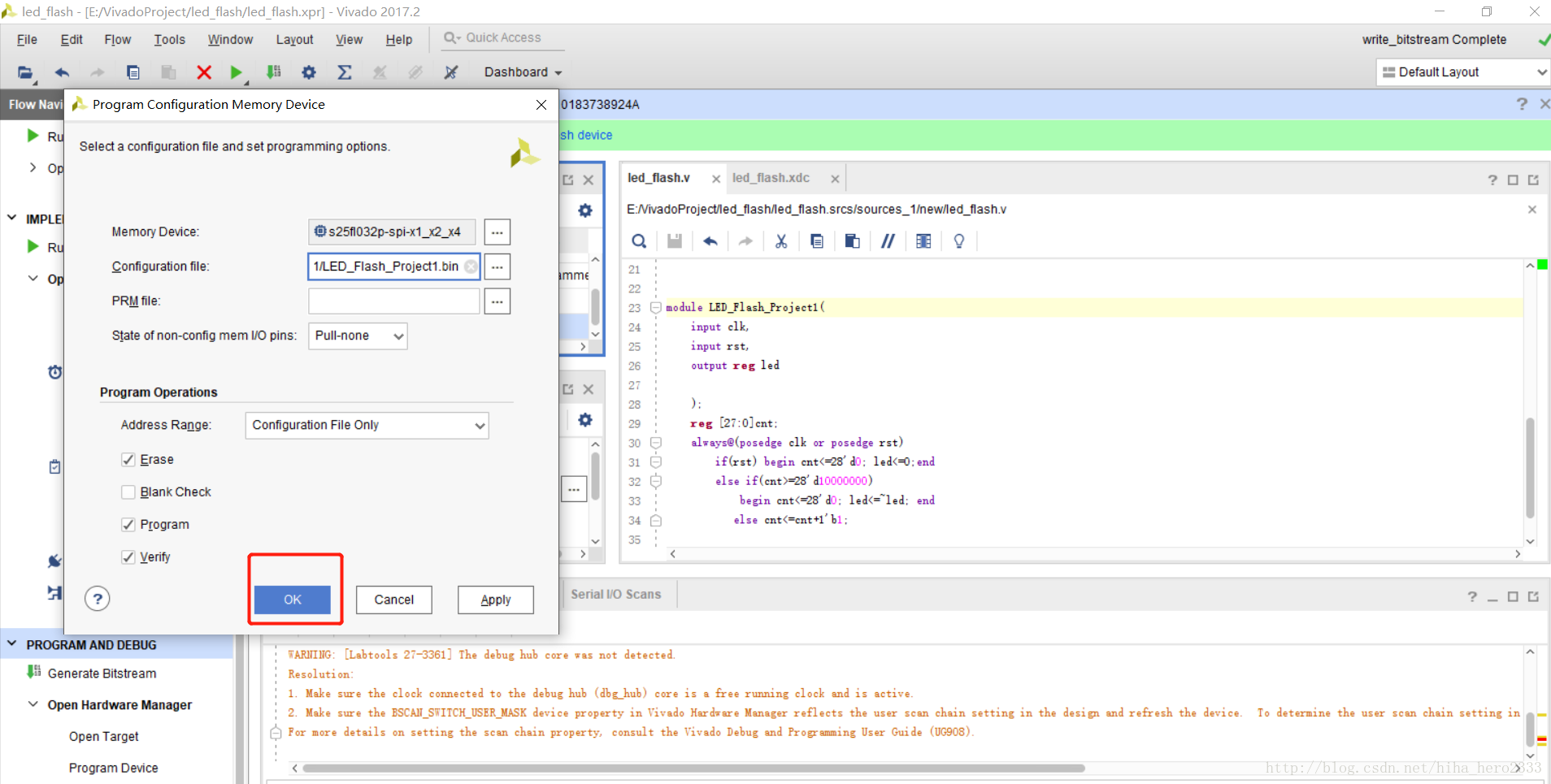

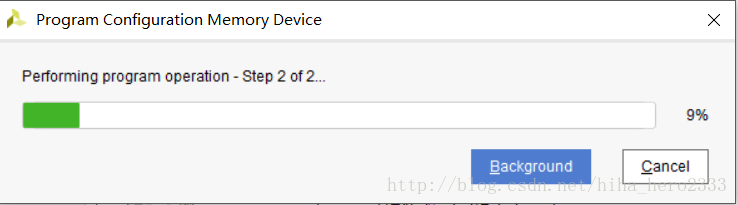

补充内容:把bin文件下载到配置Flash芯片,让fpga上电即工作!