例子:设计一个同步复位的3位计数器

分析:首先,我们可以看到有哪些信号。复位rst 、计数器3位的、时钟信号。(用到2路选择器。复位和不复位)

其次,怎样实现,一个时钟过来,记一次数就是加一次,保存(用到D触发器),满之后为0;

最后,按照以上分析,进行编写程序。

module cunt3(clk,rst,count);

input clk,rst;

output [2:0]count;

reg[2:0] count;

always @(clk)//同步复位

begin

if(rst==1)

count=0;

elseif(count==2'b111)//这就是个D触发器,q=count,d=count+1;

count=0;

else

conunt=count+1;

end

endmodule

module cunt3(clk,rst,count);

input clk,rst;

output [2:0]count;

reg[2:0] count;

always @(posedge clk)//同步复位

begin

if(rst==1)

count<=0;

elseif(count==2'b111)//这就是个D触发器,q=count,d=count+1;

count<=3'b0;

else

count<=count+3'b1;

end

endmodule上面是修改过的,由于时序逻辑电路,因此。用非阻塞赋值。q是3位,因此加上3'b1,

- 输入代码,选择Processing > start > Analysis & Elaboration

- Tools > Netlist viewer > RTL viewer

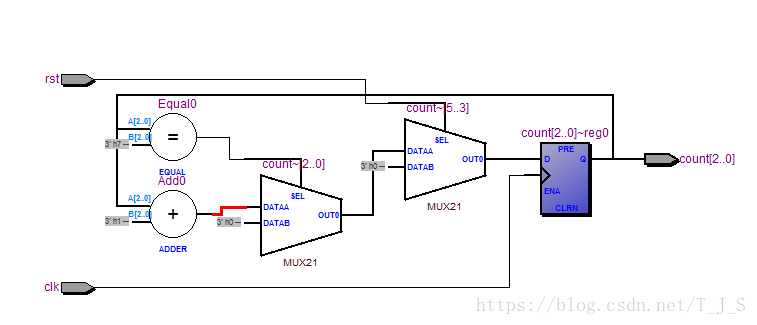

- 经过以上步骤,则得到以下电路。

因此,可以表明从程序里就可以看要用那些元件,从而能更好的理解程序的用途。