cmd文件:

一个cmd文件由三部分组成:

1)MEMORY命令:描述系统实际的硬件资源

2)SECTIONS命令:描述“段”如何定位

3)输入/输出定义:.obj文件:链接器要链接的目标文件;.lib文件:链接器要链接的库文件;.map文件:链接器生成的交叉索引文件;.out文件:链接器生成的可执行代码;链接器选项

一个简单的cmd文件如下:

PS: 在我们实际使用中可以直接把所需要的cmd文件添加的工程中

//MEMORY命令:描述系统实际的硬件资源

MEMORY

{

PAGE 0:

PROG0(RWX) : origin = 04000h length = 08000h

P_VECT(RIX) : origin = 0FF80h length = 00080h

PAGE 1:

DATA0(RW) : origin = 0C000h length = 04000h

}

//SECTIONS命令:描述“段”如何定位

SECTIONS

{

.vectors : { } > P_VECT PAGE 0

.text : { } > PROG0 PAGE 0

.cinit : { } > PROG0 PAGE 0

.csldata : { } > DATA0 PAGE 1

.stack : { } > DATA0 PAGE 1

.sysstack : { } > DATA0 PAGE 1

.bss : { } > DATA0 PAGE 1

.cio : { } > DATA0 PAGE 1

.const : { } > DATA0 PAGE 1

.sysmem : { } > DATA0 PAGE 1

}

.lib库文件:

我这里用使用到的是两个csl5509x.lib和rts55x.lib

其中rts55x.lib包含ISO运行支持库(for large model)

GEL语言:

不是必须的, 由TI提供或者自己编写, 方便程序调试

CSL (chip support library)片支持库 :

方便对DSP器件的片内外设的操作, 就不再需要对寄存器直接配置

GPIO (General purpose I/O) 通用输入输出:

可由软件配置为输入/输出状态

PLL 锁相环:

查了一下锁相环的定义, 理解的也不是太透彻, 目前简单理解为: 根据输入信号自振荡产生一个相同的信号(一般), 一般用于...用途很多.

输出频率计算公式:

将输入时钟频率乘以CLKMD中PLL_MULT的值,再除以PLL_DIV的值

PLL_MULT的取值范围是2-31

PLL_DIV是从0(除以1)到3(除以4)

输出频率= (PLL_MULT/(PLL_DIV+1)) * 输入时钟频率

eg: (24/(1+1))*12M=144M

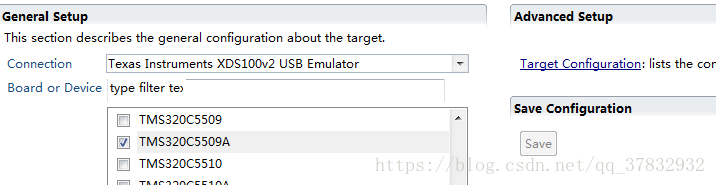

NewTargetConfiguration.ccxml 仿真器与目标板配置文件:

配置完成后点击save即可

关于硬件连接:

开发板接电源

开发板接仿真器接PC

新建一个工程:

学习补充中......