三星 Exynos 7420 何以成为 2015 年的独孤求败之作?by AnandTech

写在前面的话:

周三科技的 SLOGAN 是“只谈理论,不谈实操”,还有“优雅地纸上谈兵”。这就意味着,我期望聊更多理论层面的东西,多过实际应用——比如我对成像虽然感兴趣,但感兴趣的点仅在成像理论知识,包括光学和半导体——我对摄影根本就没兴趣,所以我不热衷于按快门,更不会在这里发布谈构图、光影这种具有实际价值的内容。

探究有趣的理论知识,不在意其时间、空间和实际价值,也就成为我撰稿,包括文章翻译的核心理念。下面这篇 Exynos 7420 剖析是国外媒体 AnandTech 发表于 2015 年 6 月 29 日的文章,这颗芯片现在看来早就过时——三星 Galaxy S6 时代的东西了。不过此文乃是 AnandTech 精心撰写的文章之一(准备周期至少也有月余),相对深入地探讨了 Exynos 7420 芯片的微架构、性能和功耗。将其剖开,对于移动芯片爱好者而言也算是增长见闻的机会。

这颗芯片对三星而言也算是意义非凡,其具体实施方案和能效表现在这个时代也算颇具代表性。更重要的是,“长在红旗下”、对半导体感兴趣的这一代应该不会忘记 Exynos 7420 的出生背景:一方面,高通仓促推出其史上效能表现最糟糕的骁龙 810,而 iPhone 6 同期采用的 A8 芯片也成为苹果有史以来性能跨步最小的一代 SoC;另一方面三星首次在工艺制程技术上领先台积电,率先大规模量产 14nm FinFET SoC。这个时间段应该算是半导体行业近些年好戏最足的一段时间了,ARM A57 架构甚至还因此背负了骂名。三星的 2015 年可说是春风得意的。

另外,这篇文章的程度要比我前几个月编译的海思 Kirin 960 芯片评测更为深入。文章从着手翻译到现在,前后写写停停,持续了半年时间,也算是心血了。期望与对半导体感兴趣的各位做分享,主要还是增长见闻、启发思路。

理论上,这样的文章应该不会被国内的科技媒体拿去编译和刊载,因为文章有一定门槛,且因为篇幅很长,没有耐心仔细钻研还真是看不下去。而真正会去看这些文章的人,其实对他们而言,语言从来不是个障碍——这也是这类文章不会被国内读者看到的一个原因。

我一向是以搬运为己任的上进型编辑,只可惜力有不逮,基础知识掌握并不扎实,也是一边学习一边翻。如果你在阅读过程中发现本文存在错误,请在评论中不吝指出——文章的许多问题我也是经过反复推敲和语言的重新安排才翻出来的,期望对各位有价值。这里概括一下本文的一些有趣观点:

- 在 Exynos 7420 身上,14nm 工艺的确为其获利良多;光就芯片尺寸来看,GPU 部分即便增加两个 shader core 核心(8 核心),面积仍比 Exynos 5433 的 Mali T760MP6(6 核心) 更小;

- Mali T760MP8 GPU 部分占到 Exynos 7420 整体面积的近 1/4;

- Galaxy S6 是当时第一批采用 2K 分辨率屏幕的设备,但你可能不知道的是,要驱动比 1080p 分辨率更高的显示内容输出,SoC 的显示流水线原本要求采用双 DSI,这会造成双倍功耗;为解决这个问题,三星没有采用双 DSI,而是采用 MIC 压缩机制,对显示内容进行压缩传输;且采用了屏幕局部刷新技术,进一步减少传输开销;

- 三星为 Galaxy S6 配备的 modem 是三星自家的 Shannon 333。这颗 modem 与 Exynos 7420 之间采用 LLI 连接;其价值就在于以前的外置 modem 是需要配备额外的内存的,而采用 LLI 连接就可以让 modem 直接访问 SoC 的主内存了;

- Exynos 的 MFC 硬件媒体加速器支持 MPEG4、H263、H264、VP8、HEVC 等格式的编解码,这次的 MFC v9 性能与功耗表现都不错,4Kp30 Main HEVC 视频播放整机功耗也仅为 950mW;

- 三星在 Exynos 芯片中用上了闭环电压调节机制,这种技术早见于德州仪器,但三星还将其与芯片 binning process 分级流程进行了结合——这在其它芯片中是看不到的;

- 虽然也算是“公版设计”,但 Exynos 7420 很多设计都并未采用 ARM 的方案。比如说 CCI-400 互联部分的设计,ARM 官方的 CCI-400 给 GPU 准备了两个端口,但在 Exynos 7420 中,GPU 和 G2D 模块(2D 图形加速器)共享一个 CCI 端口;GPU 也并没有通过 CCI 连接内存控制器;此外三星将 CCI 频率定在最高 532MHz,没有达到 ARM 推荐的 DRAM 的一半频率。

- Exynos 7420 CPU 部分的能效提升亮眼,在 1.9GHz 频率下(大核心),Exynos 7420 的核心平均最大功耗仅有同架构 5433 的一半;Galaxy S6 是 AnandTech 以往测试中功耗表现最出色的设备;#附送 undervolting 尝试大礼包...#

- AnandTech 认为,Exynos 7420 如果将 CPU 最高频率设定在 1.9GHz,其收益会更高:10% 的性能损失可以换来 26% 的功耗降低;

- 三星针对 Exynos 7420 进行了较多配置上的调整,例如电源管理优化,大小核心的线程迁移更合理(比如将线程从小核心迁移到大核心的阈值定在 46.7%,即小核心资源占比超过该值,则线程迁移至大和心)、没有一味追求高频率、优化 Android 默认的交互式 CPU governor;这些都让 Exynos 7420 的 CPU 电源管理做得很出色;

- Exynos 7420 的 GPU(Mali T760MP8)是 AnandTech 以往测试过性能最强的 GPU,而且能效最高,超过以往高通的任何一款 Adreno GPU;

- 你可能知道高通骁龙 810 的 CPU 效能表现一团糟,但你可能不知道其 Adreno GPU 部分的性能也不如 Exynos 7420,且效率低下;另外骁龙 810 GPU 部分表现甚至还不如前代骁龙 805——包括性能和效率;

- 但是!!!AnandTech 特别指责 Exynos 7420 过度推高 GPU 频率,发热令其最高频率下运行仅能维持不到 2 分钟;而且温度管理存在问题,导致其性能曲线飘忽不定;

- AnandTech 认为,过度推高 GPU 频率已经成为整个行业的恶习,这种行为有百害而无一利,除了让跑分成绩更好看,对用户的游戏体验稳定性和设备续航表现都存在消极影响;

- 2015 年,Exynos 7420 几乎处在独孤求败的地位。

由于文章真的非常长(字数约 25000 字),可能是我目前编译过单篇长度最长的文章(也可能会是唯一一篇没人愿意花时间从头到尾看完的文章)。所以这里列举这篇文章的提纲,可选择性阅读;如果你没有耐心看完,其实看上面的要点概括也差不多了,不过文中有更多细节探讨:

1. 探寻三星 14nm 制程

2. 进入 Exynos 7420 内部

3. CPU、存储性能与设备拆解

(1)CPU 性能:64 位处理

(2)存储延迟和性能

(3)离个题:Galaxy S6 拆解

4. CPU 功耗

5. CPU 电源管理

6. GPU 性能与功耗

- LPDDR4 性能与功耗

7. 总结

正文开始

过去几年,三星电子为同款移动设备采用不同的 SoC 已经成为传统。尤其主要是在北美和 CDMA 市场上,高通 SoC 的采用率还是相当广泛。这种策略早在 Galaxy S2 时代就开始了,当时的三星手机既有采用 Samsung System LSI 的 Exynos 芯片版本,也有高通骁龙芯片版。先前几代 Galaxy 设备,我们也逐渐看到 Exynos 芯片的平均份额在减少,因为先前 SoC 架构转向 ARM Cortex A15 的时候,其功耗和表现都不如平衡性更好的高通 Krait 架构 SoC。实际上,我们上次看到三星在 Galaxy 全球通用版设备上采用 Exynos 已经是 2012 年的 Galaxy Note 2 了。

而 Galaxy S6 在全球范围内都采用三星自家设计的 SoC,这和一年多以前的情况形成了比较鲜明的对比。Exynos 7420 真正标志着三星的新一代 SoC。这颗芯片被三星说成是“迄今为止最先进的应用处理器”,所以我们打算对这颗 SoC 进行深入挖掘,尝试了解其功耗、性能等方面的表现。

年初我们在 Galaxy Note 4 采用的 Exynos 5433 身上,实际已经对三星 Exynos 7420 有了初步的窥探。有心的读者应该还记得,去年 9 月(译者注:实际是 2014 年 9 月),在 SoC 设计方面,我说 Exynos 5433 是超越“大脑移植”(brain-transplant)般的存在。这话的意思是说,这颗芯片采用最新 ARM A5X 系列 CPU 设计和 Mali T760 GPU。相较去年的其他 SoC,诸如 Exynos 5430(A15/A7 + T628)及更早的产品,Exynos 5433 都是重要的进步。

初看 Exynos 7420,可能会感觉这颗芯片也就是工艺进化、GPU 配置小升级,外加支持 LPDDR4 内存,但实际上我们会看到其下还有更多的细节改进。

探寻三星的 14nm 工艺

大约在 18 个月前,我们就听到了有关三星要采用 14nm SoC 的传言。三星半导体在前沿的晶圆代工生产业务方面,一直是落后于台积电(TSMC)的,所以分析师和大部分媒体都认为,这个传言只是个不大现实的预期而已,毕竟去年下半年的苹果 A8 以及最近的高通骁龙 810 和 808 都才刚开始采用台积电的 20nm 工艺。即便三星早在 10 月(译者注:2014 年 10 月)就说在搞 14nm 芯片,而且还多次在财务电话中确认去年晚些时间就能实现大规模量产,但今年真正看到 14nm SoC 应用到 Galaxy S6 之上,还是让不少人感觉到了震惊。

14nm 制程标志着三星从平面晶体管转向 FinFET 晶体管。Intel 早在 2012 年出货的 22nm 制程的产品中就先于其他竞争对手采用这种技术了,所以我们对于这种技术应该也不会陌生。

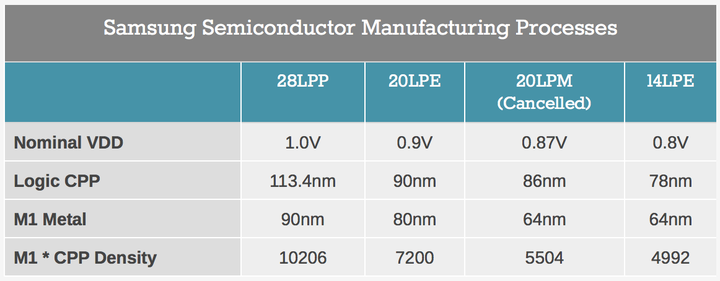

针对三星 14nm 制程的另一个议论焦点在于,相比其前代 20nm 制程,die size(译者注:die size 可以简单理解为芯片尺寸,但实际上 die size 并不等同于芯片尺寸)是否“真的”缩减了。我们自己也很惊讶地看到 Chipworks 说这次的 die size 仅 78mm²,早前的 Exynos 5433 则为 113mm²。尺寸缩减多达 31% 还是出乎我们意料的,先前我们曾报道说三星的 14nm 制程持续采用其 20nm 的 BEOL(芯片最大的金属层,Back-End-Of-Line),所以预计尺寸变化不会很大。BEOL 的 M1 金属间距与晶体管栅极(门电路)间距决定了晶体管密度,以及在相应制程下芯片设计如何对尺寸进行控制。三星 2015 年 2 月的 ISSCC 大会呈现 Exynos 5433 之后,一切就已经变得明朗了:

虽然三星先前将 20nm 结点作为单独的一代工艺,实际情况却是其 20nm 节点有两种不同的版本。Exynos 5430 和 5433 之上所用的 20nm 制程实则名为 20LPE。而实际上还有个名为 20LPM 的节点版本,在 M1 金属间距方面是不一样的。20LPM 似乎是个被三星取消的节点,随后部分工艺应用到 14nm 制程之上。下面这张表格总结了三星这几个生产工艺之间的差别。

M1 间距乘以 CPP(译者注:CPP 是指栅极间距,说得具体些,CPP 应该是指源极触点和漏极触点之间的距离),基本就完整呈现了制程密度。在此我们也意外发现,这个数据正好符合 Exynos 5433 和 Exynos 7420 之间尺寸 31% 的缩减。

然后我们再来看看 5433 和 7420 之间不同模块的尺寸差异,我们发现上面提到的尺寸缩减其实只出现在了 A53 核心之上。A57 核心及其整个簇尺寸缩减多达 59%,而 GPU 部分的尺寸则缩减了 30% ——请注意!相比 5433 的六核 GPU, 7420 还增加了两个 shader core 核心(译者注:Exynos 7420 的 GPU 为 Mali-T760MP8,而 5433 的 GPU 为 Mali-T760MP6)。7420 之上单个 T760 核心尺寸为 1.75mm²,从 GPU 总的 17.70mm² 面积中减去 3.5mm²(译者注:也就是两个增加的 shader core 核心),那么得到 14.2mm² 也就是其 6 个核心的理论面积。这个面积相比 5433 的 GPU 缩减 56%(译者注:这么比的价值在于,假定两颗芯片的 GPU 同样是 6 核的情况下,7420 的 GPU 部分的 block size 比 5433 减少了 56%)。

像这样,主 IP 部分多达 56% 的尺寸缩减表明,三星不仅借助了制程的进步,还进一步调整了具体的实施方案(implementation),可能是采用更高效的 cell libraries,也可能在密度层面进行了优化。基于上面这些数据,包括在多增加两颗 GPU 核心、采用 LPDDR4 内存控制器的情况下,仍然相较上一代芯片缩减了 die size,我们也能够从中看到三星的确期望打造一款轻量级的 SoC。

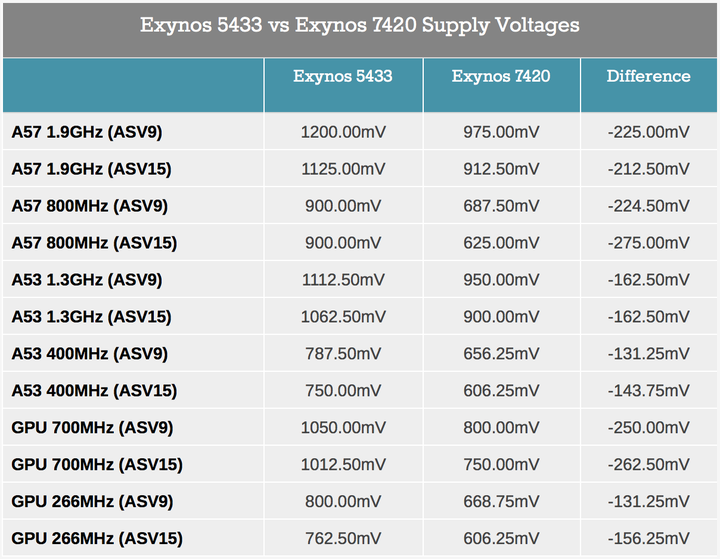

工艺迭代能够带来的外在特征诸如功耗、电压方面的变化。某些芯片供应商的产品,其实很难获取其中的 SoC 电压,比如海思 SoC 顶多能读到 PMIC(电源管理集成电路) 的登记值(register values),但无从了解降压变换器与实际电压的间接映射关系,也就不知道 SoC 究竟跑在怎样的电压水平。好在三星的 SoC 不存在这种困扰,针对 Galaxy S6 的评测中,我们就已经能够呈现对比 Exynos 5433 20nm 制程,电压的总体差异。这里再度呈现 CPU 核心在某些频率下,7420 相较 5433 电压变小的一些例子。

在针对 Galaxy S6 的评测中,我们简要谈到了三星是如何针对 ASV(Adaptive Scaling Voltage)进行芯片分级的(silicon binning process)。生产过程中的工艺偏差会导致芯片形成不同的电特性,某些芯片无法按照目标规格正常运转。在桌面领域,应对这种问题的方案就是禁用芯片中某些部分,把这样的产品(所谓的“bad piece”)做成更低价的 SKU。目前我还没有发现,移动领域有哪家半导体制造商会采用这种方法,因为在移动领域将芯片做成性能更低的 SKU 其实不怎么现实。移动半导体制造商的一般做法是,针对这样的工艺偏差,尝试增加电压,以这样的方式来克服生产问题。针对芯片的电特性,工厂就会对其进行测试,每片芯片都会标记上这些信息(永久烧制上去的)。

Exynos 芯片的这一过程被称为 ASV 分组。更高电压的分组,包含“slow-”(慢)或“cold”(冷)的芯片,这个分组的意思是指,工艺偏差导致晶体管不能达到设计频率,不必增加 VDD(工作电压)。”cold” 芯片的好处在于其静态漏电(static leakage)相对控制得更好。还有个分组就是“fast”或者“hot”芯片了,有着更低的阈值电压,能够以更低的 VDD 达到目标时钟频率。和 cold 芯片相比,hot 芯片由于更低的 Vt(译者注:呃...Vt 是指开启电压?),所以静态漏电多得多。现如今的大规模 SoC 功耗主要是由动态漏电(dynamic leakage,栅极到漏极,DIBL 漏极引入的势垒降低,等等)(译者注:DIBL 全称叫 Drain Induced Barrier Lowering,这是场效应晶体管中出现的一种不良现象)决定的,它相比静态漏电要显著多了。而且 FinFET 相较平面工艺,能够极大减少静态漏电。所以很显然,上面提到的“hot / fast”分组芯片更好,因为这些芯片有着更低的工作电压。

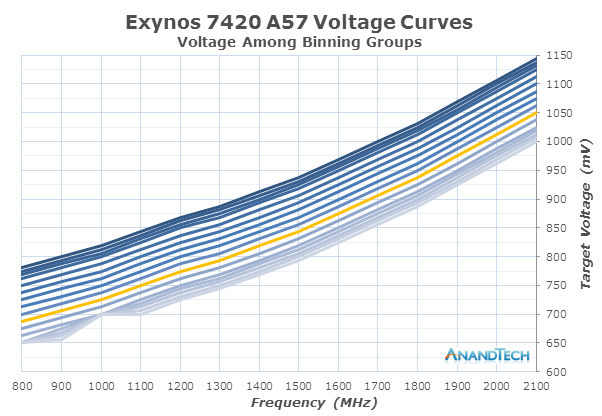

如上图所示,Exynos 7420 最佳和最糟的芯片有着高达 150mV 的差距,也就是说 A57 核心最高频率下运行,两者有至多 32% 的差别(dynamic power)。不过用户也没有必要太担心,因为出货设备情况呈泊松分布,绝大部分芯片 lambda (译者注:lambda 是泊松分布的均值,是指一个时间段内事件平均发生的次数,不过这一段一点也不重要,所以请忽略吧)落在 ASV10-ASV11 之间。我还没看到过有人收到 <ASV6 的设备,不过这也不意味着这样的设备不存在,只是比较少而已。我们这篇文章中测试的设备,所用芯片在 CPU 簇和内存控制器方面评级为 ASV10(图中的高亮部分),GPU 部分则为 ASV11。因此,主要 SoC 模块的测试成绩可能并不具有普适性。

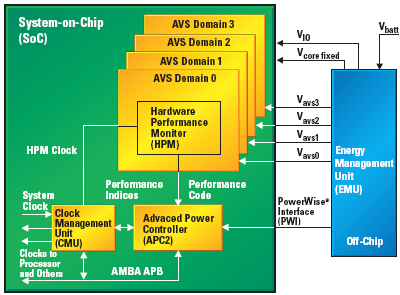

到目前为止,在电压的用词方面,我在提到“目标电压(targe voltages)”的时候都比较谨慎,另外尽管 PMIC 之上的降压变换器(High efficiency step-down voltage regulators)提供的电压可能并不完全准确,我这里提到的是另一种电压控制机制,和一般的软件 DVFS(动态电压与频率调节)控制不同。今年,三星在 Exynos 7420 中采用了一种新的闭环 DVS(动态电压调节)系统。闭环系统基于反馈回路,通过传感器(HPM,硬件性能监控器)持续监控输入。DVS 系统实际上就是一个微控制器和多个 HPM,其中的微控制器能够选择某个电压,让调节器采用这个电压。Exynos 7420 采用的是片上 Cortex M3 微控制器,三星将其命名为 APM,不过我不清楚 APM 代表什么,有可能是 Advanced(或 Adaptive)Power Manager 的缩写。

APM 仅通过小型 mailbox 信息与主系统进行通讯。mailbox 实际上是不同架构处理器之间通讯的一种方式,每个处理器只能将信息写入到自己的 mailbox(RAM 空间),但可以读取其他 mailbox。当发生频率变化时,运行在 Linux 内核之上的软件 DVFS 机制就发送目标电压到 APM。首先,内核与主 CPU 直接通过 i2c 接口对 PMIC 调节器进行编写,但在频率变化过后,控制权就转给了 APM,直到下次频率变化为止。APM 会依次去测量 HPM,两个 CPU 核心簇、GPU 和内存控制器之上都有 HPM。当 APM 发现电压阈值下降——可能是温度或者其他影响因素改变了芯片特性——APM 就会根据 ASV 分组(binning process)来进一步降低电压。

相比主 CPU 基于软件的解决方案,APM 的优势在于,它能够进行更为细粒度和实时的响应;能够在 1ms 间隔时间内改变电压,而主 DVFS 机制这一周期是在 20-80ms 的样子。电压步进取决于设备之上的 PMIC,就 Galaxy S6 来说,这也就意味着主降压变换器的步进为 6250μV。我有注意到,三星尝试了 APM 的不同电压方案(可进行 undervolt 达到最大效率),最终针对 CPU 核心部分电压在 25mV,而针对 GPU 和内存接口的电压为 12.5mV。

德州仪器的 PowerWise 技术也用了类似的闭环电压机制

德州仪器的 PowerWise 技术也用了类似的闭环电压机制

闭环电压调节系统本身并不稀奇,但三星将之与前文提到的分级流程(binning process)进行了配合。德州仪器是移动领域率先针对电压调节运用这种闭环系统的厂商,许多 OMAP SoC 产品中都采用了这种系统。德州仪器的 PowerWise AVS 是用作电源管理机制的,但更重要的是为了节约生产成本,德州仪器从生产链中去掉了产品特性鉴定(characterization)和 binning process 分级流程。高通骁龙 S810 以及英伟达的 Tegra K1 也转而采用闭环系统,但和德州仪器一样,他们也都抛弃了传统的分级电压表,仅依靠 HPM 来指定运行电压。

三星的 14nm 制程,搭配这种加强版电压调节系统,最终提供相较 Exynos 5433 和先前其他 SoC 更低的电压。对此,我仍然很好奇,这种电压减少究竟能走多远:A53 核心在不算 APM 成本的情况下电压大约 587mV。Exynos 7420 的内存控制器供给电压达到了最低:在 416MHz 频率之下,运行在 575mV。而 Exynos 5433 相同情况下从未低于 750mV。

今年早前我曾评论说,除了苹果,虽然三星相比其它供应商更早推 20nm SoC,但并不能造成明确的竞争优势,因为台积电的 28HPM 工艺 2014 年定的基调就很高。然而只过去几个月,我们就看到了完全不同的现状,因为三星在 FinFET 技术方面比台积电领先不止 6-9 个月。接下来 14nm 制程的行业竞争就会很有趣,因为三星和制程合作伙伴 GlobalFoundries 持续扩充生产能力,台积电也开始进行 16nm FINFET 节点的大规模量产。

进入 Exynos 7420 内部

不可否认,Exynos 7420 相比竞争对手显然有着更优秀的制程工艺,但在进入跑分、呈现性能方面的数字之前,我想做一件先前我们从没做过的事情:详细了解像 Exynos 7420 这样的当代 SoC 内部究竟是什么样。

过去这些年,SoC 变得越来越复杂,晶体管数量也在暴涨。但其实我们很少有机会了解,这些大规模设计,究竟包含了哪些模块。企业提供的公关稿只有一些简单的内容,比如说 CPU 的核心数、GPU 配置等。像高通这样的公司对于其 IP 甚至不会给出任何信息,比如 Adreno GPU 架构迄今都是个谜。三星 SoC 的主要处理模块可能很多人都知道,因为三星用的就是来自 ARM 的 IP,我们因此也有机会在文章中进行扩展,比如在 Mali Midgard 设计或者 ARM A53/A57 CPU 架构方面的深度挖掘。虽然我们对于 CPU 和 GPU 有着相对深入的理解,但对于 SoC 的其它组成部分,我们就知之甚少了,因为厂商从来也没谈过。

很不幸,我们去问了 Samsung LSI 有关 Exynos SoC 的细节,LSI 表示不会就现有产品的架构或细节做公开评论。为了了解更多,我尝试自己进行逆向工程,根据不同的 IP 模块,构建出了 SoC 的抽象概况。

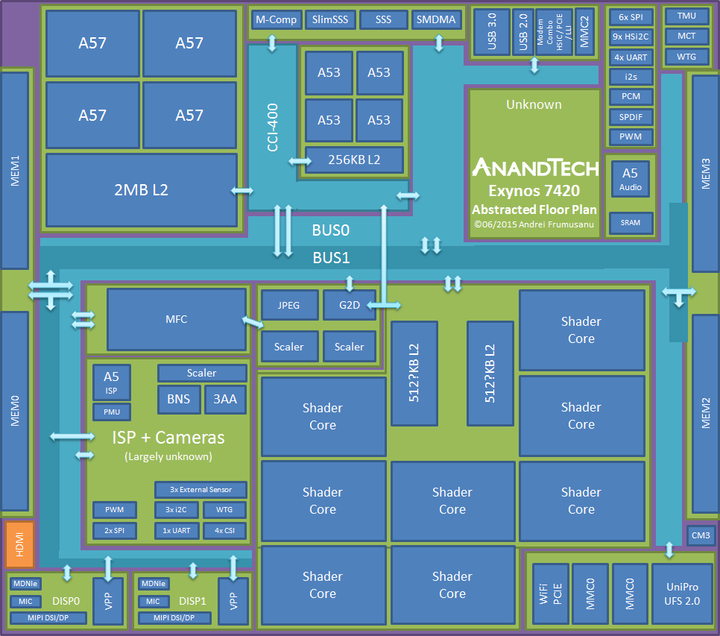

在谈不同模块和层级之前,我得搞个免责声明——这张图只是真实物理层面的抽象蓝图。根据我自己的分析,其实我们已经得到了芯片的 die shot(译者注:die shot 应该是说芯片的真实模块和层级分布),但我们无法把 die shot 公布出来。上图 GPU、CPU 和内存控制器模块基本可以代表其真实大小和位置,而为了展示,诸如 ISP 还有图的右上部分等模块都进行了简化。

在制程部分就已经提到,Exynos 7420 仍然是个很小的 SoC,其面积仅有 78mm²。其最大 IP 模块是 Mali T760 GPU,尺寸为 17.7mm²,占到整个 SoC 的 22.6%,接近 1/4 的占比。实际上从先前的 Exynos 5420 开始,三星就在为 GPU 做筹备。其中的 shader core 核心也是 SoC 独立模块中最为大型的模块之一,尺寸为 1.75mm²。8 个核心通过一条公共线路和 2 个 L2 缓存联通。三星官方先前就公布说,Exynos 5433 的 Mali GPU 总的 L2 缓存为 512KB。而 5433 与 7420 这两颗 SoC 的缓存与 shader core 尺寸差异表明,Exynos 7420 的 L2 可能更大(译者注:这句话原句是说 7420 的 L2 缓存与 shader core 核心之比更大,可以这样理解: Exynos 7420 所用 Mali T760 的 L2 缓存大小未知,但已知这颗 GPU 为八核心,从核心尺寸以及总的尺寸来推断,GPU 的 L2 缓存应该比 Exynos 5433 的 GPU 更大),每个 MMU 的缓存或翻倍至 512KB,意即总量 1MB。但悲剧的是,三星并未公布有关 Exynos 7420 的更多信息,所以我们也不能确定。

而在 CPU 部分,我们看到 Cortex-A57 “big”大核心簇(译者注:也有媒体将 cluster 翻译成“丛”或“集”,意思是一样的,本文统一将 cluster 译为核心簇)位于 SoC 的一角,和 GPU 位置相对。在 ISSCC 2015 大会期间,三星曾解释称这么安排位置是为 SoC 的温度管理考虑。将两个能耗最大的模块隔离到两端,能够让整个 SoC 的散热效率最大化。

Cortex A53 “little”小核心簇就位于 A57 簇一旁。Exynos 5433 这部分的配置相似,4 个 A53 核心,L2 缓存为 256KB。而 14nm 制程对尺寸的缩减,可能令其成为现有 SoC 中最小的四核心簇,尺寸仅为 2.71mm²。

两个 CPU 簇之间,我们能够发现 ARM Cache Coherent Interconnect(CCI-400 互联),这是不同 CPU 架构之间异构多处理的关键所在,也是 big.LITTEL SoC 的基石。除了 CPU 之外,CCI-400 也能连接另外 3 个 IP 模块,形成缓存互联。三星并未提供 CCI 及通用内部总线架构的公开信息。但针对 Exynos 7420,我至少可以确认 CCI 之上连接的 4 个端口(总共可能 5 个端口)。

两个 CPU 簇分别占用一个 CCI 端口,三星另外还选择令其连接 G2D 模块(和 GPU 是同一个端口),该模块全称叫 FIMG2D(Fully Integrated Mobile Graphics 2D,完整融合移动图形 2D)——这个模块是 Exynos SoC 的 2D 图形加速器,是 MSCL(2D 图形处理模块)的组成部分。这里的 MSCL 全称为 M-Scaler,不过我不清楚 M 究竟是指什么,可能是 Media。这个模块包含 2 个专用硬件级固定函数图形 scaler(译者注:scaler 的意思一般在这里是指尺寸的缩小和放大),以及一个 JPEG 压缩和解压单元。比如视频流就需要通过该模块,缩放至显示屏分辨率。

另外一个连接 CCI 的模块是种新型 IP,我们先前在移动领域从来没看到过:memory compressor(内存压缩),其正式名称叫 “Exynos Memory Compressor” 或者叫 M-Comp。有趣的是,这个模块尚未在 Galaxy S6 设备上发挥作用。我很确定,这是个硬件模块,是专门为 Android 系统设计的。从 Android 4.4 系统开始,内核 DRAM 压缩机制就已经成为系统的组成部分。所有设备都采用某种方式来实现该特性,大部分设备制造商采用的是“zram”机制,即采用 ramdisk(译者注:就是内存盘,或者早年很多人应该知道的虚拟硬盘)作为压缩支持。内核创建这部分 ramdisk,令其作为交换设备,存储较少使用的内存页。三星 Galaxy 设备从 Android 4.1 就已经开始这么做了。

而 Galaxy S6 采用更为高级的实施方案,名为“zswap”。这种方案能够在内存页移出交换设备之前对内存页进行压缩,显然这是个与内核内存管理核心靠得更近的优化机制。在某些 App 的多任务处理过程中,这种机制就会发生效果:实例显示,zswap 能够将 1.21GB 内存页压缩至 341MB 物理内存。将压缩任务交给专门的硬件模块,在能耗效率优化方面会产生相当不错的效果,所以我们很期待未来操作系统升级会有软件堆栈能够利用到这部分硬件单元。

这里的 memory compressor 本身属于 IMEM 模块,这个模块理应还包含其他一些组成部分,如 SSS(安全子系统)——这是个硬件加密加速器,从 S5PC110(后来改名叫 Exynos 3110)开始就是 Exynos SoC 的组成部分,它能够对加密和解密进行加速。其中有个 DMA 引擎,也就可以直接访问磁盘,实现快速全盘加密了。我不确定 7420 是否仍然留有该模块,因为似乎缺少驱动。有可能三星已经弃用 SSS,转而采用 ARMv8 的加密功能,但如果为能耗考虑的话,保留这样一个固定功能 IP 也是合理的。

ARM 公布的 CCI-400 布局实例,LG Odin/Nuclun SoC 就采用了这种设计,但 Exynos SoC 没有这么做如前文所述,G2D 模块和 GPU 共享一个 CCI 端口。这和 ARM 官方 SoC 配备的 CCI 也就存在较大差异了:我们看到的大部分 Mali GPU 都占用 CCI 两个端口,因为每个端口读写指令都为 128 bit 位宽。供应商普遍将 CCI 频率定在大约 DRAM 频率的一半,如今大部分是 LPDDR3 SoC ,所以其频率一般在 400-466MHz。遵从 ARM 这种总线架构官方方案的一个典型就是 LG 的 Odin(Nuclun),其 CCI 频率在 400MHz,内存控制器频率为 800MHz。所以给 GPU 接一个 128 bit 端口会对带宽产生限制:仅有 2 x 32bit 内存控制器可实现带宽的一半,对资源会产生浪费。而 Exynos 7420 也只把 CCI 频率定在最高 532MHz,这和 ARM 官方提出 DRAM 频率的一半规则并不相符,最终也意味着理论上,7420 的一个 CPU 簇无法让主内存带宽饱和。每个端口读取和写入指令带宽限制在了 8.5GB/s,并发也就是 17GB/s,这一点会在后面的 CPU 性能测试部分得到印证。

还有个 CCI 端口给了 CoreSight 模块,这是 ARM 的系统 IP,用于 SoC 的 Debug 和检测。

现在的问题在于,GPU 究竟是如何连接内存控制器的。有一点可以肯定,就是并非通过 CCI。三星将其内部总线架构称为“多层 AXI/AHB 总线架构(Multi-Layer AXI/AHB Bus Architecture)”。AXI 和 AHB 都是 ARM AMBA(Advanced Microcontroller Bus Architecture)已经定义的规格,这里的 AMBA 基本是现在所有 SoC 都会采用的互联标准。我们知道 7420 至少有两层大规模布局:一个“内部(Internal)”总线,我在概要图中将其标注为 BUS0,一个“内存接口(Memory Interface)”总线标注为 BUS1。另外还有一些没那么重要的外围总线没画,这些总线连接更小的低带宽 IP,这里不做讨论。

内存接口总线与 LPDDR4 内存控制器运行在相同的频率水平上,最高 1555MHz。内存控制器扩展到 SoC die 的两端。每个内存控制器都有 2 x 16bit 接口,直接连接到 DRAM die。也就是说 DRAM PoP 模块包含 4 个 DRAM die,64bit 总线带宽 SoC。我在尝试深入研究内部总线铺设时遇到最大的麻烦,就是理解内存控制器如何与各部分总线做交互。很明显,三星实际的总线架构比已经公开的信息要复杂的得多。除非未来有什么新的消息来源,我们现在能做的也就是猜测数据在芯片中是如何流动的。

主要 I/O 模块也是内部总线模块的组成部分,这些主要分成了两部分,分别叫 FSYS0 和 FSYS1。其中包含 3 个 Synopsis DesignWare MMC 控制器(2 x 8bit,1 x 4bit)——用于 eMMC、Wifi SDIO 和 外部 SD 卡连接。针对 UFS 2.0 的 MIPI UniPro 控制器当然也在其中,用于 Galaxy S6 的 NAND 存储。

去年我们看到 WiFi 连接实际已经从 SDIO 互联转向 PCIe 了。高通和三星针对其高端 SoC 都已经这么做了,那些 SoC 都已经包含 PCIe 控制器。采用博通 BCM4358 WiFi SoC 的 Galaxy Note 4 就是其中之一。博通方面表示,这种转变的原因有两个,其一是性能,PCIe 大幅降低了处理开销和 DMA;其二是能耗,PCIe 相比 SDIO 接口支持更低和更细粒度的低功率状态。

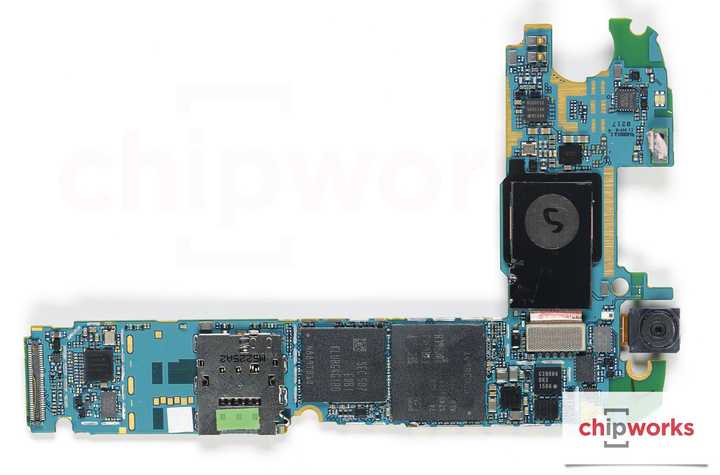

连接模块还有个有趣的组成部分就是 modem 连接模块了。三星在其驱动程序中将其描述为“Combo PHY”,支持 HSIC、PCIe 和 MIPI LLI。外部 modem 连接选择范围很广,一般一台设备就连一个 modem,所以将各种标准都融合进来也是合理的。Galaxy S6 首次在全球范围内采用自家 modem,即 Shannon 333,三星可能会在市场宣传时将其称作 Exynos Modem 333。三星自家 modem 以往的采用率限制在一定范围内,主要应用在韩国市场。从去年 Galaxy S5 Mini 开始,我们也就看到了三星在全球市场上的动作。

Galaxy S6 PCB 板,其上可见 SoC + DRAM 和 modem + NAND;UFS 模块位于 modem 上方(来源:Chipworks)

Galaxy S6 PCB 板,其上可见 SoC + DRAM 和 modem + NAND;UFS 模块位于 modem 上方(来源:Chipworks)

Shannon 333 通过 MIPI LLI(Low Latency Interface)连接到 Exynos 7420。这和以前相比,存在比较大的差别,就“集成”和“外置” modem 的问题。高通一直以来的优势地位在于,采用 all-in-one 的解决方案:单颗物理芯片在封装成本和 PCB 占用面积方面都有优势;而外部 modem 还需要专门的内存去运行。其实以前我们看到过很多这样的 modem,即便高通自己的 Gobi modem,比如说 MDM9235,也还是要搭配额外的 128MB LPDDR2 内存。而 LLI 连接,和传统的 HSIC(High Spped Inter Chip,USB 2.0 的一个衍生规格)不同,LLI 可让 modem 直接访问 SoC 的主内存,克服了外置 modem 一个大问题。Intel 应该是首个采用 LLI 连接 modem 的厂商,Galaxy Alpha 所用的 XMM7260 即是如此——和 Shannon 333 一样,它也去掉了额外的内存模块,同时减少了模块成本和功耗。

三星方面当然不会就此发表评论,不过 MIPI Aliance 联盟解释称成本和降低功耗的确是 LLI 的目标。三星在集成和独立 modem 问题上的选择也表明,后者在市场和 AP 性能特征方面也有着更好的收益,毕竟 modem 需要监管机构和运营商认证,这个过程需要耗费不少时间和金钱,而且现在将芯片投入到量产设备上的速度也需要足够快,因为行业正在以每年一更的速度前进。另外工艺结点也变得愈发复杂和昂贵,为效率和成本考虑,将 modem 和主 SoC 分开可能也算是合理的选择。

在我看来,三星未来仍然会在高端产品中采用双芯片策略,而中低端市场仍采用集成 modem,后者对成本也更为敏感。Galaxy S5 Mini 手机中所用的 Exynos 3470 可能就是集成 modem 的 ModAP SoC 产品,我们发现八核 A53 的 Exynos 7580 就采用了集成的 Shannon 310 modem 和 LPDDR3 内存,这应该是颗中端定位的芯片。(译者注:ModAP 就是三星将应用处理器和 Modem 集成到一起的解决方案,实际上 Galaxy S7/S8 所用的 Exynos 8890/8895 都用了这种集成方案。)

我们再回到 SoC 和 IP 模块。每颗 SoC 都需要通用连接,Exynos 7420 也不例外。它提供各种必要的总线接口,可将所有设备组件连接到中央 SoC,包括 SPI、HSi2C、UART、i2s、PCM、PWN 等。我获得了可对其进行抽象展示的许可,但也不会展示其细节,包括位置、尺寸之类的确切信息。

其中有个我不认识的模块,位于 A53 核心簇旁边,而且面积还挺大。我不确定这个位置究竟是什么,可能是部分小型 IP 或者通用 SoC 逻辑的集合。

早前三星曾经在 Exynos 5430 之前的 SoC 上用过一个 Coarse-Grained Reconfigurable Architecture(CGRA,粗粒度可重构体系结构)处理单元,名为 Samsung Reconfigurable Processor(SRP),用于音频处理。SRP 是个挺有趣的结构,三星似乎期望将其应用到各种使用场景中:我们见到过用其构建的原型 GPU,三星现如今将其用在单反(如 NX-1)DRIMe-V SoC 之上。而在 Exynos 5430 和后来的 SoC 中,这一音频模块就被丢弃了,改换成了更为常见的 ARM Cortex A5——这部分就用来负责音频解码、编码,以及音频处理任务,如均衡器功能。三星先前还曾宣传说它可以用作音频处理和音频识别。

最后我们来看看 SoC 的 media 媒体部分。这里有 ISP,硬件媒体编/解码器,以及显示流水线(display pipelines)。

SoC 的这部分图示,实际上和真正的物理层面布局是完全不一样的Exynos 的硬件媒体加速器名为 Multi-Format-Codec(MFC)。这已经是个比较成熟的模块了,早在 2007 年的 S3C6400 中就已经有了。不过虽然这部分的存在已经长达 8 年,我们对于其架构仍然一无所知。我觉得这很可能是个定制 DSP 结构,因为其运行需要加载单独的固件。此 IP 能够编码和解码 MPEG4、H263、H264、VP8 和 HEVC,另外还能解码 MPEG2、VC1 和 VP9。Exynos 5430 和 5433 在 MFC 之外还采用了额外的 HEVC 解码器模块,用于进行相应视频格式的播放,不过 7420 已经将这些都融合到了 MFC 中。

我一直都觉得三星的硬件解码器在性能和功耗表现方面很棒,这次 7420 中 MFC v9 也不例外。播放 4Kp30 Main HEVC 视频的整机功耗仅为 950mW(为让显示屏功耗降到最小,屏幕采用最低亮度、竖向模式)。这表明系统负载功率约仅 600mW。CPU 负载很低,两颗 A53 核心运行在大约 400MHz,占用 25-30% 上下。但很可惜解码器不支持 Main10(10bit)播放,且在播放 4Kp60 内容 2 秒后停止工作,这可能不满足某些用户的预期。高通骁龙 810 解码单元也存在这样的限制。

在媒体相关模块中,我们找到了 ISP。我们对于三星的 ISP 知之甚少,但这肯定是个相当先进的 IP,毕竟三星还能够从其自家的相机 SoC 产品线中汲取到经验。这块 ISP 包含一系列通用模块,如运行在 668MHz 频率下的 Cortex A5,以及不少固定功能的单元。

来源:三星2013 年三星公布的有关 Exynos 5420 的 paper(译者注:直接点击这个链接可能无效,有兴趣的请在 Google 中搜索 Benefits of Exynos 5420 ISP for Enhanced Imaging Experience)中提到过 ISP 架构。其中解释了整个 ISP 是由一系列子 IP 构成的,每个子 IP 都有其专门的工作,比如传感器缺陷补偿、3A(Auto-focus 自动对焦,Auto-exposure 自动曝光,Auto-white-balance 自动白平衡),反拜耳(de-mosaic),帧间抑噪(inter-frame noise-reduction),相位检测自动对焦,陀螺仪数字图像稳定,光学镜头校正,脸部识别,视频稳定,以及各种图像处理特性。这块 SoC 有 4 个 CSI 端口,似乎支持 3 块图像传感器。

最后我们来看看显示流水线,三星称其为 DECON,全称叫 Display and Enhancement Controller(显示与加强控制器)。DECON 模块负责硬件级合成。移动设备利用硬件层——即它们将内容绘制到不同的帧缓冲区(frame-buffers),再用硬件单元将其重组形成最终图像。比较常见的例子如 Android 的状态栏窗口(Status Bar Window),状态栏活跃时,系统不需要对整个屏幕进行重新渲染,只需要重绘状态栏,然后让硬件单元进行合成。视频播放窗口和应用覆盖层(overlay)也是以类似的方法工作的。

除了一个单独的 HDMI 输出之外,Exynos 7420 有两个主要显示控制器。这两个控制器都支持 MIPI DSI 或 DisplayPort 输出,虽然我不确定其完整规格,比如支持的分辨率、帧率。两个显示控制器之上的 Video Post-Processor(VPP)是以往的 SoC 从未出现过的,但我也不确定这个模块究竟是用来做什么的,似乎支持色彩空间转换,针对某些任务还会采用多相滤波器。此外,显示控制器上还有个名为 MDNIe(Mobile Digital Natural Image Enhancement,移动数字自然图像加强)的模块,这个模块用于图像色彩处理、锐化和其他大量效果。有了这个模块,三星设备就能针对不同的标准采用不同的显示配置了。值得一提的是,三星在外置的 AMOLED DDIC 上也有类似的模块,为没有采用 Exynos SoC 的设备提供功能。

早前的 Galaxy Note 4 评测中,我提到过 MIC(Mobile Image Compression,移动图像压缩):高于 1080p 分辨率的显示屏,数据从 SoC 传输至 DDIC 时,所需的图像带宽超过一般 4 通道 MIPI DSI 接口所能提供的带宽。为了驱动 1440p 以及更高分辨率的屏幕,供应商就需要采用双 DSI 配置,采用 8 通道,这也会造成双倍的功耗。还有一种方法就是压缩数据流,三星是目前唯一一家采用这种解决方案的供应商,即其专有的 MIC 压缩机制,而未来的行业标准 DSC(Display Stream Compression)尚无产品问世。

这两种方案都有个局部更新特性,即如果屏幕仅有一部分内容更新,那么压缩算法也只更新和传输这部分图像,这样一来还能进一步节约能耗。通过 MDNIe 模块改变、增大图像颜色参数可以确认这部分功能存在。在改变色彩配置之后,显示屏控制器不会刷新整个图像,而只是向 DDIC 发出了部分更新。这样一来,屏幕仅有一小部分需要更新色彩,也就是说 SoC 仅传输一部分屏幕数据,静态内容直接在 DDIC 之上进行缓存。

总的来说,Exynos 7420 是颗很有趣的 SoC。就其 78mm² 的尺寸,若增大面积会有更好的表现。很可能是三星故意采用这种尺寸,达到更好的销量预期,毕竟这是三星首颗 14nm 大规模量产芯片。或者也可能是 14nm FinFET 成本还没完全降下来,所以这可能会是个新趋势,以后超过 100mm² 的 SoC 都可能不再会有。所以未来几年内很有必要观察移动半导体供应商的发展方向,制程会逐渐成熟,产量也会上去,三星、GlobalFoundries 和台积电都在着手扩展 FinFET 大规模量产。

CPU、存储性能与设备拆解

接下来我们来看基准测试部分,考察 CPU 性能和功耗。在先前的 Exynos 5433 评测中,我们就已经谈到了 ARM A5x CPU 架构,如果你对这款 SoC 中的 CPU 设计感兴趣,一定要去看一看(译者注:老泪纵横,等我迟点去给各位编译下)。在 CPU 配置方面,Exynos 7420 和 5433 差不多,同样是 4 个 A53 核心和 4 个 A57 核心,通过 CCI-400 互联连接。唯一的区别在时钟频率方面,三星将小核和大核的频率分别推到了 1.5GHz 和 2.1GHz。

CPU 性能:64 位处理

先前 Exynos 5433 之上,有项跑分测试我们无法进行,即 AArch64 状态性能——因为仍采用 32 位软件堆栈。这次,我们为 Exynos 7420 采用针对 32 位和 64 位目标编译的 SPECint2000 进行测试。下面的得分只是个概数,可能无法代表设备性能,仅代表 CPU 性能的架构表现。

SPECint2000 是由 Standard Performance Evaluation Corporation 开发的,SPECint2000 是 SPEC CPU2000 基准测试的整数测试部分。SPEC CPU2000 实际上已经退出 PC 处理器测试舞台,不过移动处理器在性能方面相较 PC 是相对落后的。这项基准测试仍然能够为现如今的移动手机提供跑分成绩,用以进行 CPU 设计的单线程架构对比。下面公布的跑分仅是概数,不应该当成正规的有效成绩。

首先,从 AArch64 代码的 A53 核心性能表现说起,我们发现一件奇怪的事:即 64 位跑分结果有时比 32 位差。各子项之间存在差异。如 mcf 或者 crafty 这样的项目明显表现不佳,CPU 内部需要处理更大的数据。在这些测试项中,缓存压力变大,也就降低了运算速度。但其他一些子项却表现出了较大的提升,如 gcc、perlbmk 和 gap,这些项目在运算过程中能够利用 64 位寄存器和其他 ISA 变化。若运行此类代码,则 A53 核心会有 2-4 倍速度提升。

A57 部分的情况相似,64 位 vpr、mcf 和 crafty 相较 32 位版性能大幅降低,内存和缓存压力变大。而 perlbmk 和 gap 利用了 64 位寄存器,成为提升幅度最大的测试项。A53 核心得分中,gcc 编译器 64 位相较 32 位也有较大提升,A57 部分的领先幅度就没那么大了,但也有 28% 的性能优势。

很明显这种性能优势与架构、使用场景有很大关系。性能倒退最严重的两个测试项是 181.mcf 和 186.crafty,前者基于单点(single-depot)媒介调度算法,采用几乎唯一的整数运算方法,无法利用 64 位数据结构,所以大部分性能浪费了。

值得一提的是,Galaxy S6 仍然采用 32 位原生浏览器,不知道是故意为之,还是固件的历史遗留问题。这也可能表明,转而采用 AArch64 编译应用不一定会产生积极效果。

存储延迟和性能

LPDDR4 对 2015 年的不少高端 SoC 而言是个比较重要的规格升级,如骁龙 810 和 Exynos 7420 就是首批采用支持 LPDDR4 的 SoC。LPDDR4 在运行频率方面相较 LPDDR3 翻倍,Exynos 7420 的内存频率为 1555MHz(3110MT/s)。从计算需求来看,CPU 对于延迟更为敏感,GPU 则要求更多的带宽,才能保证最高效率运行。首先,我们要看看 Exynos 7420 内存延迟方面的变化。下面这张图采用对数刻度,这便于呈现 L1 和 L2 缓存间的延迟差异。

A53 核心部分,L1、L2 的结果差异没有超过 15%,这是符合预期的,Exynos 7420 略微调高了小核心的时钟频率。随传输尺寸超过 256kB,我们的测试就脱离了 L2 缓存部分的预取(pre-fetching)和缓存(caching),抵达主内存。此处 Exynos 7420 延迟增至 206ns,而 5433 为 191ns。

主内存延迟方面的变化也比较明显,导致带宽结果方面,7420 小核心相较 5433 的测试结果传输速度平均降 10%。

大核心部分就比较有趣了,Exynos 7420 大核心的 L1 缓存存在较大变化。相较 Exynos 5433,Exynos 7420 L1 缓存延迟表现提升了多达 76%,两者 A57 核心 L1 延迟的具体数字是:7420 稳定在 1.91ns,而 5433 平均为 3.36ns。实际上,7420 的频率优势仅有 10%,所以三星肯定在缓存架构方面做了一些改进,所以其延迟和带宽表现在我们的测试中才如此稳定。

L1、L2 缓存带宽测试结果差异也比较大:相比 Exynos 5433,7420 的 L1 带宽平均提升 89%,L2 也有 46% 的提升。NEON 载入指令似乎部分得到了很大提升,相比 Exynos 5433 的 A57 核心簇,我们测得 7420 的 L2、L1 缓存带宽有 2.4-3.1 倍提升。

在抵达主内存之后,延迟和带宽差异就变小了。Exynos 7420 的 A57 核心簇表现仍然比 5433 更好,主内存延迟略微减少了 8ns 至 172ns,内存带宽平均提升 4%。CPU 当然不会受限于主内存,毕竟离塞满 CCI 之上的总线带宽还差得远。前文讲 SoC 布局的部分中提到过,三星将 CCI 频率限制在 532MHz,而没有为了配合 DRAM 速度提升这个值。这和其它 SoC 就不一样了,高通骁龙 810 的 CCI 频率最高至 787MHz。

总的来说,三星针对 A57 核心进行了一些优化,以提升存储(memory)性能方面的表现。性能提升幅度超过 10%——也就是超过 200MHz 应有的频率提升,而且也没有受到 AArch64 指令集使用的影响,这可能和更高的核心、核心簇缓存性能提升有关,但这也很难确定,我们并没有发现 7420 与前代 SoC 架构间的更多差异。

离个题:Galaxy S6 拆解

在谈具体的性能之前,我想分享有关 Galaxy S6 拆解的经验,毕竟很多读者可能对于如何更换电池比较感兴趣。而拆解最麻烦、耗时的步骤就是将后盖玻璃取下来的过程。

Galaxy S6 背面所用的第四代大猩猩玻璃,以非常牢固的粘合剂粘在设备框架边缘位置上。所以就需要强有力的吸盘和吹风机(如果没有热风枪的话)才能搞定了。我用的是汽车上的 GPS 固定吸盘,这货比较牢靠,而且还能形成可撬动的杠杆。粘合剂需要到较高的温度才会软化,所以需要将设备加热到已经无法握持的程度才行。另外你还需要准备个薄片。要撬的话,一开始要从设备底部,扬声器位置下手。要把薄片或者尖锐物插进去,第一把真的需要比较大的力气,胆小的人绝对搞不定。沿着边缘,一边加热一边撬开玻璃盖板。

后盖取走以后,剩余的步骤就比较简单了——内部用的都是常规飞利浦螺丝。所有螺丝都取下之后,沿着显示屏前沿加热。按住电池部分,从屏幕和主板分离出整个一体框架。对于 Galaxy S6 而言,到这里就差不多了,电池已经可以看得到——断开连接器,将其小心与显示屏分离即可。而 S6 edge 还需要进一步分离主板,因为电池连接器弯折到了 PCB 板背面。

组装的过程不难,连接电池后逆向操作即可。不过组装的时候要保证玻璃背板上的粘合胶条平整,否则的话,装上去之后背板会翘起来,和金属框架不呈水平面。手机组装完毕后,我建议再次沿着设备边缘加热,并挤压玻璃背板,将整个后壳组装到位。

替换电池的过程大约需要至多 30-40 分钟,取决于你卸下玻璃背板有多努力...我们需要看一看,三星采用最新的电池成分,在 1 年的持续使用和快充过后表现如何。但如果需要更换电池的话,鼓起勇气,这还是可以搞定的。

CPU 功耗

功耗部分的测试可能是最受关注的,的确这部分测试结果是能够反映 14nm 制造工艺在能效方面的表现的。为此,我们给 Galaxy S6 加装外部电源和电能表。

结果中标注“负载功率(load power)”表示闲置功耗,与相应场景总功率之间的差异。也就是说,在某个特定测试场景下,我们会在设备未执行任何活动的情况下对设备功耗进行测试,不过屏幕会显示相应内容。这种测试方法可抵消屏幕和各种设备组件产生的功耗。控制设备的电源管理和性能,我们就能得到相当精准的数据。值得一提的是,这种测试方法仍然无法具体到 SoC 的常规使用模块,如互联(interconnects)或 DRAM。

我们首先看看 A53 核心簇,及核心功耗。测试采用一款功耗程序(power-virus),人为地干预 CPU 核心加载过程。这样一来就能了解特定频率下的最大功耗了,于此得出下面的曲线图:在不同频率和电压水平之下的功率。现实使用场景中较少出现 CPU 满载的情况,大部分高负荷场景也仅在特定频率下占用 CPU 资源的 80%-90%,功耗也是如此。

测得的功耗较大程度遵循 P = C * f * V² 动态功耗公式,即频率(f, frequency)乘以电压(V, voltage)的平方,乘以代表 IP 模块电容的的一个常量(C, constant value)。半导体制造商一般在温度管理驱动中会遵循这一公式,它能够表现大致的功耗。

从上图可见,Exynos 7420 的小核心加载至多 4 个线程的时候,会达到最高 1W 的功耗。这比我们在 Exynos 5433 之上测得的值稍高,可能和前者增加的 200MHz 频率有关。而 Galaxy Note 4 测得最高电压达到了 1150mV,Galaxy S6 最高为 1037mV。上述动态功耗公式 fV² 项可以算得,7420 的值为 1613,而 5433 为 1719。也就是说,仅考虑电压和频率,7420 虽然时钟频率更高,但功耗更低。可能是由于全新的芯片实施方案和布局设计,电容增大。这个公式中的常量也有结果了,Exynos 7420 的 A53 核心相较 5433 有更高 30% 的电容。

我先前在测试过程中,发现 Exynos 5430 的一个奇怪现象,随着线程数的增加,其功率增量减少。ARM 当时解释说,这是因为 A7 核心争抢核心簇资源所致,每增加一个线程会导致收益递减,这是因为每个核心执行的任务变少(因此功耗变少)。原本我们以为 5433 的 A53 新架构能够避免这样的瓶颈,所以 5433 增加线程功率递增。但 7420 表现出和 5430 同样的问题,也就是说这个问题并非核心架构特性所致。我无法确定问题出在哪里,可能只有三星知道了。

核心平均最大功耗(core average maximum power consumption),指的是核心 1-2、2-3 和 3-4 之间功率差异间的均值。测得的核心平均最大功耗曲线低于 1 个核心的功率曲线图,它尝试要呈现的是在 CPU 工作时,包括核心簇、互联、存储等脱离低功耗状态时的非 CPU 功耗。虽然 Exynos 7420 的 A53 核心最大功率高于 5433,但效率提升 30-40%(每 MHz 能效)。14nm FinFET 带来的电压降低,远比增加的电容有价值。

SoC 的静态漏电,我没法进行有效测试,我有和三星取得联系,不过没有得到明确答案。

在屏幕显示全黑的闲置状态下,Galaxy Note 4 的 Exynos 芯片最小功耗为 440mW,而 Galaxy S5 LTE-A(S805)功耗为 354mW。魅族 MX4Pro、华为 P8 分别最低功耗为 530mW 与 500mW。Galaxy S6 则可下探至 330mW,相较其它手机有 25% 的功耗优势,但仍然比不过去年的 Galaxy S5。这个值也是相当重要的,因为它代表使用设备期间不可避免的持续性耗电(屏幕关闭后的深度睡眠状态,会为 SoC 供电,而关闭设备的其它组成部分)。

除了 SoC 之外,显示控制 IC 也是主要耗电项目之一,它用于驱动 LCD 或 AMOLED 设备的像素阵列。ARM 先前就曾和我们分享过,测试 Galaxy S5 显示部件的电压变化情况。在屏幕显示纯黑的情况下,其功率值大约为 90mW。由于 Galaxy S6 采用 1440p 分辨率的屏幕,所以这个值应该会更高。

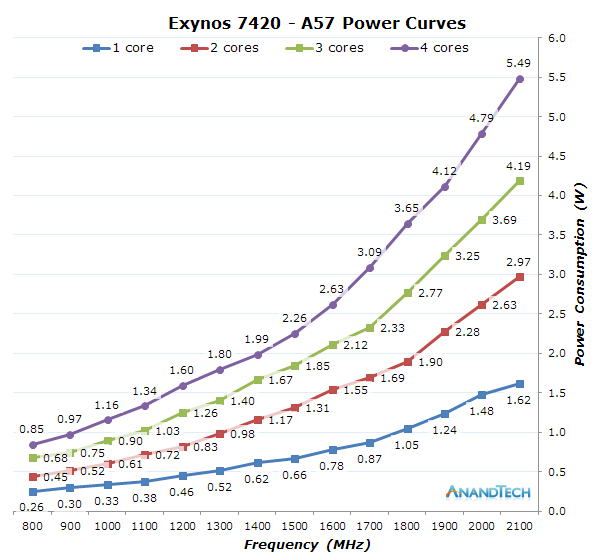

而在 A57 核心部分,我们理应看到在功耗表现方面更大的提升。我在 Galaxy Note 4 的评测中提到,三星给 Exynos 5433 定的时钟频率太高,功耗增加换来的那一点性能提升(最终的 200-300MHz)可能是不值得的。我们首先还是来看一下不同线程下的功率曲线。

Exynos 7420 的 A57 核心最大功耗在 5.49W,相比 5433 的 7.39W 显然合理的多。如果要看效率,则差距更大,Exynos 7420 在 1.9GHz 频率运行时,功耗为 4.12W,这个频率下 5433 的功耗就是 7.39W。和 A53 核心一样,三星可能的确充分利用了新工艺的优势,最大 CPU 电压从先前 1.9GHz 频率下的 1.235V(Exynos 5433),降至现在 2.1GHz 频率下的 1.037V(而 1.9GHz 频率下则为 0.962V)。更低频率的表现更出色,700/800MHz 频率下的电压从先前的 900mV 降至 675mV。

核心平均最大功耗见上图,Exynos 7420 功率大幅减少,在整个频率曲线上,其整体功率下降达到了 35%-45%。在 1900MHz 频率下,Exynos 7420 功率将近仅有 5433 的一半,这个成绩是非常出色的。A57 之上的电容也略有提升:7420 芯片中大核心有容量更高 10% 的电容,没有 A53 核心中增加得那么多,但在物理实施层面仍然是值得注意的变化。

PCMark 基准测试能够表现人们日常使用手机的使用场景,用它来衡量设备的整体效率是比较有价值的。我们测量了整台设备的功耗,因为我们无法在动态测试中刨除屏幕的功耗。

测试期间,设备的整体功耗表现很不错,其中 web 网页测试相较其它设备表现出最大优势,总功率仅 1.42W——相比 MX4Pro 和 Note 4 低了超过 1W。总的来说,Galaxy S6 是我们目前测试中功耗表现最出色的设备,这和设备与 SoC 一定是分不开的。

和性能跑分相结合,得到每瓦特的性能表现,Galaxy S6 相较其它设备也有 1.5-2 倍的提升。Galaxy S6 的 OLED 屏幕当然本身在效率方面就有加成,但能有这样的提升仍然是相当出色的。也就不难理解为什么三星为 Galaxy S6 选配了 2550mAh 的电池了,因为其效率足够高。

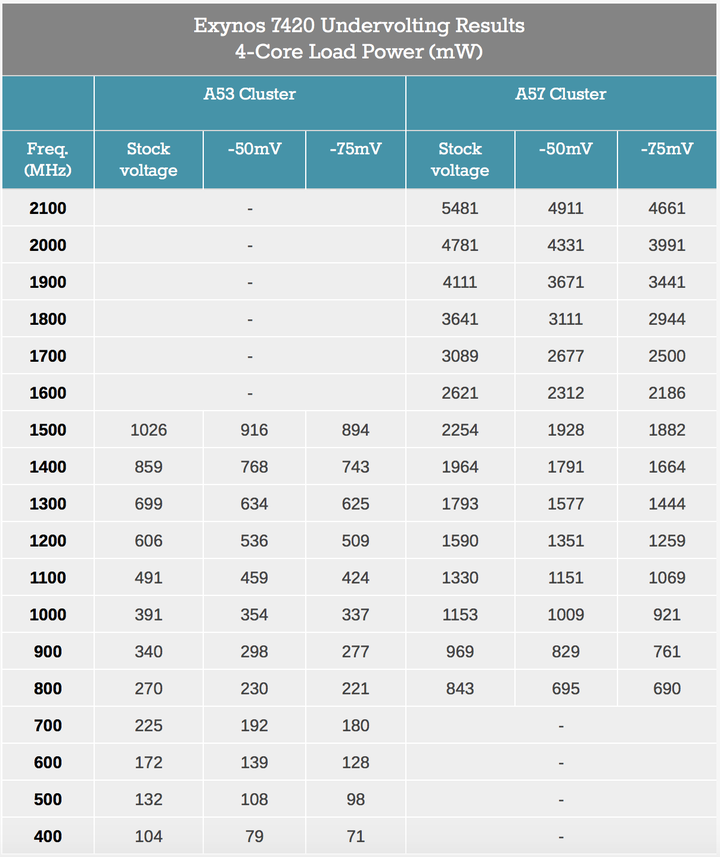

我先前拿到 Galaxy S6 评测机的第一件事就是编译一个定制版内核,这样就能得到 SoC 电压数据了,主要是要看这颗芯片在降低电压方面究竟能走多远。然后开始执行 undervolting 操作。undervolting 实际上和 PC 领域的超频有点类似的意思,对发烧友而言是比较流行的操作,可以压榨设备的潜能。对移动设备而言,我们要获取的是尽可能好的能效,而不是超频获得更高频率——因为对移动设备而言,不足以承担发热和功耗的后果。

(译者注:undervolting 是指通过软件减少 CPU 电压的过程,以零成本的方式获得更好的散热与功耗表现。应该说 undervolting 是不会对性能造成影响的。其实前文就已经提到了,工厂造出来的芯片并不是完全一致的,每颗处理器可能都有不同的电压容差。为稳定考虑,芯片制造商会为所有的芯片设定一个完全稳定的标准电压,一般这个值会比较高——Undervolting 就是要充分利用这一点来减少电压。)

为了让过程简单化,我针对 A53 与 A57 核心的原生电压分别全局施加 -50 和 -75mV 的 undervolting。如上图所示,在减少电压之后就能获得非常可观的能效。如果你有原生电压和原本的功耗数据,那么功耗缩减理论值也很容易计算。应用下面的公式就能大致算出在 undervolting 操作后的功率:

比如说,A57 核心在 2100MHz 频率下,可以这么算:5481mW/(1.037V²/0.987V²)=4965mW。这个数字和测得的 4911mW 是相近的。差异应该在于这个公式没有静态漏电,另外还有最重要的发热。

所以如果用更低频率来套用这个公式,就会更为准确,比如 1GHz A57:1153mV/(0.712V²/0.663V²)=996mV,和测得的 1009mW 更靠近。

实际上这里的 undervolting 操作还能进一步下探到 -87.5mV,但要找到最低的稳定电压还是比较有难度的,因为在相应频率、相应电压下要完整测试稳定性需要好几周时间。SoC 的温度在此仍是个未知数,提升晶体管电压阈值,则芯片会相对更“冷静”。进行 undervolting 操作,在“冷静”到某个程度之后,就会造成设备不稳定或崩溃——但可能在此电压之下,持续保持设备活跃倒是可以完美运行的。对设备的通常使用而言,如果发现不稳定,则情愿让电压回升一些。三星的闭环电压控制对 undervolting 而言也是个很有趣的机制,因为这种机制不需要牺牲稳定性就能进一步降低安全阈值。我对 Galaxy S6 进行 -50mV 的 undervolting 操作后,再将其作为主力机使用,最终发现将 undervolting 设定在 APM 允许的 -37.5mV,则一切完美!

CPU 电源管理

三星先前 big.LITTLE 架构 SoC 的电源管理是比较失败的,效率优化不怎么样。Exynos 7420 在这方面有一些加强,部分与 14nm 工艺提升有关,和软件方面的提升也有关系。

当代 ARM CPU 的电源管理有多种不同的方式。首先是 DVFS(动态电压与频率调节)机制,在不影响性能的前提下以最低可用频率运行,起到优化能效的作用。由于频率越低,工作电压就会越低,针对特定工作负荷就减少了能量损耗。这种性能状态的切换,是由名为 CPU 频率调速器执行的——它在 Linux 内核的 CPUFreq 框架中工作。

谷歌自 Android 4.1 Jellybean 开始,就采用“交互式”CPU 调速器(CPU governor,频率调节器,以下全部译作 CPU 调速器),这已经成为 Android 的组成部分——大量设备都将其作为默认的调速器,不过供应商也可以对其进行修改。这种调速器其实概念也比较简单:在特定采样时间(20ms)内,检查 CPU 负载。如果工作量超过现有频率下的目标负载,则在目标负载阈值(target load threshold)内,改变频率、适应当前工作量。这里的目标负载阈值,实际是个参数,用以描述在 CPU 调整至 P-state 状态时,我们期望的 CPU 资源百分比。如果工作量增加太快,极大超过目标负载,就会有个名叫高速负载阈值(high-speed load threshold)的东西,将 CPU 激进地调整到某个更高的固定频率,对 Exynos 7420 而言,此处 A53 和 A57 核心的频率分别为 900MHz 和 1200MHz。如果工作量稳定下来,且 4 次采样——也就是 80ms 期间,最新计算的目标频率持续变低,则将频率调整回更低的状态。

三星尝试对这种交互式调速器进行优化,引入了一些新的运行模式,能够动态切换交互式调节机制的可配置性,通过这种方式来提升 big.LITTLE 架构的调度能力。比如说,仅有一个 CPU 大核心超过 95% 的负载阈值,则进入到“single-load(单负载)”模式,为更方便地提升频率,这种模式可以减少调节阈值;同时针对小核心创建 QoS 最小频率请求。我不确定,为何大核心负载较高的时候,他们还会去提升小核心的频率,不过三星可能对频率调节做了比较深入的剖析,最终认为这么做会产生比较好的收益。单负载模式之上还有另一种模式,即当 4 个核心的累计负载超过某个值时,就会触发这种模式。这种多负载(multi-load)模式通过让核心更松弛,更容易将频率调整到更高,来再次改变调节参数。

实际上,这些已经应用到了 Exynos 5433 之上,只不过由于 5433 仍采用默认参数值,在调节机制方面没有提升,所以就没有发挥作用。Galaxy Alpha 所用的 5430 就开启了这种设定,而魅族 MX4Pro 却没有,所以这种设计方面的变化可能会显得比较犹豫,相对合理的解释可能是为将来做准备的。

这些变化显然是为了加强性能,以及 DVFS 调节的响应时间,Exynos 7420 在这方面的表现显然是比较好的。三星在频率调节方面表现比较出色,就是因为调速器不错。另外还有大量驱动的 QoS 机制,可持续向 CPU 发出请求,转至最低频率。比如说屏幕触控 booster:这是个独立的调节机制,能够控制两个核心簇的 CPU 频率,以及让 scheduler 强制迁移到大核心之上,获得更出色的响应时间,在显示屏驱动从触控控制器接收到中断请求后就立刻进行 UI 响应。还有比如,媒体流水线中的 IP 模块,诸如 2D composer 或者硬件视频加速器,这些模块在所需存储带宽和 CPU 资源方面,完全是可以预测的,所以其驱动会就 DVFS 机制动态设置性能水平,保证输出。三星另外还针对 NAND、modem、WiFi 和 IPC(Inter-process calls)通讯,为其 I/O 带宽采用了 QoS 系统。

除了 DVFS 调节机制之外,现代设备的电源管理机制也提供时钟和功率门控。对 CPU 而言,这又是个内核控制的部分,位于 CPUIdle 框架机制之中。以前,硬件还没有这样的节电机制,让系统空转一般也就是跑 NOPs(no operation)的无限循环,直到有任务将其中断。现在已经不这么干了,scheduler 会调用 CPUIdle governor,令其执行“nothing”。CPUIdle governor 统计每次闲置时间多久,基于这些数据就能从各种更深或更浅的硬件闲置状态中进行选择了。从 ARM 的 A15/A7 开始,这就基本整合到了 3 种所谓的 C 状态中:名为 WFI(Wait-for-interrupt)的时钟门控状态、单独核心功率门控状态、核心簇功率门控状态。

WFI 是个指令级和架构电源管理状态,以极低延迟,针对相应 CPU 来停止时钟。停止时钟,就能避免 CPU 的动态泄露,这对移动 CPU 的闲置状态(doing "nothing")而言是很重要的。而单核心功率门控状态,则能够关闭相应 CPU 的电源。这就是个比较深度的状态了,CPU 需要在切入时存储状态,唤醒时恢复状态。7420 中,这部分退出延迟为 100μs。由于恢复 CPU 状态本身存在开销,缩减时间周期(residency time)的话,进入这些模式其实就不划算了。某个核心簇的所有核心都处于闲置状态时,整个簇可以关闭。这种机制的开销肯定更大,退出延迟更长(300μs),最小 residency time 时间也更久(5ms)。这种核心簇关闭的机制主要应用在大核心上,小核心仅在屏幕关闭时才可关闭。另外,三星还做了一件事情,针对每个核心簇采用优化配置值——先前的三星 SoC 比较奇特,只用一个驱动,为两个核心簇采用相同的设置,这对 CPU 的闲置效率是存在影响的。

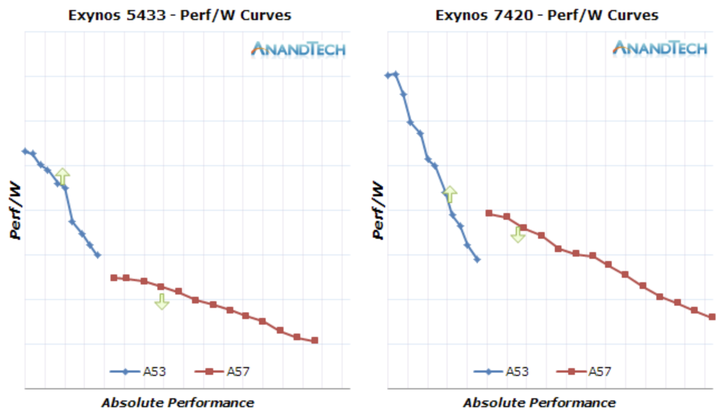

这次的 14nm 工艺给 CPU 的两个核心簇带来的变化似乎存在差异,两个核心簇的调节效率有区别。这对 GTS scheduler 设定存在较大影响:和 Exynos 5433 相比,7420 两个核心簇的能效曲线贴得很近。我对两个核心簇进行 SPECint2000 跑分,确定两个架构间的 IPC 差异,得到 A57/A53 的每瓦性能(perf/W),再除以时钟频率(Perf/MHz/W),得到下面的曲线。A53 核心曲线对应的纵轴就是标准的 MHz/mW,而 A57 核心曲线多算了一个 2.09 的乘数,调整效率值,可代表大核心的 IPC 提升。

(译者注:有关 2.09 这个乘数,我是不大懂的,也不知道为什么要这么做,为了数字比较方便?原话是这么说的:

On the first set of charts the vertical axis is just an arbitrary normalized value of MHz/mW for the A53 cores, and the A57 curve uses a multiplier ratio of 2.09 to scale the efficiency value and thus represent the IPC increase of the larger architecture.

欢迎理解的同学指教。)

首先我想解释一下,为什么 perf/MHz/W 曲线是相当重要的一个值。现如今的 Linux 内核与 GTS 机制会观察频率调节负载,如果某个进程占到 CPU 资源 50%,其当下的运行频率为 500MHz,而其最高可调节频率为 1GHz,那么 scheduler 就会将该任务视作占 CPU 负载的 25%。这种机制旨在以 CPU 本身最大资源为参考对象,对现有任务进行负载规范,而不是以 CPU 当前状态为对象。

GTS 机制中,线程迁移的触发点名为 up-threshold 和 down-threshold,这两个触发点也就是 CPU 负载调节的阈值。在 Exynos 5433 中,三星将 50% 和 25% 作为 up-threshold 和 down-threshold。当某个线程超过 A53 核心资源的 50% 时,就会迁移到大核心;而一旦大核心上的某个任务所占资源降到 25% 以下,则会迁往小核心。而在 7420 之上,这两个值略有差异,三星将其默认设定为 46.7% 和 20.8%。起初,我对于这两个值还挺疑惑的,无法完全理解为何这么设定,直到我算了一下两个核心簇的每瓦性能曲线。

肯定会有人注意到我在图中放的箭头,箭头所在位置代表了某个线程迁移到大核心或小核心的理论值。细心的读者可能还会注意到,这些剪头并没有出现在小核心 50% 和 46% 的位置。这是因为 CPU 频率调速器对于频率的调节,比任务达到 up-threshold 触发线程迁移更快。比如说,5433 的 up-threshold 是 50%,指的其实就是 A53 核心满负荷运行在 800MHz 频率下,但这种状况可能永远都不会发生,因为 CPU 在那种情况下肯定会调节到更高频率。5433 的调速器调节到某个频率一般会维持 10% 的闲置资源,而 7420 的这一数值为 25%——也就是说后者采用更宽松的设定,这样一来即便负载不需要,频率也会调节得更高。最终结果就是小核心迁往大核心的真正拐点,在 5433 身上略低于 900MHz,而在 7420 身上则略高于 1100MHz。

Down-threshold 的逻辑更简单一点,因为频率调速器的下调机制,在速度上比 scheduler 的线程迁移机制更慢。也就是说图中的箭头是线程向小核心迁移时的最小值,更高频率下这种向下迁移可能会随时发生。

所以用这张图来描绘核心性能,我们就能更好地理解 big.LITTLE 究竟在做些什么了。这实际上也是 5433 和 7420 存在较大差异的一个地方:Galaxy Note 4 线程迁移相较 Galaxy S6 更激进,效率更低。设备相对优化的方案,应该是线程向上和向下迁移的拐点尽可能在效率方面靠拢(上图的纵轴),虽然在性能方面(上图的横轴)可能会略有小跳跃——负载介于两条性能曲线之间的时候可能表现出迟滞。

看起来,三星针对 Exynos 7420 的效率优化还是花了不少功夫的,软件部分修正了早前 5433 不少奇怪的配置问题。Exynos 7420 和 5430 一样,成为为数不多在小型移动设备中,在 ARM 大核心设计上占优势,并在没有太多妥协的前提下高效利用 big.LITTLE 架构的 SoC。虽然三星的软件堆栈仍然有提升空间,比如 scheduler 的完整性能感知(full energy awareness),但的确没有再像 Exynos 5433 那样出现错误配置的情况。

从最大能耗的角度来看,我认为 1.9GHz 对 A57 核心而言可能会是个更合理的选择:设备在某些场景下,比如说大量应用更新或者访问一些包含大量广告的站点,会令 CPU 满负荷运行,设备因此会微微发热——但这种场景毕竟是少数,大部分运算时间仍处在低频率下。未来 ARM A72 处理器核心的性能和能效表现如何显然很值得期待,就 2015 年来看,三星的 A57 SoC 由于存在工艺方面的优势,仍然是表现最好的。

GPU 性能与功耗

接下来就来到 Exynos 7429 的 GPU 部分了,我们再次看到了 ARM Mali T760。我们在先前的深度架构剖析,以及 Exynos 5433 评测文章中,已经谈到过 ARM 的 Midgard 架构和三星的具体实施方案。Exynos 7420 和 5433 在 GPU 部分的差异在于,前者多了两个 shader 核心,而且这次还用上了 LPDDR4 内存。两个新增的 shader 核心肯定是存在影响的,但我们对 LPDDR4 和增加的带宽造成的影响就不确定了,直到我们进行性能的深入分析。

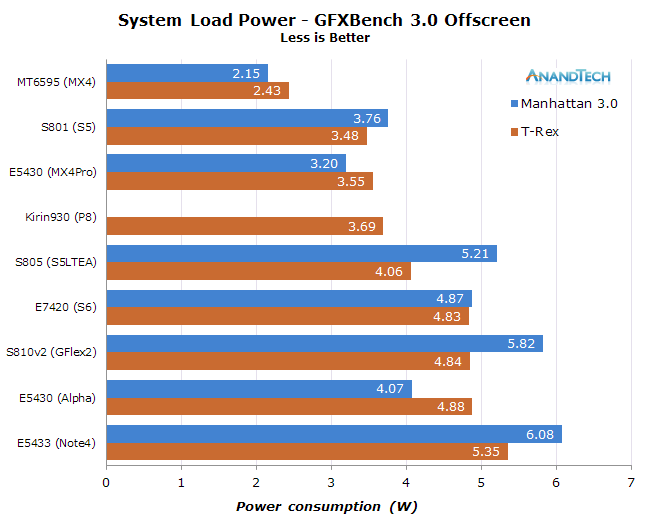

首先来看看 7420 的功耗峰值情况,和其它 SoC 比起来如何。我们采用 GFXBench 的 T-Rex 和 Manhattan 3.0 离屏测试。

Galaxy S6 及 Exynos 7420 负载功率最高达到 4.85W。这个负载功率去掉了闲置与屏幕功耗,能够更有效地表现 SoC 活跃功耗,而非整机功耗。

看起来,14nm 工艺的确有利于性能方面的提升,于此同时功耗还比 5433 的 T760MP6 更低,这里 T760MP6 的频率稍低。我们先前就了解过三星针对 ARM Midgard 架构的 DVFS 调节技术,这次看来 Exynos 7420 的 GPU 在处理重型 ALU 运算任务的时候,在功耗方面做得非常不错。值得一提的是,只要某个任务给 shader core 增加 ALU 负载,三星就选择提高 GPU 的频率。 上述跑分中,Exynos 7420 GPU 应对这一场景的最高频率达到 772MHz,而在增加纹理和加载/存储单元方面的任务压力时,最大频率达到 700MHz。而 Exynos 5433 这两个值分别限制在 700MHz 和 600MHz 之下,相较而言 7420 在这方面小有提升。而且两种状态下的电压也没有比 5433 更高, 从结果来看,高负荷算术运算(译者注:原文用词 high-arithmetic,我不确定这里的 high 是大量算术运算,还是高精度或什么高级算数运算,有时间的可以去研究下 Manhattan 3.0 测试)和一般负载的 GPU 功率差异达到了最小化。

这次我终于也有机会测试高通的 Adreno GPU(分别是 S5 中的骁龙 801、S5 LTE-A 采用的骁龙 805 和 G Flex2 采用的骁龙 810),某些数字是我没想到的。首先很显然在 T-Rex 测试中,Adreno 420 强于 Galaxy Note 4 之上的 Mali T760MP6,T-Rex 测试中其功耗和能效都远远领先。比较有趣的是,在诸如 Manhattan 测试一类重在 ALU 算术运算负载的任务中,Adreno 4xx 的功耗高得多。Midgard 架构让 GPU 有了算术运算负载方面的功耗优势,而 Adreno 4xx 就相反了,其功耗出现了剧烈增加。

为了更好地观察不同架构间的能效差异,我将性能和功率数字放在同一张表格中,如下:

虽说 Exynos 7420 达到了较高的 4.82W,但却达到了迄今最佳性能表现,在效能方面也位列这张表的最顶端。高通骁龙 805 在工艺方面实际上落后于 7420 两代,不过在 T-Rex 测试中,其能效表现也相当不错。而骁龙 810 的 Adreno 430 虽然采用更好(相比 805)的工艺,但能效却落后于骁龙 805。

而在接下来重在算术运算的 Manhattan 测试中,情况就略微复杂了:

Exynos 7420 仍然是效率最高的芯片,而且和高通 Adreno 4xx 拉开了比较可观的差距。未来我们还会对骁龙 810 进行更为细致的分析,但就目前 GFXBench 的结果看来,虽然骁龙 810 采用台积电更新的 20nm 工艺,但在 GFXBench 的两项测试中,能效都落后于骁龙 805。

(译者注:本文对“能效”一词对应的英文是 power efficiency;本文有时不对“功率”和“功耗”进行区分,这两个词通常都对应英文的 power。)

显然,由于 14nm 工艺的加成,三星在效率方面表现最佳,这样一来,也就很难对 GPU 架构效率做判断了。看来唯有高通发布骁龙 820(FinFET 工艺)之后,我们才能对架构进行一对一的比较了。

可能会有人注意到,我在对比中加入了联发科的 MT6595,虽然其绝对性能很弱,但其功耗表现却比较亮眼,这颗芯片达到最大性能时功耗不超过 2.4W,这足以表明不同半导体供应商之间的设计差别。

在功率超过 3-4W 时,基本上所有测试的 SoC 都无法将最高频率维持在可用时间内。Exynos 7420 情况也是这样,即便用上了更新的制造工艺,效率也不错,却依然无法维持超过 350-420MHz 的频率状态。Joshua 在先前的 Galaxy S6 评测中已经谈到了温度限制机制,这也就带来了一条形似正弦的性能曲线(译者注:意指性能很不稳定),因为其温度管理无法决策某个频率的维持时间。我对此稍作了研究,发现默认驱动的调节等级很不合理,不像我们预期得那么平缓。原生驱动有 4 个温度调节等级,频率分别定在 544、350、266 和 266MHz。有两个温度阈值设定在相同的频率上,实在是很奇怪,应该是没有任何实际价值的。我将调节等级改为 544、420、350、266MHz,令频率降低变得更平缓,另外我还增加了 IPA 热管理驱动的功率悉数值,令其更能代表真实使用场景。

最终,在运行期间性能表现稳定了很多,设备开始发热,25 分钟后,性能水平达到稳定状态。值得一提的是,这种调整还能令电池续航提升多达 33%,相较 S6 原生设定的 2.8 小时,现在持续到了 3.8 小时。这是因为更高的性能状态,相比更低频率状态的能效更差,频率的线性变化,可导致运行电压的二次方变化(译者注:这句话是指,频率提升一小步,则电压需要增加一大步;后者的增加不呈线性)。

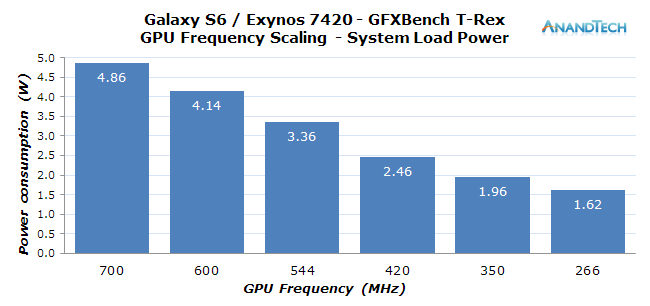

上图是 GPU 所有频率状态测得的负载功率(没有 772MHz 是因为 T-Rex 测试达不到这一频率)。不难发现,420MHz 状态就相当于 700MHz 功耗的一半,虽然实际上从频率上来看前者只比后者低了 40%。

移动行业似乎养成了这样一种坏习惯:无止尽地进行性能跑分竞赛,已经开始忽视性能和效率之间的关系。除了魅族 MX4 所用的联发科 MT6595 SoC(还有苹果最近的 A 系列 SoC),如今的旗舰 SoC 已经很少采用合理的 GPU 配置,基本都无法维持最高性能状态。这对用户体验是存在影响的,就像上面我们演示修正温度调节行为一样;都想要更高的性能,但由于温度方面的限制一味追求高频只会导致不稳定的性能和续航的妥协。

Galaxy S6 的 GPU 最高频率仅能维持不到 2 分钟,在 20 分钟之后掉一半性能。除非有用户玩游戏的习惯是每次都只玩 5-10 分钟,否则这样的设定是很不合理的。如果厂商能够将最高频率限制到设备的可持续性能水平,则表现会好很多,对 Galaxy S6 而言,这个频率应该在 420MHz 或 350MHz 状态。测试效率,的确比测纯粹的性能要复杂很多,如果说整个行业和媒体针对移动设备的评估方式还是这样,那么这个问题未来会成为大问题。

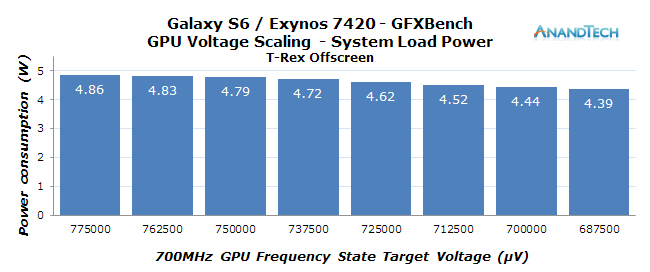

和 CPU 测试部分一样,我对于 GPU 功耗的 undervolting 操作也很好奇。所以我又搞了个介面,控制 GPU 电源管理驱动,实时更改电压,GFXBench T-Rex 测试得到以下值:

设备温度不高的话,GPU 就能维持在最高频率状态更长时间了(没有垂直同步的限制下)。鉴于 T-Rex 测试尚未达到拐点,而且是没有垂直同步的离屏测试,所以就没什么可担心的了。我以 12.5mV 步进逐步减少电压,直到设备崩溃无法完成测试。总的来说,这种尝试所能获得的性能红利,相比针对 A57 核心的 undervolting 操作,还是存在更多限制的。这很可能是因为我们看到的功率数字并非完全来自 GPU,部分来自 CPU、互联,以及内存控制器和 DRAM。

LPDDR4 性能与功耗

LPDDR4 理论上相较 LPDDR3 能够带来更好的功耗和性能表现。性能提升很清楚:因为这种新的内存技术能够为 SoC 提供双倍带宽,相较 825MHz LPDDR3 的 13.2GB/s,Exynos 的 1555MHz 内存将带宽提升到了 24.8GB/s。

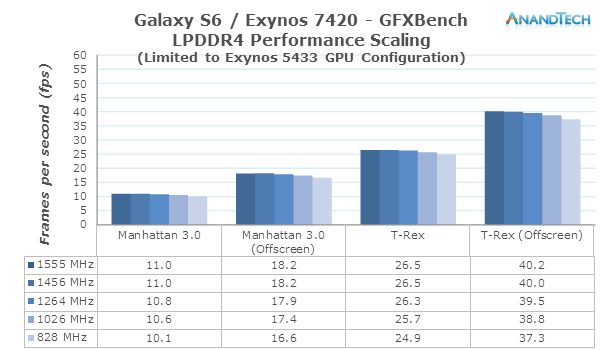

为了了解 LPDDR4 内存带来的性能提升,我做了个小实验:既然 Exynos 7420 和 5433 有着相同的主 IP 模块和 GPU 架构,那么通过对 7420 进行限制,应该可以模拟 5433。如果限制过后的性能和 5433 差不多,以此作为基准,就能单独判断 LPDDR4 的实际影响了。

为了在 Galaxy S6 上模拟出 Exynos 5433 的性能,我将 7420 的 GPU 核心限制到了 MP6,且频率也降低了。另外我还降低了 LPDDR4 内存控制器的速度,令其与 Exynos 5433 LPDDR3 频率相同。虽然两代内存技术运行在相同频率下,并不意味着他们就能有相同的性能表现;还会有诸如延迟、transaction size 等影响性能的其他因素。CPU 存储测试中,我没有发现两颗 SoC 之间有延迟方面的大差别,所以虽然并不能完全确定,但我们可以假定内存频率是影响两颗芯片的唯一要素。

在 828MHz 内存频率下,GFXBench 所有四个游戏测试性能得分,两款设备差别都控制在 0.5fps 范围内。看起来已经完美还原了 5433 的性能状态。然后再持续增加内存频率,看看 Mali T760 是如何利用这些资源的。每次频率增加,性能都会提升。这种提升似乎在 1264MHz 时发生衰减,在 1456MHz 及更高频率时,性能提升已经变得很少。看来三星在 Exynos 5433 内存带宽权衡方面做得很不错,因为在将内存速度加倍以后,性能提升也不到 10%。

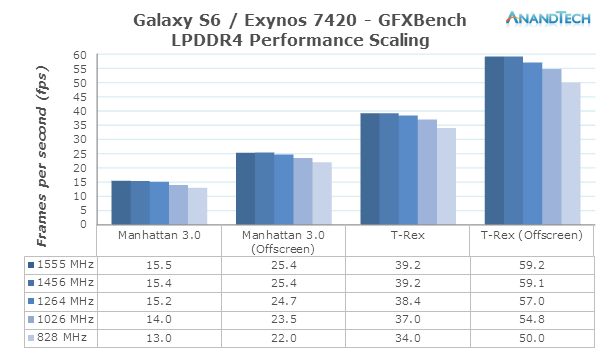

不过 Exynos 7420 多加了两个 shader 核心,频率也更高,对内存也会有更高的要求,也就能够更好地利用 LPDDR4 内存了。于是我们将 GPU 配置调整到 7420 的原生设定状态,然后调整内存频率,来看 LPDDR4 带来的红利。

相较 Exynos 5433,其性能数字实现全方位跳跃,可见 7420 对于新增核心的利用还是相当不错的。这一测试方法总体上更好地表现了 LPDDR4 带来的提升。T-Rex 测试成绩变化更大,限制在 LPDDR3 速度下时其帧率会掉 15-18%。Manhattan 测试情况和 T-Rex 类似,不过其 on-screen 模式下获得的提升更大,达到了 19%。

和 Exynos 5433 一样,7420 实际上也没有完全填满带宽,随频率增加性能提升也出现了逐步衰减——到 1555MHz 时基本上已经没有什么性能提升了。

LPDDR4 的一大优势就是带来更高的效率,三星说相较 LPDDR3 每字节能耗减少 40%(译者注:文中出现“能耗”一词时,特指 energy consumption)。在高性能场景下,速度达到将近 LPDDR3 的两倍,这种优势将不复存在了,不过日常使用场景仅需部分带宽,在功耗方面还是能够看到切实的提升的。

考虑到 GPU 工作量多少也取决于可用带宽,调整内存频率带来的功耗差异还是有限的。今年早前在 ARM 的 TechDay 之上,ARM 和我们分享了 Galaxy S5 之上 Exynos 5422 的一些功耗数字——这是一颗 28nm 的 SoC,支持 LPDDR3 内存。内存控制器与 DRAM 共同功耗大约在 1W 左右,控制器与 DRAM 平均功耗占比 40:60。我估计 Exynos 7420 及其 LPDDR4 内存风之性能下的情况差不多,虽然我们不太确定 LPDDR4 和 14nm 对于内存控制器的功耗影响如何。

总的来说,LPDDR4 在效率和性能方面都有可观的提升,但我觉得不能称其为革命性变化。高通和联发科今年为其大部分 SoC 仍然选配了 LPDDR3,这对于非旗舰设备而言仍是个比较经济的选择。所以和几年前 LPDDR2 向 LPDDR3 的转变一样,完全转向 LPDDR4 还是需要时间的。

总结

三星 Exynos 7420 对于 Samsung LSI 而言的确是很重要的一步,虽然这颗芯片基础部分相较上一代并没有本质差异,但实际物理实施和生产工艺方面,这颗 SoC 却做了不少提升。

就 CPU 部分,部分性能提升源自比前作略高的频率,另外还有更佳的缓存实施方案,尤其是大核心簇部分。而且在大核心簇部分,三星并没有追求过高的时钟频率,更多着力于能效。实际上,Exynos 5433 之上的 A57 核心就已经在性能方面比竞争对手骁龙 805 更出色了,Exynos 7420 也就没有必要把频率推得更高了。这对最大功率和能效的提升都有帮助。相同频率下节约 35%-45% 的功耗,以其 TDP 和效率,将其放进诸如 Galaxy S6 这么薄的智能手机中就能够达到要求。

不过我认为三星如果能够将最高频率设定在 1.9GHz,维持每个核心功耗低于 1W,其表现会更好。这么做能够在高负载时略微增加效率,降低 10% 的性能可以换来 26% 功耗表现的提升。

在 Exynos 5433 的评测中,我对其软件和电源管理表达了失望,因为 5433 的优化极少,且真实使用场景存在性能退化。但这一次,三星电子在配置 SoC 电源管理参数方面表现好了很多。配置错误少了,原本 5433 芯片中绝大部分低效行为也不见了。虽然仍有提升空间,比如升级能耗感知 scheduler,但其表现还是令人满意的。

而在 GPU 方面,情况就不大一样了。好的一面在于 Exynos 7420 的 Mali T760MP8 采用 14nm 制程,不仅是我们所见智能手机中最快的 SoC,也是我们测试过效率最高的 SoC。而坏的一面则在于,虽然效率很高,但性能和功耗再次超过手机可忍受的 TDP,在活跃状态下不可避免地因为发热,需要调整到更低频率状态。在过去几代产品中,这个问题变得越来越严重,都不过是为了跑分更好看而已。

对 CPU 而言,现实使用场景,性能要求存在频率超过持续 TDP 的情况(译者注:意即短时峰值性能需求),但 GPU 就不一样了。三星并不是唯一这么干的厂商,高通等一众厂商都采用这种超负荷的配置,这是很不合理的。采用合理平衡的 SoC 似乎越来越成为一种奢侈行为。可能会有人说高性能设计,对于平板或者更大的设备是有意义的,SoC 厂商不应该受到全部的指责——那么 OEM 厂商在合理配置方面、在更小的设备中通过软件限制功耗,就是有责任的。无论怎么说,这种做法对用户而言都是有百害而无一利的,只会导致不稳定的游戏体验,和糟糕的续航表现。

Galaxy S6 是首批采用 LPDDR4 内存的设备。虽然 LPDDR4 带来的性能提升并不具有革命性的意义,GFXBench 成绩提升平均在 18-20%,但其效率对于设备体验仍存在很大的影响。由于任务负载的复杂性,虽然我无法完全量化 LPDDR4 带来的好处,但理论性能提升对于日常使用的加成,一定是持续性的。

那么最大的问题就在于 Exynos 7420 究竟有多好了。结论实际上取决于同时段的竞品,主要就是高通骁龙 810 和 808 了。在这篇文章中,我已经展示了骁龙 810 的 GPU 成绩,很遗憾跑分数字还不如 805 好看——Exynos 7420 无论在性能还是功耗方面都是完胜的。实际上我这边已经有了 810 的测试成绩,不过还没有准备好发布——骁龙 810 的表现会作为一篇单独的深度文章发布。已经看过我们 HTC M9 评测文章的读者应该已经知道,骁龙 810 并不像它宣传得那么好,可以说其效率方面的弱势,相比 Exynos 7420 是相当大的。

这么一来,Exynos 7420 在这一时段是没有对手的。在全新的 14nm 设计和解决方案的加持下,三星实现了完胜。就近期来说,Exynos 7420 的确在 Android 设计中做到了独孤求败,的确为 2015 SoC 树立了新的榜样。

* 参考来源:The Samsung Exynos 7420 Deep Dive - Inside A Modern 14nm SoC,转载请注明出处 AnandTech,及译者:欧阳洋葱

讲真,楼上的好几个人不要无端黑麒麟 950,这颗 SoC 的 CPU 部分可以说表现算是非常牛逼的,其最高频率甚至都没到热平衡拐点,对大屏手机而言几乎可以持续满负荷运行——这样的 CPU 在市面上是不多见的。但麒麟 950 的绝对性能,还有 GPU 表现都比较弱逼。

-

别着急买电脑,英特尔刚发布了10年来最有诚意的新处理器

别着急买电脑,英特尔刚发布了10年来最有诚意的新处理器作者:Finch前段时间刚重金攒了一台 3.1GHz 四核第七代酷睿 i7 处理器、2TB SSD、16GB 内存…查看全文

-

如何看待2017年1月23日三星公布的Note7爆炸原因?

如何看待2017年1月23日三星公布的Note7爆炸原因?这篇文章很长,我用了两天时间才写完。可以保证绝不是又臭又长,内容超出您的预期。昨天早上…查看全文

-

手机厂商年表(2010年)

之前的《米乎演义》要从第一回开始补,但是时间过得比较久了,怕很多事情忘记了,所以列了一个表,把每一年重要事件先列出来。刚刚把2010年的列好了,看了一下还真有启发呢,就是不知道时间…查看全文

-

2016年12月份CPU性能天梯图

新增型号: A4-7300A6-9500EA6-9500A8-8650A8-9600A10-9700EA10-9700A12-9800EA12-9800Athlon X4 950PhenomII X4 850I7 7700K等、转自@秋刀鱼半藏 图片点击可放大百度云下载地址:http://…查看全文