一、CPU的结构

1.CPU的功能

(1)取指令

控制器必须具备能自动地从存储器中取出指令的功能

(2)分析指令

分析指令包括两部分内容:其一,分析此指令要完成什么操作,即控制器需发出什么操作命令;其二,分析参与这次操作的操作数地址,即操作数的有效地址。

(3)执行指令

执行指令就是根据分析指令产生的“操作命令”和“操作数地址”的要求,形成操作控制信号序列,通过对运算器、存储器以及I/O设备的操作,执行每条指令。

CPU必须具有控制程序的顺序执行(称指令控制)、产生完成每条指令的控制命令(称操作控制)、对各种操作加以时间上的控制(称时间控制)、对数据进行算术运算和逻辑运算(称数据加工)、处理中断等功能。

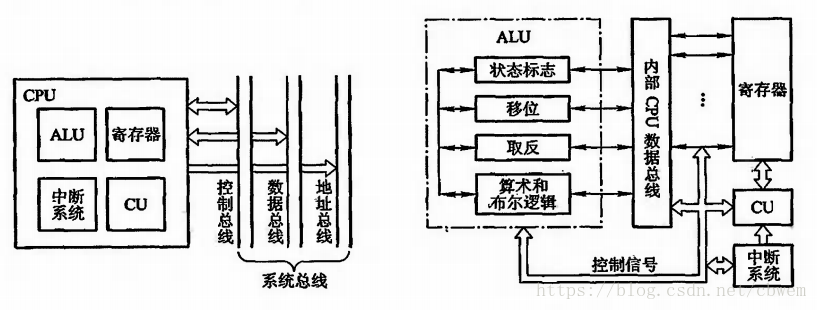

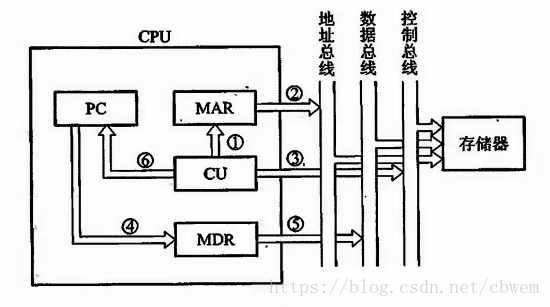

2.CPU结构框图

3.CPU的寄存器

CPU中的寄存器大致可分为两类:一类属于用户可见寄存器,用户可对这类寄存器编程,以及通过优化使CPU因使用这类寄存器而减少对主存的访问次数;另一类属于控制和状态寄存器,用户不可对这类寄存器编程,它们被控制部件使用,以控制CPU的操作,也可被带有特权的操作系统程序使用,从而控制程序的执行。

用户可见寄存器

(1)通用寄存器

通用寄存器可由程序设计者指定许多功能,可用于存放操作数,也可作为满足某种寻址方式所需的寄存器。寄存器间接寻址时还可用通用寄存器存放有效地址的地址。

(2)数据寄存器

数据寄存器用于存放操作数,其位数应满足多数数据类型的数值范围。

(3)地址寄存器

地址寄存器用于存放地址,其本身可以具有通用性,也可用于特殊的寻址方式。

(4)条件码寄存器

条件码是CPU根据运算结果由硬件设置的位。将条件码放到一个或多个寄存器中,就构成了条件码寄存器。

控制和状态寄存器

MAR:存储器地址寄存器,用于存放将被访问的存储单元的地址。

MDR:存储器数据寄存器,用于存放欲存入存储器中的数据或最近从存储器中读出的数据。

PC:程序计数器,存放现行指令的地址,通常具有计数功能。当遇到转移类指令时,PC的值可被修改。

IR:指令寄存器,存放当前欲执行的指令。

PSW:程序状态字寄存器,存放条件码和其他状态信息。

在具有中断系统的机器中还有中断标记寄存器。

4.控制单元和中断系统

控制单元(CU)是提供完成计算机全部指令操作的微操作命令序列部件。微操作命令序列的形成方法有两种:一种是组合逻辑设计方法,为硬连线逻辑;另一种是微程序设计方法,为存储逻辑。

二、指令周期

1.指令周期的基本概念

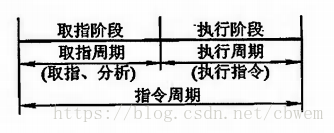

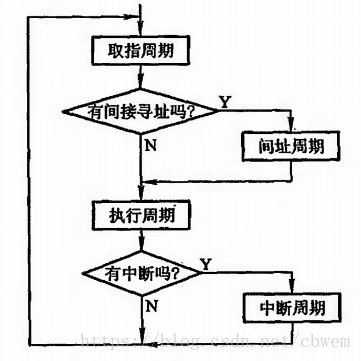

CPU每取出并执行一条指令所需的全部时间称为指令周期,也即CPU完成一条指令的时间。取指阶段完成取指令和分析指令的操作,又称取指周期;执行阶段完成执行指令的操作,又称执行周期。

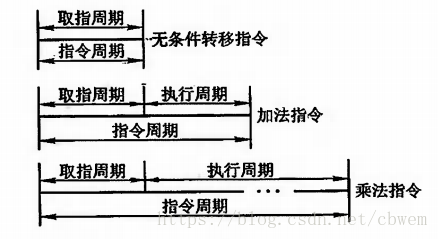

由于各种指令操作功能不同,因此各种指令的指令周期是不相同的。

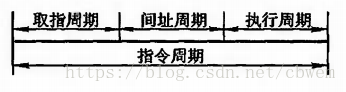

简介寻址的指令周期就包括取指周期、间址周期、**执行周期**3个阶段,其中间址周期用于取操作数的有效地址,因此间址周期介于取指周期和执行周期之间。

如果有请求,CPU则要进入中断响应阶段,又称中断周期。在此阶段,CPU必须将程序断点保存到存储器中。一个完整的指令周期应包括**取值、间址、执行、中断**4个子周期。

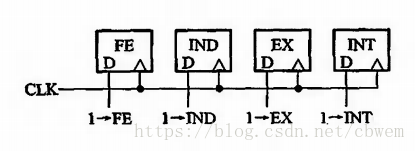

取指周期是为了取指令,间址周期是为了取有效地址,执行周期是为了取操作数,中断周期是为了保存程序断点。这4个周期又可称为CPU的工作周期,为了区别它们在CPU内可设置4个标志触发器。

FE、IND、EX、INT分别对应取值、间址、执行、中断4个周期,并以“1”状态表示有效,它们分别由 这4个信号控制。

2.指令周期的数据流

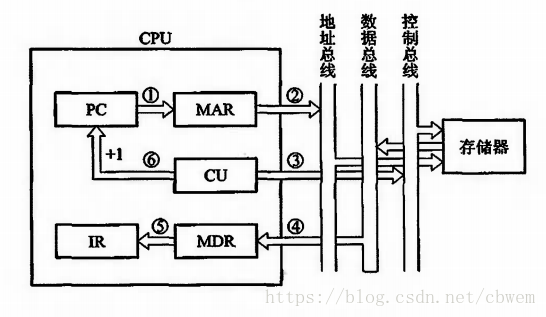

取指周期数据流

PC中存放现行指令的地址,该地址送到MAR并送至地址总线,然后由控制部件CU想存储器发读命令,使对应MAR所指单元的内容经数据总线送至MDR,再送至IR,并且CU控制PC内容加1,形成下一条指令的地址。

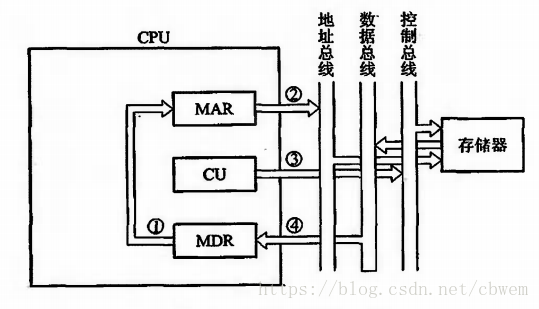

间址周期的数据流

一旦取指周期结束,CU便检查IR中的内容,以确定其是否由间址操作,如果需要间址操作,则MDR中指示形式地址的右N位(记作Ad(MDR))将被送到MAR,又送至地址总线, 此后CU向存储器发读命令,以获取有效地址并存至MDR。

执行周期的数据流

由于不同的指令在执行周期的操作不同,因此无法用统一数据流图表示。

中断周期的数据流

由CU把用于保存程序断点的存储器特殊地址(如栈指针的内容)送往MAR,并送到地址总线上,然后由CU向存储器发写命令,并将PC的内容送到MDR,最终使程序断点经数据总线存入存储器。CU还需将中断服务程序的入口地址送至PC,为下一个指令周期的取指周期做好准备。