CPU 的结构

CPU的功能

- 对于冯诺依曼结构的计算机而言,一旦程序进入存储器之后,就可以由计算机自动完成取指令和执行指令的任务。控制器负责协调和控制计算机各部件执行程序的指令序列。

- 取指令:要求控制器能自动形成指令的地址,发出取指令的命令,将对应此地址的指令取到控制器中。第一条指令的地址可以人为指定,也可以由系统设定。

- 分析指令:分析要完成什么操作,即控制器需要发出什么操作命令。分析参与这次操作的操作数地址,即操作数的有效地址。

- 执行指令:形成操作控制信号序列,通过对存储器,运算器和IO设备的操作,执行每条指令。

- 控制程序的输入和运算结果的输出及对总线的管理,处理处理机运行过程中出现的异常情况和特殊请求,即中断处理能力。

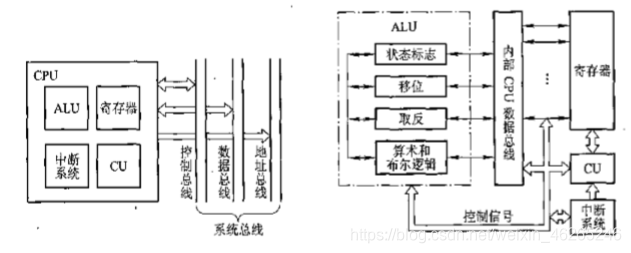

CPU结构框图

CPU的寄存器

-

用户可见的寄存器:CPU执行机器语言访问的寄存器。再调用子程序之前,必须将所有用户可见寄存器的内容保存起来,可以由CPU自动完成,也可以由程序员编程保存。

通用寄存器:可以用于存放操作数,也可作为满足某种寻址方式所需的寄存器。

数据寄存器:存放操作数。

地址寄存器:存放地址。

条件码寄存器:存放条件码,对用户来说是部分透明的。

-

控制和状态寄存器:对用户透明

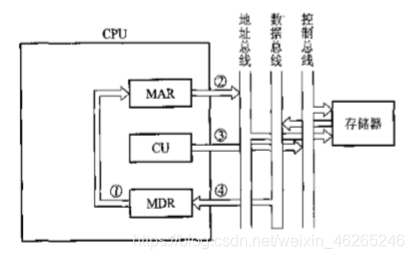

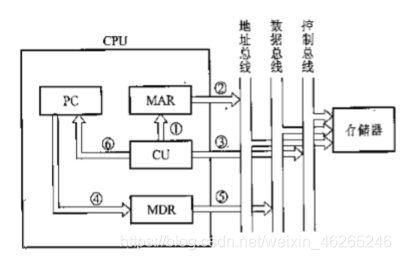

MAR:存储器地址寄存器。

MDR:存储器数据寄存器。

PC:程序计数器。

IR:指令寄存器。

控制单元

- 提供完成计算机全部指令操作的微操作命令序列部件

指令周期

- 指令周期:CPU每取出并执行一条指令所需的全部时间称为指令周期,也即CPU完成一条指令的时间,取指令阶段完成取指令和分析指令的阶段,又称为取指周期,执行阶段完成执行指令的操作,又称执行周期。由于各种操作功能不同,各种指令的指令周期是不同的。

- 取指令周期取指令访存,间址周期取有效地址访存,执行周期取操作数访存,中断周期保护程序断点。

指令周期的数据流

- 取指周期的数据流

PC中存放现行指令的地址,该地址送到MAR并送至地址总线,然后由控制部件CU向存储器发读命令,使对应MAR所指单元的内容经数据总线送至MDR,再送至IR,并且CU控制PC加1,形成下一条指令的地址。 - 间址周期的数据流

一旦取指周期结束,CU便检查IR中的内容,已确定其是否有间址操作,若需要间址操作,则MDR中指示形式地址的右N位将被送到MAR,又送至地址总线,此后CU向存储器发读命令,以获取有效地址并存至MDR。 - 执行周期的数据流

由于不同的指令在执行周期的操作不同,因此执行周期的数据流是多种多样的,可能涉及CUP内部寄存器间的数据传送,对存储器或IO进行读写操作或对ALU的操作,无法用统一的数据流表示。 - 中断周期的数据流

当前PC的内容必须被保存起来,以待执行完中断服务程序后可以准确返回到该程序的间断处。由CU把用于保存程序断点的存储器特殊地质送往MAR,并送到地址总线上,然后由CU向存储器发写命令,并将PC的内容送到MDR,最终使程序断点经数据总线存入存储器,此外CU还需要将程序的入口地址送至PC,为下一个指令周期的取指周期做好准备。