转自 https://blog.csdn.net/i_water/article/details/45621295

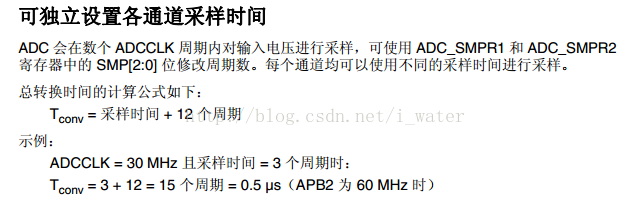

对单个ADC而言,AD采样的采样时间满足此关系:

我用的ADCCLK=42MHz,针对单ADC而言,最大采样率为42M / (12 + 3) =2.8M // 取ADC_SampleTime_3Cycles

要采 100KHz的信号32点,则采样率需达到3.2MHz(根据以上计算,好像有那么一小丢丢够不着。。。),没关系,多重ADC可以解决这个问题。

要采 1MHz的信号32点,则采样率需达到32MHz,使用STM32根本达不到(你不用花时间啦)。。。但是,可以尽量提高采样率,我们可以试一试,有时候就算明知不可为,我们还是值得让它走到它命运的巅峰(^--^)。

以下是官方例子的说明,我们可以稍加揣测:

In this example, the system clock is 144MHz, APB2 = 72MHz and ADC clock = APB2 /2.

Since ADCCLK= 36MHz and Conversion rate = 5 cycles

==> Conversion Time = 36M/5cyc = 7.2Msps

那么按照我自己的情况,就可以达到8.4Msps,看起来味道还不错,起码采100KHz的信号32点绰绰有余,但是做人不能太贪心了。。。

那么,问题来了,这货为神马不按套路出牌,难道不是 36M/(12+5)=2.1Msps ? 12跑哪儿去了?它脑袋进水了么?

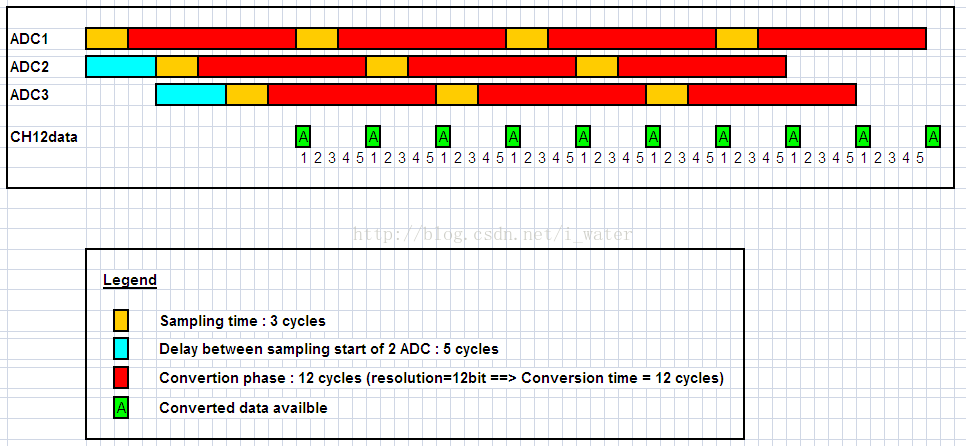

其实不然。我前面已经提到,那个神一样的公式是针对 单 ADC而言的,至于多重ADC得这么看:

我暂且相信你已经看懂了,不解释。。。

……

下面要说的是,这玩意儿怎么根据被测信号频率修改采样率(相信你已经猜到我要做FFT)?有点纠结:

为什么说有点纠结呢?

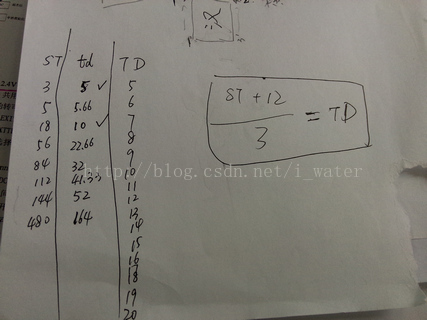

这里说明一下:参看库函数文件,我的ST即SampleTime,TD即TwoSamplingDelay,td 是根据 ST 计算得到理论上 TD 需要设置的周期数,ST 和 TD需满足

公式(ST + 12)/ 3 = TD,这个公式的得出就要看懂上面那张橙红蓝绿的图表啦。。。这个不会也需要我解释吧。。。

为什么要让它俩满足这个公式哩?

原因很简单——没有规矩不成方圆。要让AD均匀采样,就得按这个规矩办事,发现没?上面那张彩图说明了每隔5个ADC周期得到一次采样值,均匀的。不满足

公式当然采样也就不均匀了。经过计算得出理论上需要设置的TD值居然、仅仅、只有、区区两个值 5 和10 满足公式,也就是说只有这两组值可以达到均匀采样。至于ST为什么要酱紫设计我暂时也不得而知,干嘛不设计成可以匹配的选项。。。但是可以肯定的是,存在即合理。

综上可知,想要有规律的设置采样率应该是行不通的。聪明的你,有什么好药方麻烦告诉我吧?我要吃药。。。