无源晶振再使用时可以见到如下几种形式,具体如下:

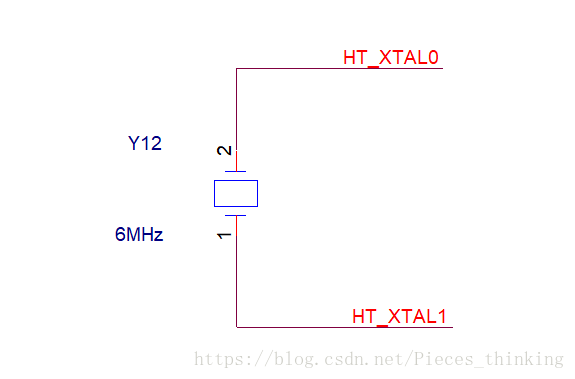

1.

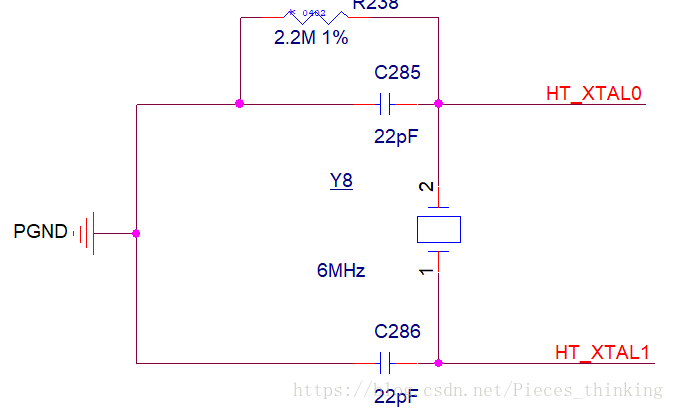

2.

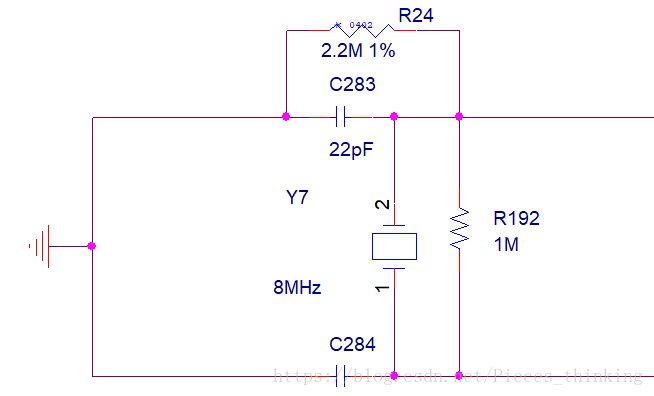

3.

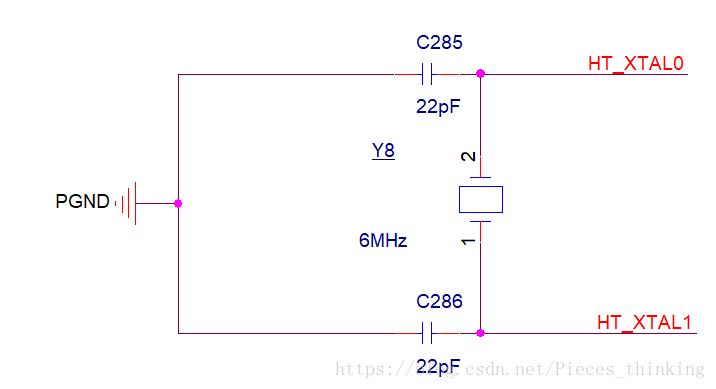

各种形式基本都有,最常见的就是下图中的格式:

4.

首先按照1.电容的有无?2.并联电阻和串联电阻的作用?两部分进行说明

一、电容的作用

1、晶体旁边不加电容是可以的。

2、晶体旁边加的这个电容被我们称之为晶体负载电容。晶体的谐振频率为Fr,加了电容的谐振频率为有载谐振频率FL。晶体谐振频率Fr与晶体有载谐振频率FL的关系为:

FL=Fr + Ts*CL

式中Ts为晶体的牵引量,单位为ppm/pF。CL为晶体的负载电容,即晶体旁边加的那个电容,单位为pF。

3、如果电路不加负载电容,则电路会工作在晶体谐振频率上。所以电路中是可以不加负载电容的。

4、晶体发生谐振后,会呈现为纯电阻,即谐振阻抗。在有载谐振中,谐振电阻一般会与负载电容呈反比例关系。也就是说负载电容越小,电路的谐振阻抗越高,就越不容易起振,输出波形幅度就越小。

5、而事实上,电路直接工作在晶体谐振频率的状态是非常理想化的。我们一般的电路都或多或少的有一些杂散电容。当电路振荡时,这些杂散电容便被视为晶体的负载电容进行工作。由于这些杂散电容一般都很小,且不稳定,这就造成晶体振荡频率不稳定,且谐振阻抗增高,“可能工作不稳定,频率不准确”。当然,如果你的振荡电路较为简单,而且PCB走线设计的又十分合理,PCB上的杂散电容小到可以忽略不计且十分稳定,那么就可以不加电容。

6、那么在设计电路时该如何加这个负载电容呢?首先你要明白FL这个有载谐振频率就是你的电路所要的频率。电路中的杂散电容为Cy的话,根据上面的公式,你所设计的电路频率应为:

FL = Fr + Ts*(Cy+CL)

设计时,你的负载电容CL可以用可调电容替代,调整CL值直到电路工作在你所要的频率上。一般时候这个负载电容CL值不要太小,上面说过电容太小,谐振阻抗会变高,不利于起振且输出幅度小。所以这个电容值一般选取在10至30pF之间。此时由于负载电容CL值远远大于杂散电容Cy值,因此对杂散电容的不稳定性可以忽略不计。所以加了负载电容的电路会更稳定,频率更准确。

一、并联或者串联电阻的作用

一份电路在其输出端串接了一个22K的电阻,在其输出端和输入端之间接了一个10M的电阻,这是由于连接晶振的芯片端内部是一个线性运算放大器,将输入进行反向180度输出,晶振处的负载电容电阻组成的网络提供另外180度的相移,整个环路的相移360度,满足振荡的相位条件,同时还要求闭环增益大于等于1,晶体才正常工作。

晶振输入输出连接的电阻作用是产生负反馈,保证放大器工作在高增益的线性区,一般在M欧级,输出端的电阻与负载电容组成网络,提供180度相移,同时起到限流的作用,防止反向器输出对晶振过驱动,损坏晶振。

和晶振串联的电阻常用来预防晶振被过分驱动。晶振过分驱动的后果是将逐渐损耗减少晶振的接触电镀,这将引起频率的上升,并导致晶振的早期失效,又可以讲drive level调整用。用来调整drive level和发振余裕度。

Xin和Xout的内部一般是一个施密特反相器,反相器是不能驱动晶体震荡的.因此,在反相器的两端并联一个电阻,由电阻完成将输出的信号反向 180度反馈到输入端形成负反馈,构成负反馈放大电路.晶体并在电阻上,电阻与晶体的等效阻抗是并联关系,自己想一下是电阻大还是电阻小对晶体的阻抗影响小大?

电阻的作用是将电路内部的反向器加一个反馈回路,形成放大器,当晶体并在其中会使反馈回路的交流等效按照晶体频率谐振,由于晶体的Q值非常高,因此电阻在很大的范围变化都不会影响输出频率。过去,曾经试验此电路的稳定性时,试过从100K~20M都可以正常启振,但会影响脉宽比的。

晶体的Q值非常高, Q值是什么意思呢? 晶体的串联等效阻抗是 Ze = Re + jXe, Re<< |jXe|, 晶体一般等效于一个Q很高很高的电感,相当于电感的导线电阻很小很小。Q一般达到10^-4量级。

避免信号太强打坏晶体的。电阻一般比较大,一般是几百K。

串进去的电阻是用来限制振荡幅度的,并进去的两颗电容根据LZ的晶振为几十MHZ一般是在20~30P左右,主要用与微调频率和波形,并影响幅度,并进去的电阻就要看 IC spec了,有的是用来反馈的,有的是为过EMI的对策

可是转化为 并联等效阻抗后,Re越小,Rp就越大,这是有现成的公式的。晶体的等效Rp很大很大。外面并的电阻是并到这个Rp上的,于是,降低了Rp值 —–> 增大了Re —–> 降低了Q

精确的分析还可以知道,对频率也会有很小很小的影响。

总结

并联电阻的作用:

1.降低晶体的Q值,Q值降低后晶体起振比较容易

2.抑制EMI,EMI不过时,可减小阻值

3.提供直流工作点

4.使门电路工作于线性区

串联电阻的作用:

1.降低晶体的激励功率,防止损坏。

2.限制振荡幅度。

实例:

已成型的一款产品因更换陶瓷晶振厂家后,陶振不容易起振,经过测试,将晶振并联一个1M电阻,晶振能够正常起振。

原因:这个电阻是为了使本来为逻辑反相器的器件工作在线性区, 以获得增益, 在饱和区是没有增益的, 而没有增益是无法振荡的. 如果用芯片中的反相器来作振荡, 必须外接这个电阻, 对于CMOS而言可以是1M以上, 对于TTL则比较复杂, 视不同类型(S,LS…)而定. 如果是芯片指定的晶振引脚, 如在某些微处理器中, 常常可以不加, 因为芯片内部已经制作了, 要仔细阅读DATA SHEET的有关说明.

附:电阻的作用是将电路内部的反向器加一个反馈回路,形成放大器,当晶体并在其中会使反馈回路的交流等效按照晶体频率谐振,由于晶体的Q值非常高,因此电阻在很大的范围变化都不会影响输出频率。过去,曾经试验此电路的稳定性时,试过从100K~20M都可以正常启振,但会影响脉宽比的。