操作系统学习<概述>

1.基本框架

计算机的存储结构主要有ROM(只读内存)、DRAM(动态随机访问内存)、硬盘等。

计算机CPU的外围有很多引脚和外围设备相连,并通过这些引脚来访问外围设备。

计算机上电后,首先进行CPU、内存条、显卡的初始化,由于后期cpu访问外围设备比较麻烦,所以一种有效可行的解决方案是将部分外围设备的缓存直接映射到内存的特定地址段,然后CPU通过和内存引脚直接访问特定的内存地址(譬如显卡将缓存直接映射到内存某个地址段空间,然后在bios中直接写数据到该内存地址空间中,由显卡直接显示数据)

ROM中存放BIOS(基本输入输出设备)初始化代码,在ROM代码执行过程中,从硬盘主引导扇区(0面0道1扇)读取512字节的主引道程序并并加载到内存指定位置(x8086的架构中指定内存地址为0x7c00),该512字节最后两个字节必须为0xaa55(表示可用的引导程序)。

该512字节内的代码主要功能是计算出内核执行文件在硬盘位置并把内核加载到内存中,然后cpu执行指令跳转到内核所在内存地址(start地址),即将cpu使用权交给内核。

2.cpu概述

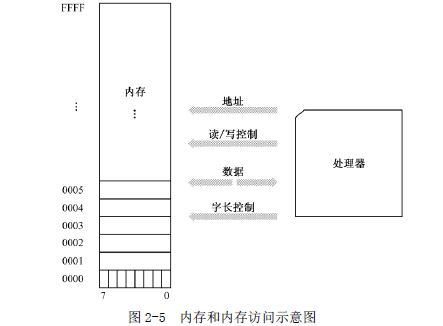

cpu通过总线和外围设备进行交互,以和内存交互为例。

cpu通过地址总线、数据总线、控制总线和内存进行互动。基本流图如下:

3.分段机制

cpu从内存指定地址读取指令并执行,这些指令在内存中都是以二进制形式存在。我们知道编译后的程序有可执行的代码、数据。可执行的代码和数据在内存中都是以二进制形式存在,cpu如何区分是可执行代码还是数据呢。

cpu的之所以能识别可执行指令是因为事先有约定,约定那些二进制是可执行代码指令。从这个角度来理解,试想,如果内存中是一个代码和数据交错混杂的在一起,cpu很容易读取到无法识别的指令(譬如直接读到数据),这里对cpu来说可能是一种灾难,另外即使cpu有保护机制,主要的访问也大大降低了效率,试想在一大坨内存中赛选可执行指令是个多么奢侈的工作。

对此,提出一种解决方案,分段机制。即可执行代码放在内存的固定一个地址范围中称为代码段,数据放入另一个内存地址范围中称为数据段,当然还有其他类型的段信息。

框架如下图:

4.分段机制的优化

试想有两个模块程序A和B,假设只有两个程序,先加载A后加载B到内存,A物理起始地址为0x00ff,B物理起始地址为0x007c。cpu访问B模块只要访问0x007c+段内偏移地址即可。假若加载顺序发生变化,AB模块的起始地址一般情况下会发生变化,

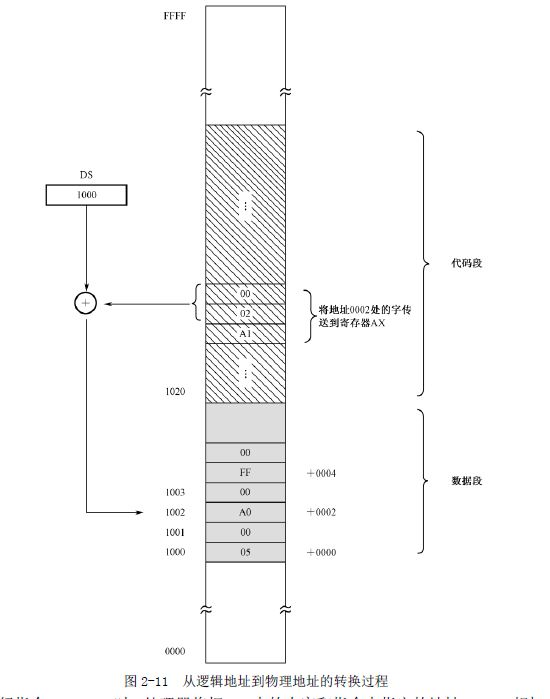

这时如果按照原有的物理地址访问方法进行重新调整各模块的访问物理地址及其麻烦(段内每条指令或数据地址都要重新更新)。为了解决这个问题,cpu引入一种解决方案,使用地址偏移(逻辑地址)+物理地址的方法来访问。即模块A中的每条语句的地址为相对0地址的偏移量,再模块被加载时使用内部寄存器CS/DS/ES等记录对应该段的物理地址,每个段内的指令或数据为CS/DS/EX+段内偏移即可访问。

该方法只需要重新赋值CS/DS/ES等段寄存器即可(段寄存器中存放物理地址)。整个过程即为从逻辑地址到物理地址的转换过程。

分段机制框架图如下: