Platform: RK3399

OS: Android 7.1

Kernel: v4.4.83

由于此屏在rk3288平台上使用过,原以为接上去就可以点亮,谁知道花了一天多时间折腾,最后还是发现是自己的大意造成的,ORZ…

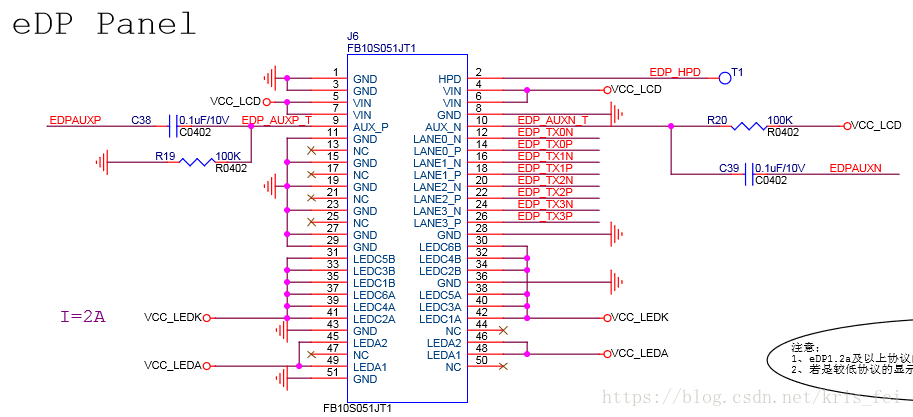

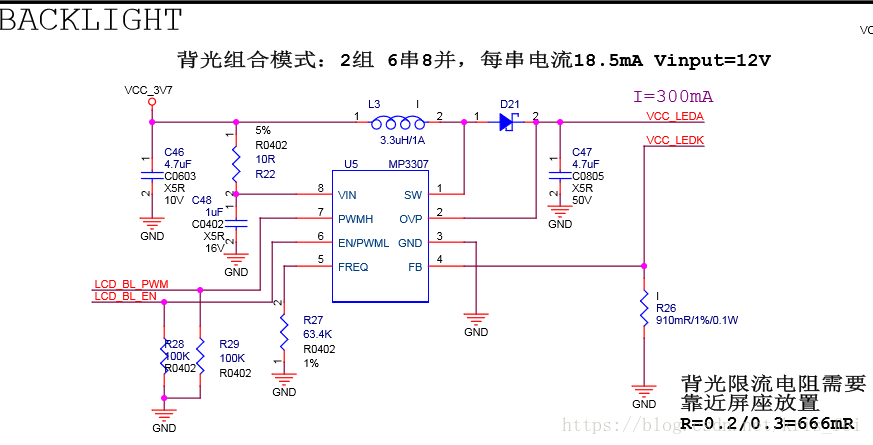

原理图:

LCD:

背光:

EDP屏硬件直接按照上电时序连接好控制,软件无需干预。

EDP_HPD pin可接可不接。

所以要做的就是配置LCD_BL_EN pin, 对应的是GPIO4_D5.

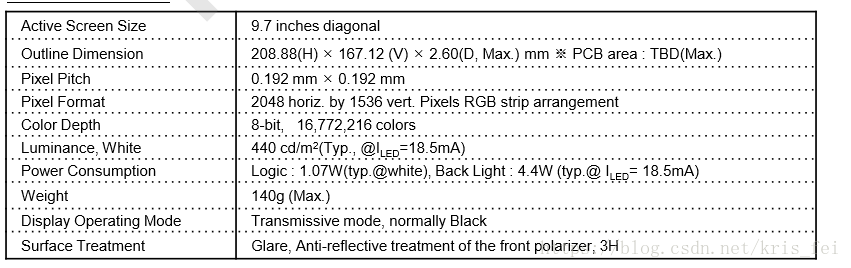

屏幕参数:

物理参数:

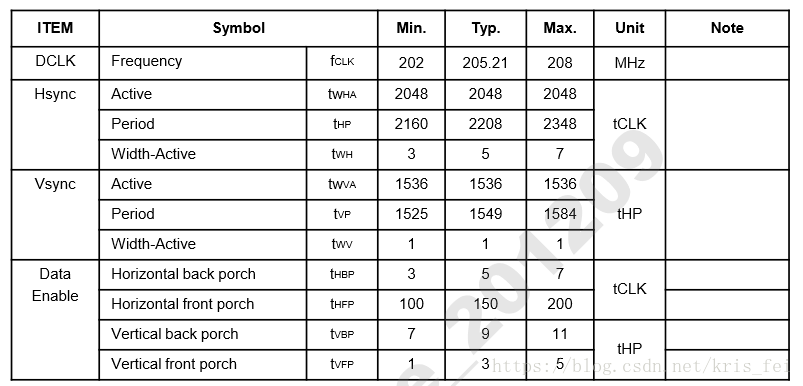

时序参数:

附时序参数说明:

| Property | Comment |

|---|---|

| clock-frequency | Dclk频率,单位Hz |

| hactive | 行有效像素 |

| vactive | 列有效像素 |

| hfront-porch | 行前消隐 |

| hsync-len | 行同步信号 |

| hback-porch | 行后消隐 |

| vfront-porch | 列前消隐 |

| vsync-len | 列同步信号 |

| vback-porch | 列后消隐 |

| hsync-active | Hsync信号极性配置 |

| vsync-active | Vsync 信号极性配置 |

| de-active | Den 信号极性配置 |

| pixelclk-active | Dclk信号极性配置 |

DTS配置:

在rk3399-mid-818-android.dts基础上修改

edp_panel: edp-panel {

//注意不要和lg_lp079qx1_sp0v弄混淆了。

compatible = "lg,lp097qx1-spa1", "panel-simple";

bus-format = <MEDIA_BUS_FMT_RGB666_1X18>;

backlight = <&backlight>;

power-supply = <&vcc3v3_s0>;

enable-gpios = <&gpio3 8 GPIO_ACTIVE_HIGH>;

ports {

panel_in_edp: endpoint {

remote-endpoint = <&edp_out_panel>;

};

};

};

backlight: backlight {

compatible = "pwm-backlight";

pwms = <&pwm0 0 25000 0>;

brightness-levels = <

255 200 199 198 197 197 196 195 194 193 193 192

191 190 189 189 188 187 186 185 185 184 183 182

181 181 180 179 178 177 177 176 175 174 173 173

172 171 170 169 169 168 167 166 165 165 164 163

162 161 161 160 159 158 157 157 156 155 154 153

153 152 151 150 149 149 148 147 146 145 145 144

143 142 141 141 140 139 138 137 137 136 135 134

133 133 132 131 130 129 129 128 127 126 125 125

124 123 122 121 121 120 119 118 117 117 116 115

114 113 113 112 111 110 109 109 108 107 106 105

105 104 103 102 101 101 100 99 98 97 97 96

95 94 93 93 92 91 90 89 89 88 87 86

85 85 84 83 82 81 81 80 79 78 77 77

76 75 74 73 73 72 71 70 69 69 68 67

66 65 65 64 63 62 61 61 60 59 58 57

57 56 55 54 53 53 52 51 50 49 49 48

47 46 45 45 44 43 42 41 41 40 39 38

37 37 36 35 34 33 33 32 31 30 29 29

28 27 26 25 25 24 23 22 21 21 20 19

18 17 17 16 15 14 13 13 12 11 10 9

9 8 7 6 5 5 4 3 2 1 1 0

0 0 0 0>;

default-brightness-level = <200>;

//Kris, 用的是GPIO4_D5

enable-gpios = <&gpio4 29 GPIO_ACTIVE_HIGH>;

};

建议先单独测试GPIO以及背光,然后再接屏幕,避免硬件电路设计有问题导致器件损坏。

调试遇到的问题:

问题一:

刚起来提示*ERROR* failed to find panel

此log是正常现象,刚开始由于DRM驱动先加载,这时候各个Components没准备好,导致master还是bring up。等后面Component(这里主要是等edp_panel加载完成)添加好后就还会bring up的。具体过程可参考:[RK3399][Android7.1] DRM中的Component System

问题二:

无法找到任何模式,提示:

rockchip-drm display-subsystem: connector[eDP-1] can't found any modes

查看/d/dri/0/summary下的vop状态也是不工作的,说明确实有问题。

rk3399_mid:/ # cat /d/dri/0/summary

VOP [ff900000.vop]: DISABLED

VOP [ff8f0000.vop]: DISABLED跟踪了下流程:

rockchip_drm_fbdev_init ->

drm_fb_helper_initial_config ->

drm_fb_helper_probe_connector_modes ->

connector->funcs->fill_modes ->

drm_helper_probe_single_connector_modes ->

drm_helper_probe_single_connector_modes_merge_bits ->

connector->funcs->detect ->

analogix_dp_detect->

analogix_dp_detect_hpd ->

analogix_dp_get_plug_in_status因此HPD的状态决定了mode的返回是否正确。

int analogix_dp_get_plug_in_status(struct analogix_dp_device *dp)

{

u32 reg;

//如果EDP的hdp pin有接到GPIO,那么检测电平状态

//上面原理图看到我们并未接。

if (gpio_is_valid(dp->hpd_gpio)) {

if (gpio_get_value(dp->hpd_gpio))

return 0;

} else {

//直接读取ANALOGIX_DP_SYS_CTL_3寄存器中的HDP状态的值

reg = readl(dp->reg_base + ANALOGIX_DP_SYS_CTL_3);

if (reg & HPD_STATUS)

return 0;

}

return -EINVAL;

}加Log看发现并没有读到寄存器中的HPD状态。

然后我在dts中直接设置force hpd了(代码调用可看analogix_dp_detect_hpd())

&edp {

force-hpd;

};这时候vopb工作了,但是还无显示。

kris@eco:~/rk3399/rockdev/rk3399_mid-eng$ adb shell

rk3399_mid:/ # cat /d/dri/0/summary

VOP [ff900000.vop]: ACTIVE

Connector: eDP

bus_format[1009] output_mode[f]

Display mode: 1536x2048p60

clk[200000] real_clk[200000] type[0] flag[a]

H: 1536 1548 1564 1612

V: 2048 2056 2060 2068

win0-0: DISABLED

win1-0: DISABLED

win2-0: ACTIVE

format: XB24 little-endian (0x34324258)

zpos: 0

src: pos[0x0] rect[1536x2048]

dst: pos[0x0] rect[1536x2048]

buf[0]: addr: 0x0000000003106000 pitch: 6144 offset: 0

win2-0: DISABLED

win2-1: DISABLED

win2-2: DISABLED

win3-0: DISABLED

win3-0: DISABLED

win3-1: DISABLED

win3-2: DISABLED问题三:

此问题最奇葩,因为自己偷懒,没有检查和看清EDP的驱动中居然有两个很类似的驱动名字

“lg_lp079qx1_sp0v”和“lg_lp097qx1_spa1”!

屏对应的是后者,但DTS配置的是前者,真给自己跪了…