介绍

正如业界众所周知的那样,28纳米及以下节点的设计复杂性正在爆炸式增长。小尺寸要求和高性能,低功耗和小面积的相互矛盾的要求导致了如此复杂的设计架构。多核,多线程和功耗,性能和面积(PPA)需求加剧了设计复杂性和功能验证。

负担在于功能和时间域验证,以确保设计符合规范。 RTL(和虚拟平台级别)功能验证不仅重要,而且硅验证也很重要。工程团队需要几个月才能验证实验室中的硅片的日子已经结束。在硅前验证过程中你能做些什么来保证硅后验证是第一次成功。

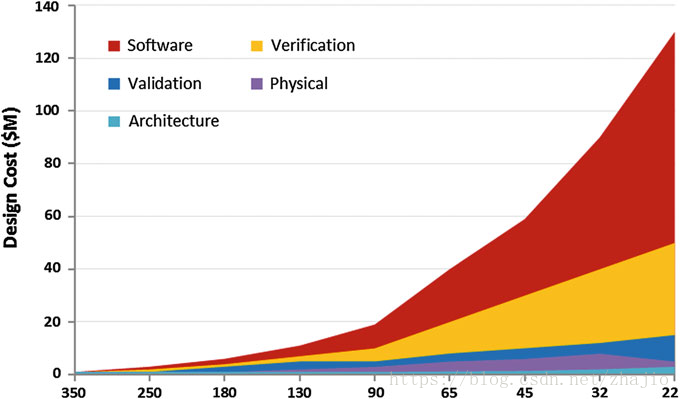

图1.1验证成本随着技术节点的缩小而增加

这些公司面临的最大挑战是缩短产品上市时间,以提供首批通过工作量增加的复杂硅片。功能设计验证是设计输出的长期调查。以下是两个关键问题陈述。

1.设计验证生产力:: 40-50%的项目资源用于功能设计验证。图1.1中的图表显示了设计周期不同部分的设计成本。显而易见,设计验证成本组件约占总设计成本的40%以上。换句话说,这个问题表明我们必须提高功能设计验证的生产力,缩短设计,模拟,调试和覆盖循环。这是一个生产力问题,需要解决(图1.2)。

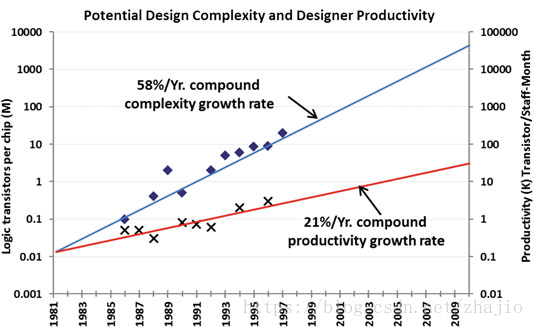

继续关注生产力问题,下图显示复合增长率每年为58%,而复合增长率仅为21%。需要完成什么和完成什么之间存在巨大差距。这也是为什么必须改进设计周期组件的生产力(如功能设计验证)的另一个例子。

图1.2设计生产力和设计复杂性

2.设计覆盖率::第二个问题陈述指出,由于功能性错误,超过50%的设计需要重新旋转。导致这种情况的因素之一是,我们没有客观地确定我们是否真的用我们的测试台覆盖了整个设计空间。 “如果没有经过验证,它不会起作用”的座右铭似乎在设计周期中占据了主导地位。不知道你是否确实覆盖了整个设计领域是逃脱漏洞和功能硅故障的真正罪魁祸首。

那么,每个问题的解决方案是什么?

1. 提高设计验证生产力

1.1. 缩短开发时间

- 提高抽象级别的测试。使用基于TLM(交易级别模型)的方法,如UVM,SystemVerilog / C ++ / DPI等。抽象级别越高,建模和维护验证逻辑就越容易。事务级逻辑的修改和调试更容易,进一步缩短开发测试平台,参考模型(记分板),外设模型和其他验证逻辑的时间。

- 使用受限随机验证(CRV)方法以较少的测试达到详尽的覆盖范围。更少的测试意味着更少的开发和调试时间。

- 开发可重复使用的验证组件(例如,UVM代理)。使它们参数化以适应未来的项目。

- 使用SystemVerilog断言来减少开发复杂时域和组合检查的时间。正如我们将看到的,断言非常直观,而且更容易建模,特别是对于复杂的时域检查。给定断言的Verilog代码将更加冗长,很难建模并且很难调试。 SVA确实减少了开发和调试的时间。

- 同样,更高级别的抽象模拟速度比在信号级别建模的纯RTL测试平台快得多。使用交易级别的测试平台。

- 使用SystemVerilog断言来直接指向错误的根本原因。这减少了模拟,调试和验证循环时间。调试设计过程非常耗时,但不知道错误的位置,试错模拟进一步加剧了已经很长的仿真时间。

- 使用SystemVerilog基于断言的验证(ABV)方法快速找到该错误的来源。正如我们将看到的,断言被放置在设计的各个地方,以便在错误发生的地方发现错误。传统的调试方式是在IO级别。您会看到主输出中的错误的影响。然后从主要输出追溯到找到造成冗长调试时间的错误的原因。相比之下,SVA断言直接指向故障源(例如,FIFO断言将直接指向失败的FIFO条件,并立即帮助调试故障),从而大大减少调试工作量。

- 使用事务级别的方法来减少调试工作(并且不会陷入信号级粒度)

2. 减少时间来覆盖并建立对完全验证设计的信心

- 使用SystemVerilog Assertions的'cover'功能来覆盖设计的复杂时域规范。正如我们在本书中将会看到的那样,'cover'有助于确保您已经在测试平台中使用了低层次的时域条件。如果断言不能解决,那并不一定意味着没有错误。其中一个原因是,你可能从来没有真正刺激过要求的条件(先行词)。如果你没有激发一个条件,你怎么知道模拟下的设计逻辑中是否确实存在一个错误? '封面'可以帮助您确定您是否确实已经行使了所需的时域条件。更多内容在后面的章节中。

- 使用SystemVerilog功能覆盖率语言来衡量设计的“意图”。您的测试台如何验证设计的“意图”。例如,您是否验证了公交车上的写/读/窥探的所有转换?您是否已经证实在同一行发生CPU1-snoop,同时出现CPU2写入无效的同一行?代码覆盖无助于此。本书将详细介绍功能覆盖。

- 使用代码覆盖来覆盖结构覆盖(是的,代码覆盖仍然是第一道防线,尽管它只是提供结构覆盖)。正如我们将在SV功能覆盖部分中详细看到的那样,结构覆盖不会验证设计的意图,它只会看到您编写的代码已经被执行(例如,如果您已经验证了所有“案例” 'case'语句,或切换所有可能的分配,表达式,状态等)。尽管如此,作为衡量设计覆盖范围的起点,代码覆盖仍然非常重要。

正如您从上述分析中注意到的,SystemVerilog断言和功能覆盖在功能验证的每个方面都起着关键作用。请注意,在本书中,我使用功能验证来包含'功能'功能覆盖以及'时间'功能覆盖。

本书如何帮助你?

本书将系统地介绍SystemVerilog断言(SVA)和功能覆盖(FC)语言功能以及每个步骤中实际应用的方法学组件。这些应用程序是建模的,你应该能够在最小的修改中使用它们。本书是使用功能点样式幻灯片和描述来组织的,使得它很容易掌握关键基础知识。为那些熟悉基础知识的用户提供高级应用程序。本书的大部分内容都集中在对语言功能的深入讨论上,并展示了使功能易于理解和适用的示例。仿真日志通常用于更容易理解功能或方法的基本概念。

本书由设计工程师为(主要)硬件设计工程师编写,目的是使语言易于掌握,避免长时间冗长的详细说明。作者在系统和芯片设计领域已有20多年的历史,并且知道在尽可能短的时间内学习新语言和方法的重要性,以提高生产力。

本书主要介绍IEEE 1800-2005标准的SVA特性。

作者认为,这个标准的特点是为读者的项目设计实用的断言。然而,作者确实在独立的Chap中解释了IEEE 1800-2009的特性。 16给予新标准的好评。请注意,截至撰写本文时,许多2009年的功能都不被流行的模拟器支持,并且所提供的示例未被模拟。请将您的建议/更正发送给作者。

SystemVerilog断言和IEEE1800 SystemVerilog Umbrella System下的功能覆盖

SystemVerilog断言(SVA)和功能覆盖(FC)是IEEE1800 SystemVerilog标准的一部分。换句话说,SVA和FC是属于SystemVerilog的四种不同语言子集中的两种。

(1)用于功能验证的SystemVerilog面向对象语言(使用OVM / UVM类型库)

(2)用于设计的SystemVerilog语言

(3)SystemVerilog断言(SVA)语言

(4)SystemVerilog功能覆盖(FC)语言可以确认验证环境已经完全验证了您的设计。

如图1.3所示,SVA和FC是SystemVerilog的两个重要语言子集。

在任何设计中,都有三个主要的验证组件。 (1)激励发生器产生激励来驱动设计(2)响应检查器以查看设备是否符合设备规范。(3)覆盖组件可以根据设备规范确定结构上和功能上覆盖了DUT中的所有内容。

(1)激励产生。这需要创建不同的DUT需要执行的方式。例如,外设(例如USB)可能被建模为总线功能模式(或UVM(通用验证方法)代理),以通过SystemVerilog事务将traffic驱动到DUT。部署不同的技术以实现对设计的详尽覆盖。例如,约束随机,基于事务的,基于UVM的,基于内存的等等。这些主题超出了本书的范围。

图1.3 SystemVerilog IEEE 1800-2009下的SystemVerilog声明和功能覆盖组件

(2)响应检查。现在您已经激发了DUT,您需要确保设备已根据设备规格对该刺激做出了响应。这里是SVA与UVM监视器,记分牌和其他此类技术一起拍摄的地方。上广电将检查设计不仅要满足高层次的规范,还要满足低层次的组合和时间设计规则。

(3)功能覆盖。我们如何知道我们已经执行了设备指定的所有内容?代码覆盖率是一项措施。但是代码覆盖只是结构性的。例如,它会指出是否有条件执行。但是代码覆盖率并不知道条件本身是否正确,这就是功能覆盖(Functional Coverage)出现的地方(稍后我们将讨论功能覆盖)。功能覆盖给出了设计覆盖率的客观度量(例如,我们是否验证了从CPU到L2的所有不同的高速缓存访问转换(例如,写入,然后从同一地址读取)?代码覆盖不会给出这样的度量)。我们将在Chap19中详细讨论整个覆盖方法。

SystemVerilog断言的演进

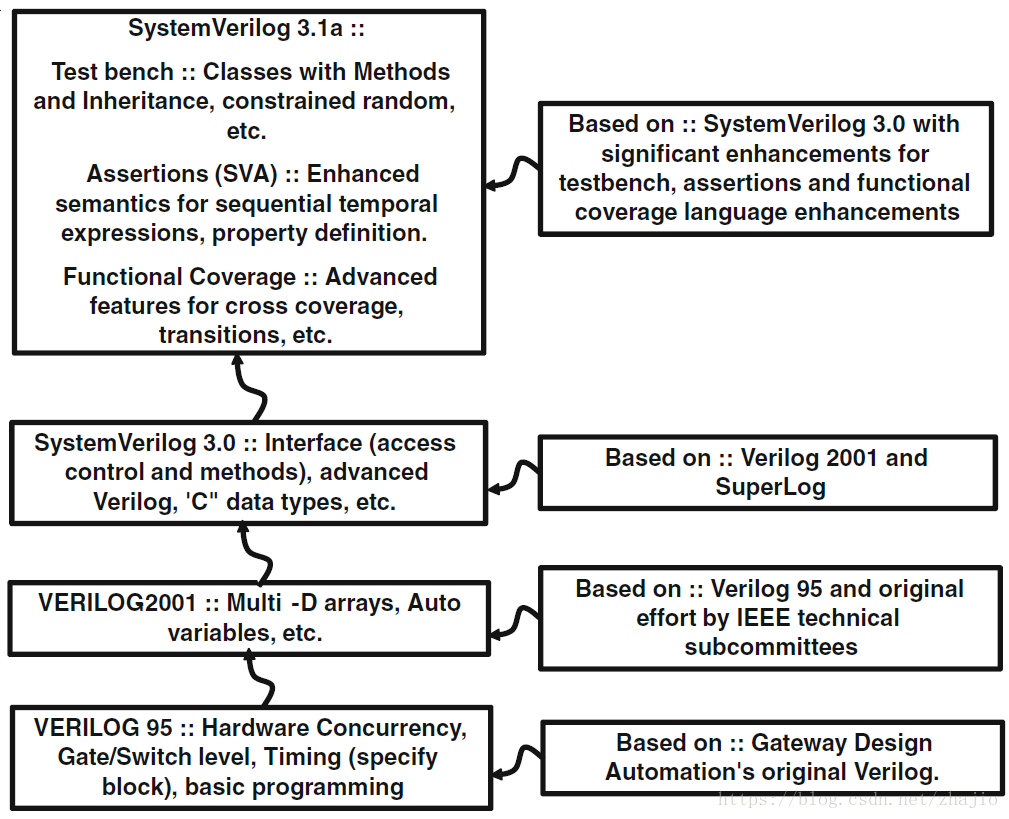

为了设置阶段,下面是Verilog对SystemVerilog演进的简要记录(图1.4和1.5)。从Verilog 95开始,我们使用多维数组和自动变量以及其他有用的功能,来到Verilog 2001。同时,功能验证正在消耗特定项目的更多资源。每个人都拥有完全不同的Verilog功能验证环境和方法。这不再可行。

业界认识到需要一种标准语言,可以设计和验证可重复使用的组件的设备和方法,以避免多语言繁琐的环境。Superlog,这是一种具有功能验证所需的高级构造的语言。 Superlog捐赠(与其他语言子集捐赠一起)以创建SystemVerilog 3.0,从中演化出SystemVerilog 3.1,为设计增加了新功能,但超过80%的新语言子集专用于功能验证。我们只能感谢Superlog发明者(与Verilog相同的发明人,即Phil Moorby)和Accelera技术小组委员会,他们有长远的眼光来设计这种强大的全包式语言。不再需要多语言解决方案。每个项目都不再需要重新发明轮子。

图1.4 SystemVerilog演进

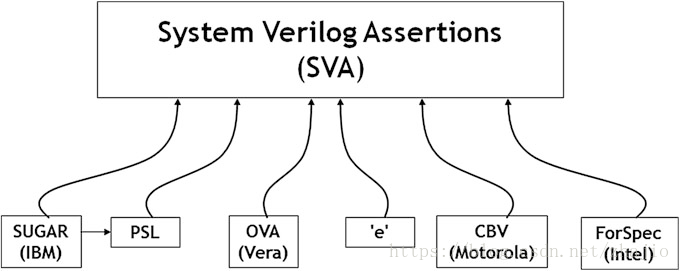

如图1.5所示,SystemVerilog Assertion语言来自许多不同的语言。这些语言的特征要么影响语言,要么直接作为语言语法/语义的一部分。

IBM的Sugar导致PSL。两者都有助于SVA 。其他贡献的语言是Vera,'e',摩托罗拉的CBV和英特尔的ForSpec。

图1.5 SystemVerilog assertion演进

简而言之,当我们使用SystemVerilog断言语言时,我们有利用断言语言的最新发展,这种语言从其他健壮的断言语言中受益。