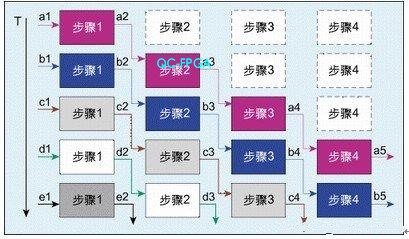

所谓流水线(pipeline)设计,通常来说是流水生产线。

同样,组合逻辑路径可以看作是一条生产线,路径上的每个逻辑单元都可以看作是一个阶段,都会产生时延。

如果不采用流水设计,前后级组合逻辑依次工作,那么这条路径的模型就是

原始的生产线。如果采用流水设计,那么前后级组合逻辑可以同时工作,就像新的生产线一样。

在FPGA设计中,通常在适当组合逻辑中插入寄存器,以提高速度。这里对于插入寄存器提高速度,我们暂不分析。

流水线模型

今天我们分析一下在实现CORDIC算法中,流水线操作和控制器操作的比较。

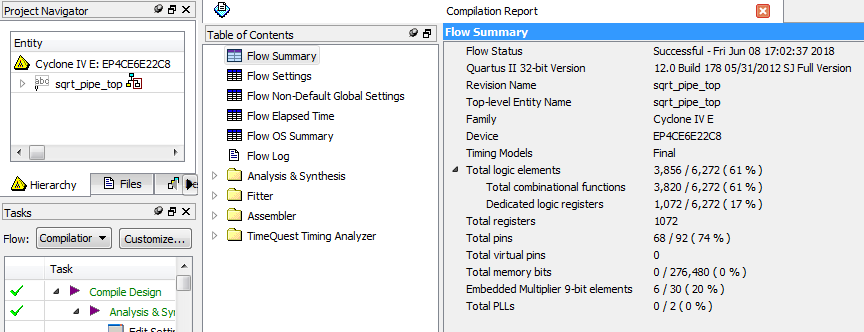

在实现CORDIC算法时,有两种方法。第一是使用流水线操作,不仅能够提高系统速度,而且能够加快输出的速度。

16次迭代流水线仿真输出如下图:

从上图可以看到,使用流水线方式,处理第一次输出需要等待16个时钟周期外,后面的输出将以流水的方式根据输入的有效而不断输出。这种流水线方式适用于要求连续输出的场景。

上图是在C4的FPGA上综合后的资源使用情况,可以看到,资源使用量非常大,其中大量的资源都浪费在加法器以及寄存器的使用上。乘法器资源也用了20%。

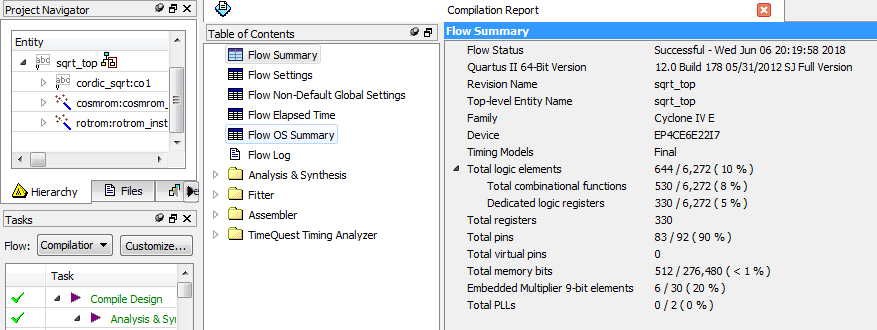

第二种方式是使用控制器的模式实现CORDIC算法。

上图是使用控制器的方式实现CORDIC算法,可以看到每个输出都需要等待16个时钟周期,时效性比流水线方式低很多,适用于不需要实时输出的场景。

上图为在C4的FPGA上综合后资源的使用情况。,可以看到,比起流水线操作,控制器方式资源使用大大减少。

上面简单分析了两种方式实现CORDIC算法。我们不能够说谁优谁劣,只能是在不同的场景使用不同的方法达到最后的设计功能。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间