目录

AT89S52单片机采用总线结构,使扩展易于实现,AT89S52单片机系统扩展结构如图所示:

(1)地址总线(Address Bus,AB):用于传送单片机发出的地址信号,以便进行存储单元和I/O接口芯片中的寄存器单元的选择。

(2)数据总线(Data Bus,DB):用于单片机与外部存储器之间或与I/0接口之间传送数据,数据总线是双向的。

(3) 控制总线(Control Bus,CB):控制总线是单片机发出的各种控制信号线。

三种总线的构造方式

1.P0口作为低8位地址/数据总线

AT89S51受引脚数目限制,P0口既用作低8位地址总线,又用作数据总线(分时复用),因此需增加一个8位地址锁存器。AT89S51访问外部扩展的存储器单元或1/O接口寄存器时,先发出低8位地址送地址锁存器锁存,锁存器输出作为系统的低8位地址 (A7~ A0)。随后,PO口又作为数据总线口 (D7~ D0) ,如图所示

2.P2口的口线作为高位地址线

P2口用作系统的高8位地址线,再加上地址锁存器提供的低8位地址便形成了系统完整的16位地址总线。

3.控制信号线

除地址线和数据线外,还要有系统的控制总线。这些信号有的就是单片机引脚的第一功能信号,有的则是P3口第二功能信号。包括:

(1) PSEN*作为外扩程序存储器的读选通控制信号

(2) RD*和WR*为外扩数据存储器和I/O的读、写选通控制信号

(3)ALE作为P0口发出的低8位地址锁存控制信号

(4)EA*为片内、片外程序存储器的选择控制信号

可见,AT89S52的4个并行I/O口,由于系统扩展的需要,真正作为数字I/O用,就剩下P1和P3的部分口线。

寻址结构图如下

地址空间分配和外部地址锁存器

1.存储器地址空间分配

实际系统设计中,既需要扩展程序存储器,又需要扩展数据存储器如何把片外的两个64KB地址空间分配给各个程序存储器、数据存储器芯片,使一个存储单元只对应一个地址,避免单片机发出一个地址时同时访问两个单元,发生数据冲突。存储器地址空间分配:

AT89S52单片机发出的地址码用于选择某个存储器单元,外扩多片存储器芯片中,单片机必须进行两种选择:

一是选中该存储器芯片,这称为“片选”,未被选中的芯片不能被访问。

二是在“片选”的基础上再根据单片机发出的地址码来对“选中”芯片的某一单元进行访问,即“单元选择”

通常把单片机系统的地址线笼统地分为低位地址线和高位地址线,“片选”都是使用高位地址线。实际上,16条地址线中的高、低位地址线的数目并不是固定的,只是习惯上把用于“单元选择”的地址线,都称为低位地址线,其余的为高位地址线。

常用的存储器地址空间分配方法有两种:线性选择法(简称线选法)和地址译码法(简称译码法)

译码法

使用译码器对AT89S51单片机的高位地址进行译码,译码输出作为存储器芯片的片选信号。这种方法能够有效地利用存储器空间,适用于多芯片的存储器扩展。常用的译码器芯片有74LS138 (3线-8线译码器)74LS139 (双2线-4线译码器) 和74LS154 (4线-16线译码器)

(1)74LS138

3线-8线译码器,有3个数据输入端,经译码产生8种状态。引脚如图所示:

真值表:

由表可见,当译码器的输入为某一固定编码时,其输出仅有一个固定的引脚输出为低电平,其余的为高电平。输出为低电平的引脚就作为某一存储器芯片的片选信号。

(2)74LS139

双2线-4线译码器。这两个译码器完全独立,分别有各自的数据输入端、译码状态输出端以及数据输入允许端,其引脚如图所示。

真值表见表(只给出其中一组)

以74LS138为例,如何进行地址分配:

例如,要扩8片8KB的RAM 6264,如何通过74LS138把64KB空间分配给各个芯片?

由74LS138真值表可知,把G1接到+5V,G2A*、G2B*接地,P2.7、P2.6、P2.5 (高3位地址线) 分别接74LS138的C、B、A端由于对高3位地址译码,这样译码器有8个输出Y7*~ Y0*,分别接到8片6264的各“片选”端,实现8选1的片选。

低13位地址 (P2.4~ P2.0,P0.7~ P0.0) 完成对选中的6264芯片中的各个存储单元的“单元选择”这样就把64KB存储器空间分成8个8KB空间了。

这里采用全地址译码方式。因此,AT89S51发出16位地址时,每次只能选中某一芯片及该芯片的一个存储单元

这里选择第0个芯片,即高地址位为(0,0,0),这个对应的是片选芯片,低地址位有13位,这些对应了8K的存储单元

如何用74LS138把64KB空间全部划分为4KB的块呢?

4KB空间需12条地址线,而译码器输入只有3条地址线 (P2.6 ~ P2.4) ,P2.7没有参加译码,P2.7发出的0或1决定选择64KB存储器空间的前32KB还是后32KB,由于P2.7没有参加译码,就不是全译码方式,前后两个32KB空间就重叠了。那么,这32KB空间利用74LS138译码器可划分为8个4KB空间。

如果把P2.7通过一个非门与74LS138译码器G1端连接起来,如图所示,就不会发生两个32KB空间重叠的问题了。这时,选中的是64KB空间的前32KB空间,地址范围为0000H~7FFFH(低32KB空间)

前32K的地址空间

后32K的地址空间

2.外部地址锁存器

受引脚数的限制,PO口兼用数据线和低8位地址线,为了将它们分离出来,需在单片机外部增加地址锁存器。目前,常用的地址锁存器芯片有74LS373、74LS573等

(1)锁存器74LS373

是一种带三态门的8D锁存器,其引脚如图所示:

内部结构如图所示:

低8位的地址信息存储在锁存器中,与高八位地址信息共同发出16位地址信息,低8位地址信息,存储在锁存器中后,P0空闲下来,则可用来传输数据信息。

AT89S51与74LS373锁存器的连接如图8-9所示

静态数据存储器RAM的并行扩展

AT89S52单片机片内有256B RAM,往往不能满足实际需要,必须片外扩展数据存储器。数据存储器分为动态数据存储器与静态数据存储器。在单片机应用系统中,如果外部扩展动态数据存储器,还需要有对应的刷新电路,所以,在单片机的外部扩展的数据存储器都采用静态数据存储器(SRAM)

对外部扩展的数据存储器空间访问,P2口提供高8位地址,P0口分时提供低8位地址和8位双向数据总线。片外数据存储器RAM的读和写由单片机的RD*(P3.7) 和WR* (P3.6) 信号控制。

(1)常用的静态RAM (SRAM)芯片

单片机系统中常用的RAM芯片的典型型号有6116 (2KB),6264(8KB) ,62128 (16KB) ,62256 (32KB)

各引脚功能:

A0~A14:地址输入线

D0~D7:双向三态数据线

CE*:片选信号输入线。对6264芯片,当24脚 (CS)为高电平,且CE*为低电平时才选中该片

OE*:读选通信号输入线,低电平有效

WE*:写允许信号输入线,低电平有效

VCC一工作电源+5V。

GND 一地

RAM存储器有读出、写入、维持3种工作方式:

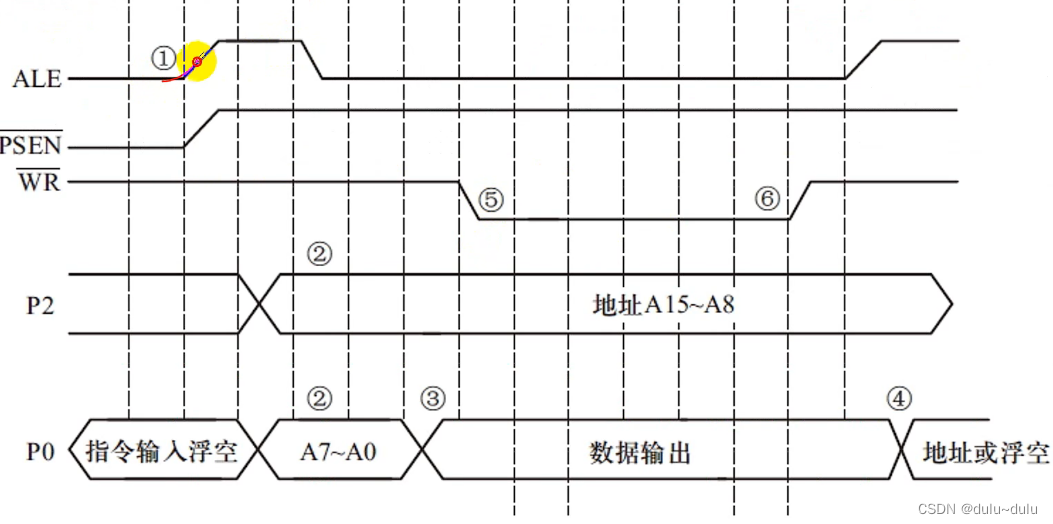

(2)外扩数据存储器的读写操作时序

对片外RAM读和写两种操作时序的基本过程相同

1.读片外RAM操作时序

若外扩---片RAM,应将WR*脚与RAM的WE*脚连接,RD*脚与芯片OE*脚连接

2.写片外RAM操作时序

“MOVX @DPTR,A”指令。指向片外RAM写数据,单片机执行令执行后,单片机的WR*信号为低有效,此信号使RAM的WE* 端被选通。

开始的过程与读过程类似,但写的过程是CPU主动把数据送上P0口总线,故在时序上,CPU先向P0口总线上送完8位地址后,在S3状态就将数据送到P0口总线 (③处) 。此间,P0总线上不会出现高阻悬浮现象。

(3)AT89S52单片机与RAM的接口设计与软件编程

AT89S52对片外RAM的读和写由单片机的RD*(P3.7)和WR(P3.6) 控制,片选端由译码器译码输出控制。因此设计时,主要解决地址分配、数据线和控制信号线的连接问题。在与高速单片机连接时,还要根据时序解决读/写速度匹配问题。

图为用线选法扩展AT89S51外部数据存储器电路。图中数据存储器选用6264,该芯片地址线为A0~A12,故单片机剩余地址线为3条。

用线选可扩展3片6264

用译码法扩展外部数据存储器的接口电路如图所示

数据存储器62128,芯片地址线为A0~A13,剩余地址线为两条,若采用2线-4线译码器可扩展4片62128。各片62128芯片地址分配如表所示:

[例8-1]编写程序将片外数据存储器中5000H~50FFH单全部清“0”。

方法1:用DPTR作为数据区地址指针,同时使用字节计数器。

方法2:用DPTR作为数据区地址指针,但不使用字节计数器,而是比较特征地址。

单片机片外数据区读/写数据过程

当程序运行中,执行“MOV”类指令时,表示与片内RAM交换数据:当遇到“MOVX”类指令时,表示对片外数据存储器区寻址片外数据存储器区只能间接寻址。

例如,把片外6000H单元的数据送到片内RAM 50H单元中。

向片外数据区写数据的过程与读数据的过程类似例如,把片内50H单元的数据送到片外4000H单元中。

片外存储器只能间接寻址:

单片机读写片外数据存储器中内容,除了用“MOVXA@DPTR”和“MOVX @DPTR,A”外,还可用指令“MOVXA,@Ri”和“MOVX @Ri,A”。这时P0口装入Ri中内容 (低8位地址),而把P2口原有的内容作为高8位地址输出。

[例8-4]编程,将程序存储器中以TAB为首址的32个单元内容依次传送到外部RAM以4000H为首址的区域。

DPTR指向标号TAB首地址。RO既指示外部RAM的地址,又表示数据标号TAB的位移量。程序为一循环程序,循环次数为32,R0的值达到32就结束循环。

E2PROMA的并行扩展

在以单片机为核心的智能仪器仪表、工业监控等应用系统中,某些动态测试数据以及某些状态参数数据,不仅要求能够在线修改保存而且断电后能保持。断电后的数据的保护可采用电可擦除写入的存储器E2PROM,其突出优点是能够在线擦除和改写。

E2PROM有并行和串行之分,并行的速度比串行的快,容量大。例如并行的E2PROM2864A的容量为8kx8位。而串行12C接口的E2PROM与单片机的接口简单,比较流行的是ATMEL公司的串行芯片AT24C02/AT24C08/AT24C16等。

常见的并行芯片有2816/2816A,2817/2817A,2864A等。

引脚如图所示:

其主要性能见表(表中芯片均为Intel公司产品):

2816、2817和2864A的读出数据时间均为250ns,写入时间10ms。

下面对E2PROM2864A的4种工作方式说明:

1.读方式

当CE*和OE*均为低而WE*为高时,内部的数据缓冲器被打开数据送上总线,此时可进行读操作。

2.写方式

2864A提供两种数据写入方式:页写入和字节写入

(1)页写入

为提高写速度,2864A片内设置16字节的“页缓冲器”,将整个存储器阵列划分成512页,每页16字节。高9位(A12~A4)确定页,低4位(A3~A0)选择页缓冲器中的16个地址单元之一。

写操作分两步来实现:

第一步,在软件控制下把数据写入页缓冲器,这步称为页装载与一般的静态RAM写操作是一样的。

第二步,在最后一个字节(即第16个字节)写入到页缓冲器后20ns自动开始,把页缓冲器的内容写到E2PROM阵列中对应地址的单元中,这一步称为页存储。

写方式时,CE*为低,在WE*下降沿地址码A12~A0被片内锁存器锁存,在WE*上升沿数据被锁存。

片内有一个字节装载限时定时器,只要时间未到,数据可随机地写入页缓冲器。在连续向页缓冲器写数据过程中,不用担心限时定时器会溢出,因为每WE*当下降沿时,限时定时器自动被复位并重新启动计时。

限时定时器要求写一个字节数据时间TBLW须满足:

3us<TBLW<20us,这是正确对2864A页面写操作的关键。当一页装载完毕,不再有WE*信号时,限时定时器将溢出,页存储操作随即自动开始。首先把选中页的内容擦除,然后写入的数据由页缓冲器传递到E2PROM阵列中。

(2)字节写入

与页写入类似,写入一个字节,限时定时器就溢出。

3.数据查询方式

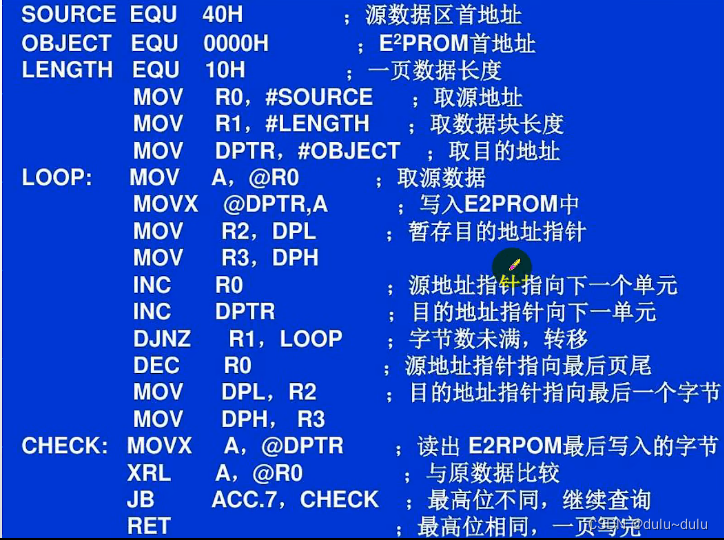

用软件来检测写操作中页存储周期是否完成。在页存储期间如对2864A执行读操作,那么读出的是最后写入的字节,若芯片的转储工作未完成,则读出数据的最高位是原来写入字节最高位的反码据此,单片机可判断芯片的编程是否结束。如果读出的数据与写入的数据相同,表示芯片已完成编程,可继续向2864A装载下一页数据。

4.维持方式

当CE*为高电平时,2864A进人低功耗维持方式。此时,输出线呈高阻态,芯片的电流从140mA降至维持电流60mA。

AT89S52对2864A进行写操作时所用指令包括:

MOVX @DPTR,A

MOVX @Ri,A

AT89S52对2864A进行读操作时所用指令包括

MOVX A,@DPTR

MOVX A,@Ri

示例:

编一个写入一页(16个字节)数据到E2PROM 2864A的子程序设写入的数据取自片内RAM40H开始的源数据区