目录

SPI 介绍

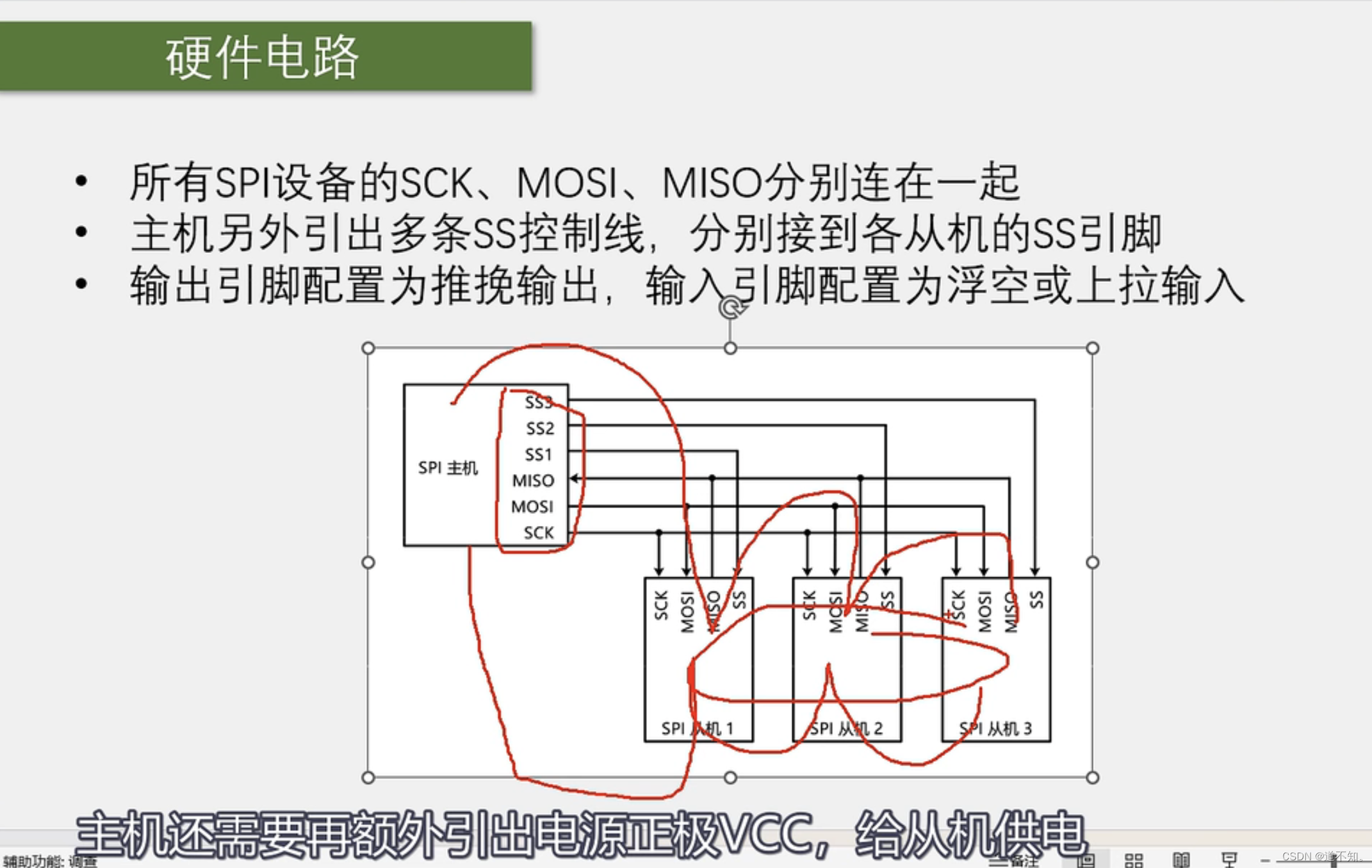

硬件电路

推挽输出,高低电平都有很强的驱动能力,使得上升沿和下降沿都很迅速。

当ss为高电平时,MISO默认为高阻态(高阻态相当于引脚断开,不输出任何电平)为了防止多个MISO冲突

移位示意图

SPI通信的基础是交换一个字节

上升沿()移出,下降沿()移入。

软件SPI

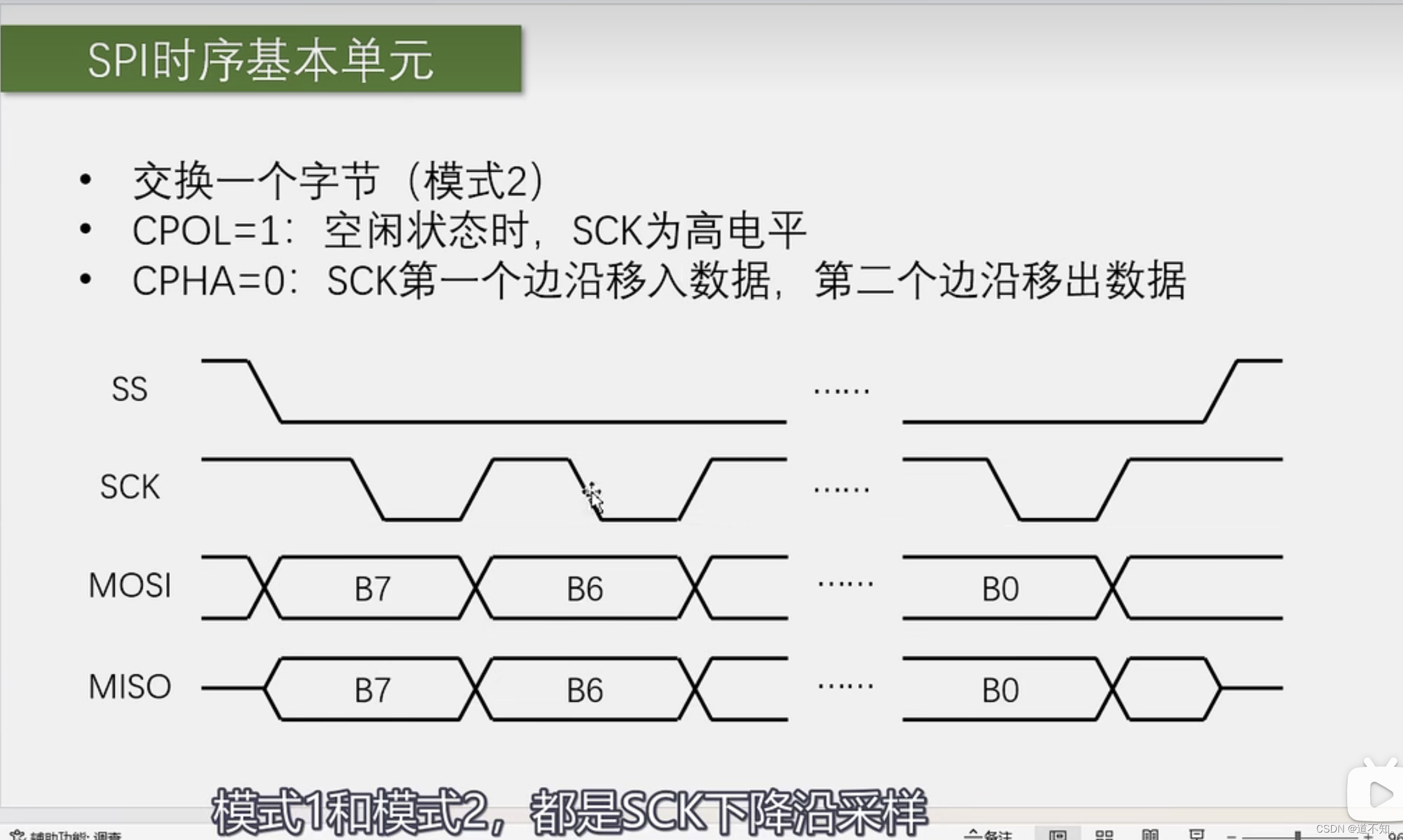

SPI时序基本单元

起始终止

CPOL时钟极性(决定空闲状态SCK的电平),CPHA时钟相位(决定第一个时钟采样移入还是第二个时钟采样移入).组合起来有4种模式.

如果想交换多个字节,SS继续为低电平

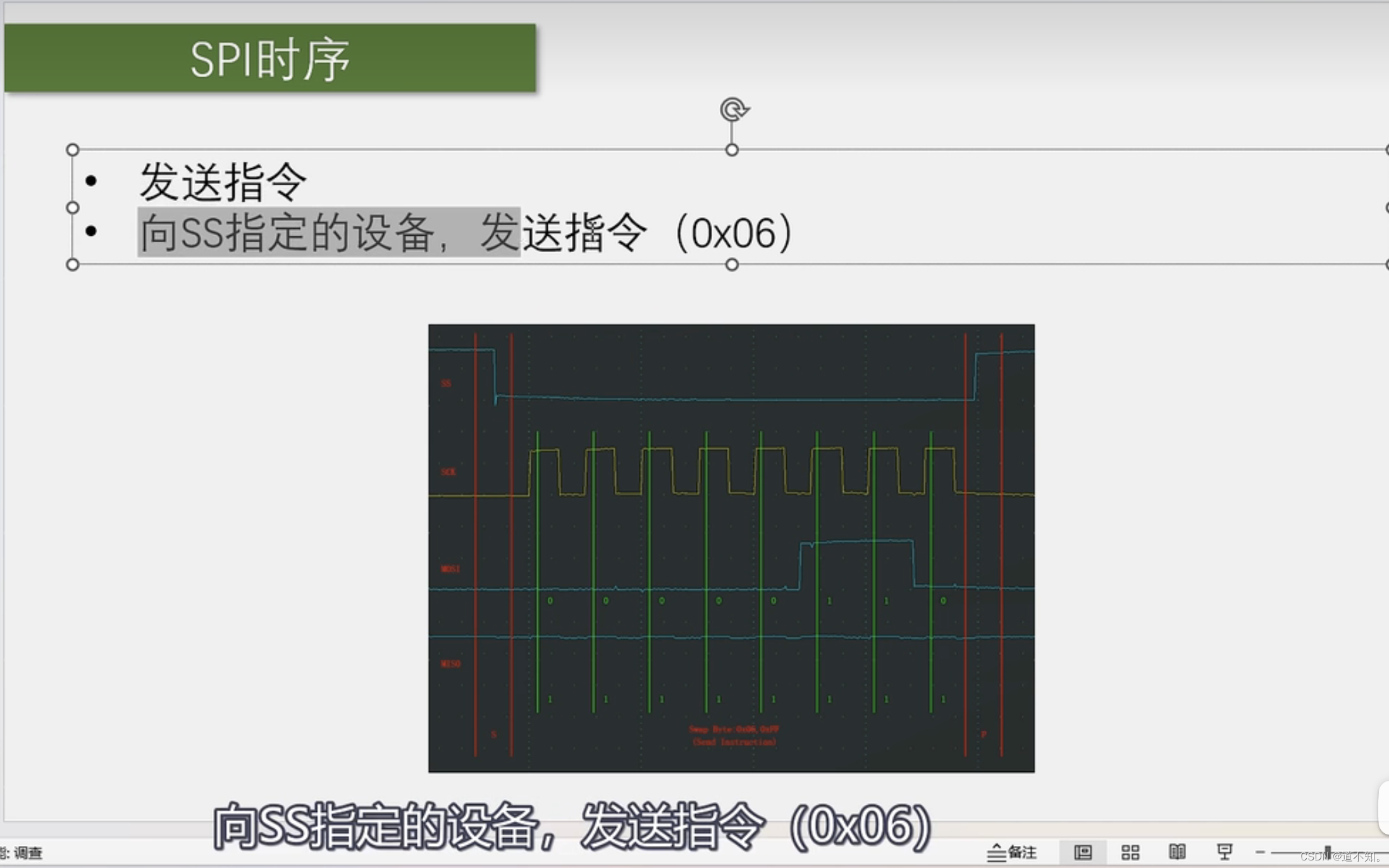

SPI时序

W25Q64

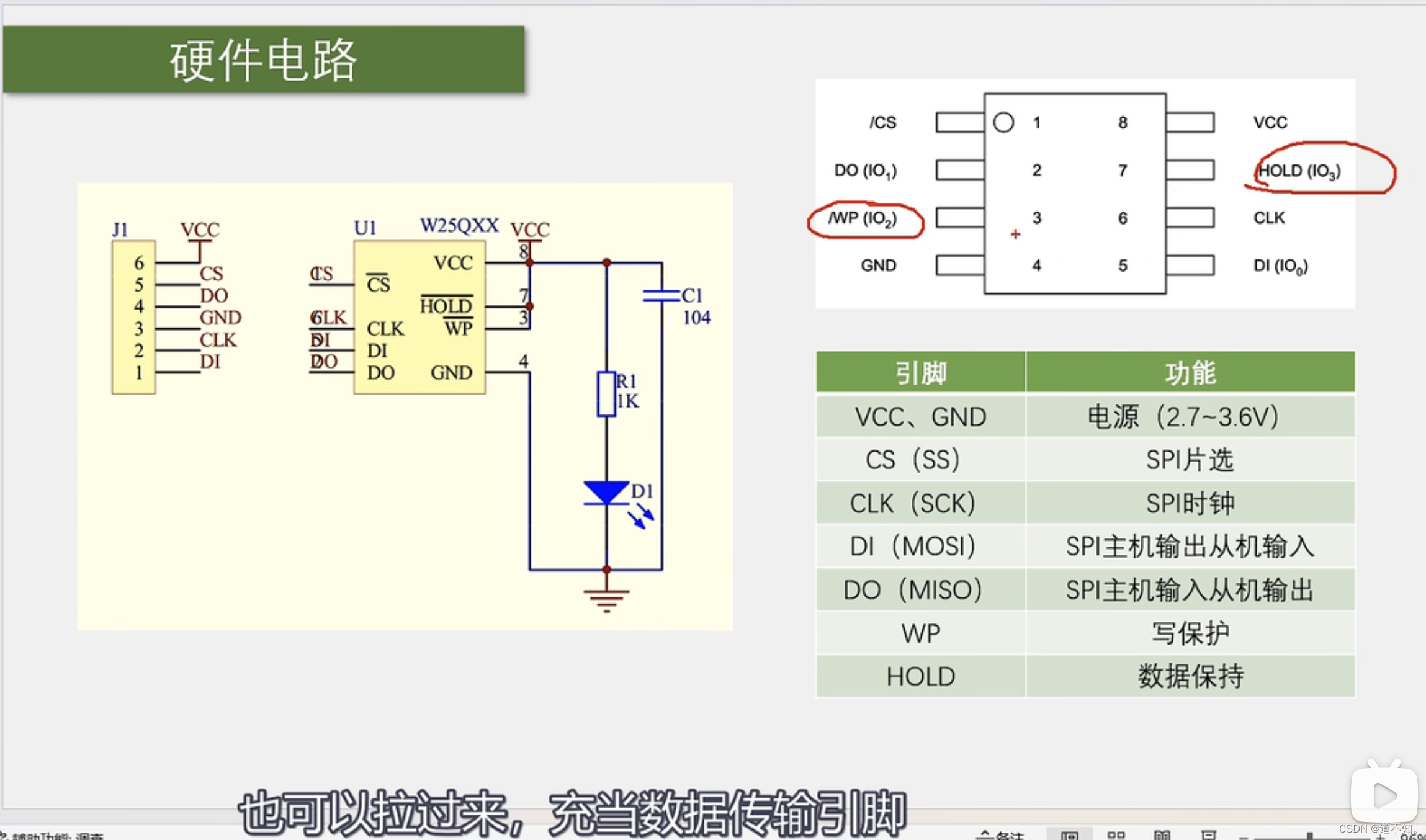

硬件电路

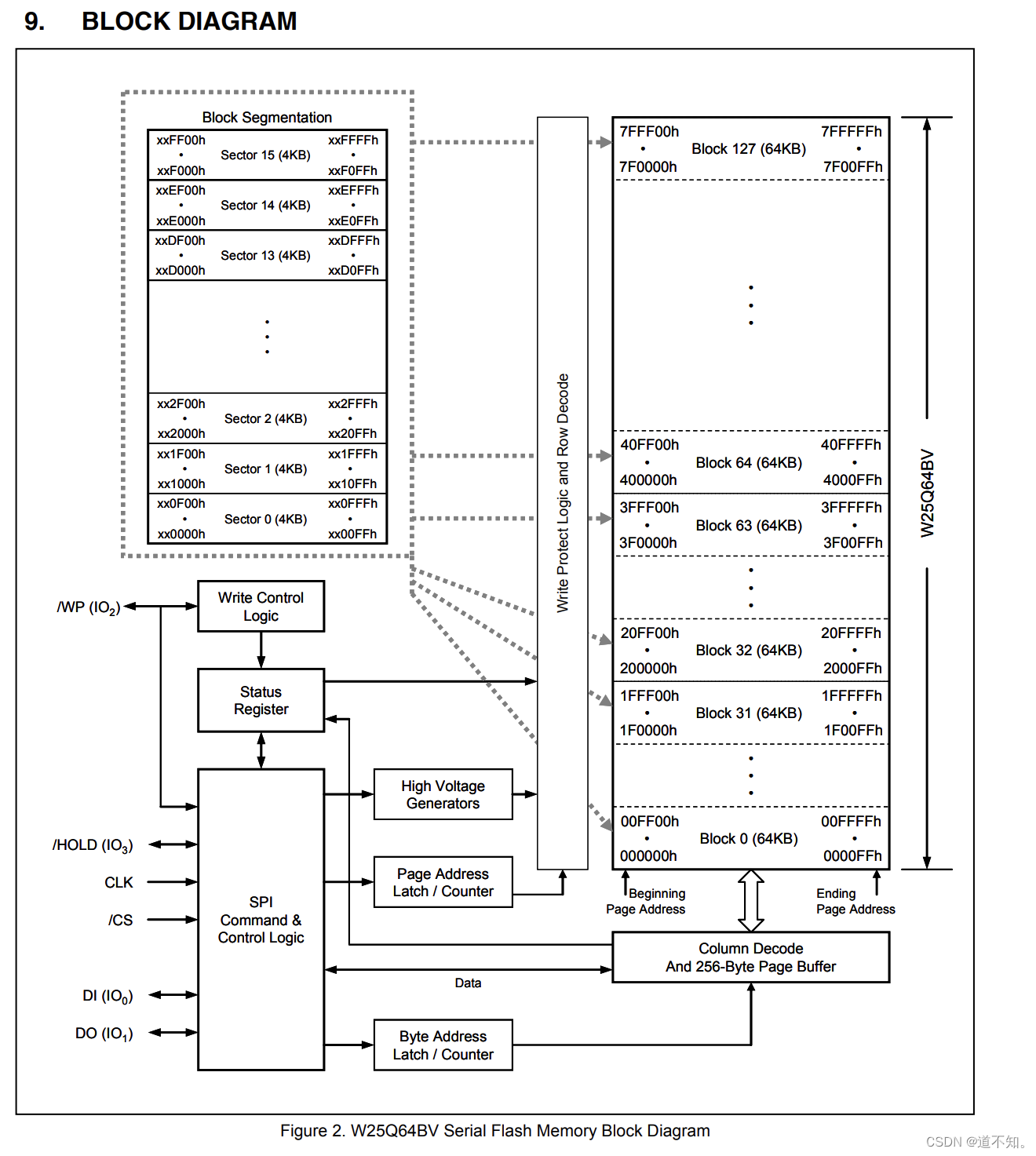

W25Q64框图

- 主要有四个部分:Flash空间的划分、SPI控制逻辑、状态寄存器、256字节页缓冲区。

整个存储空间,首先划分为若干块,对于每一块划分为若干扇区。对于整个存储空间,会划分为若干页,每一页256kb

所以一页内的地址取决于最低一个字节,高位两个字节对应页地址前两个字节进入页地址锁存器里,最后一个字节进入字节地址锁存器里。页地址通过写保护和行解码来选择哪一页,字节地址通过列解码和256字节页缓存进行指定地址读写操作。

256字节页缓冲区是一个256字节RAM存储器

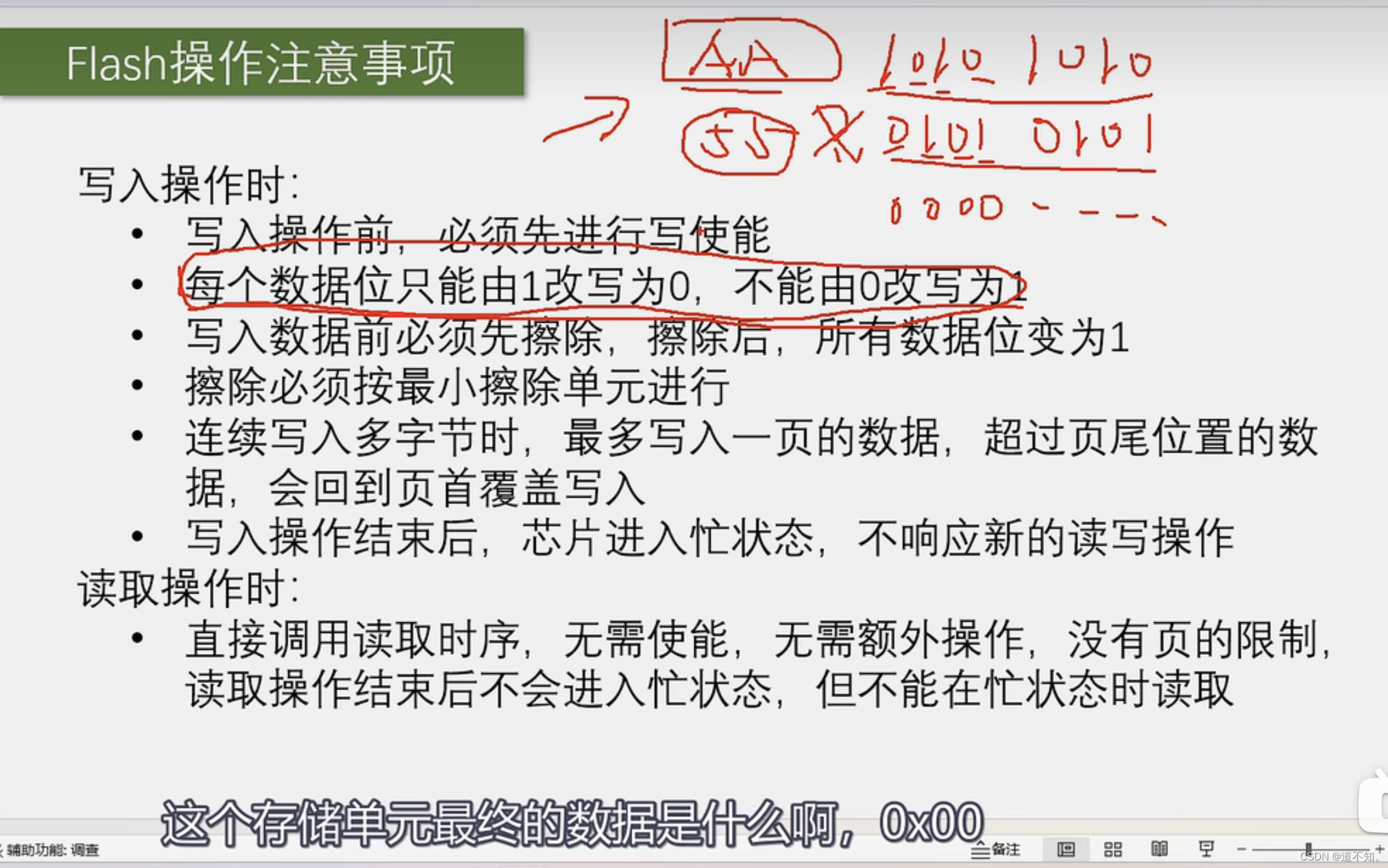

Flash操作注意事项

擦除按最小擦除单元扇区(4kb)

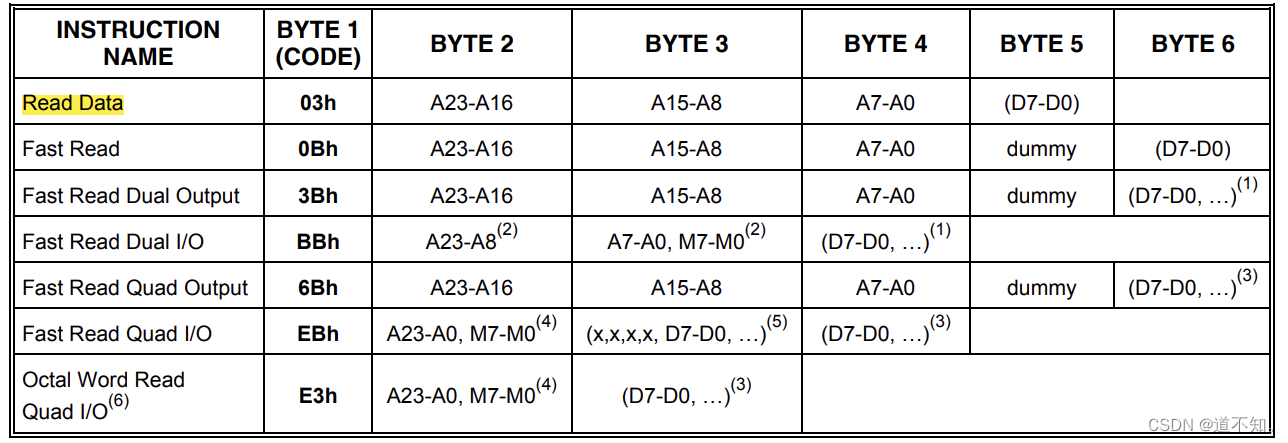

指令集

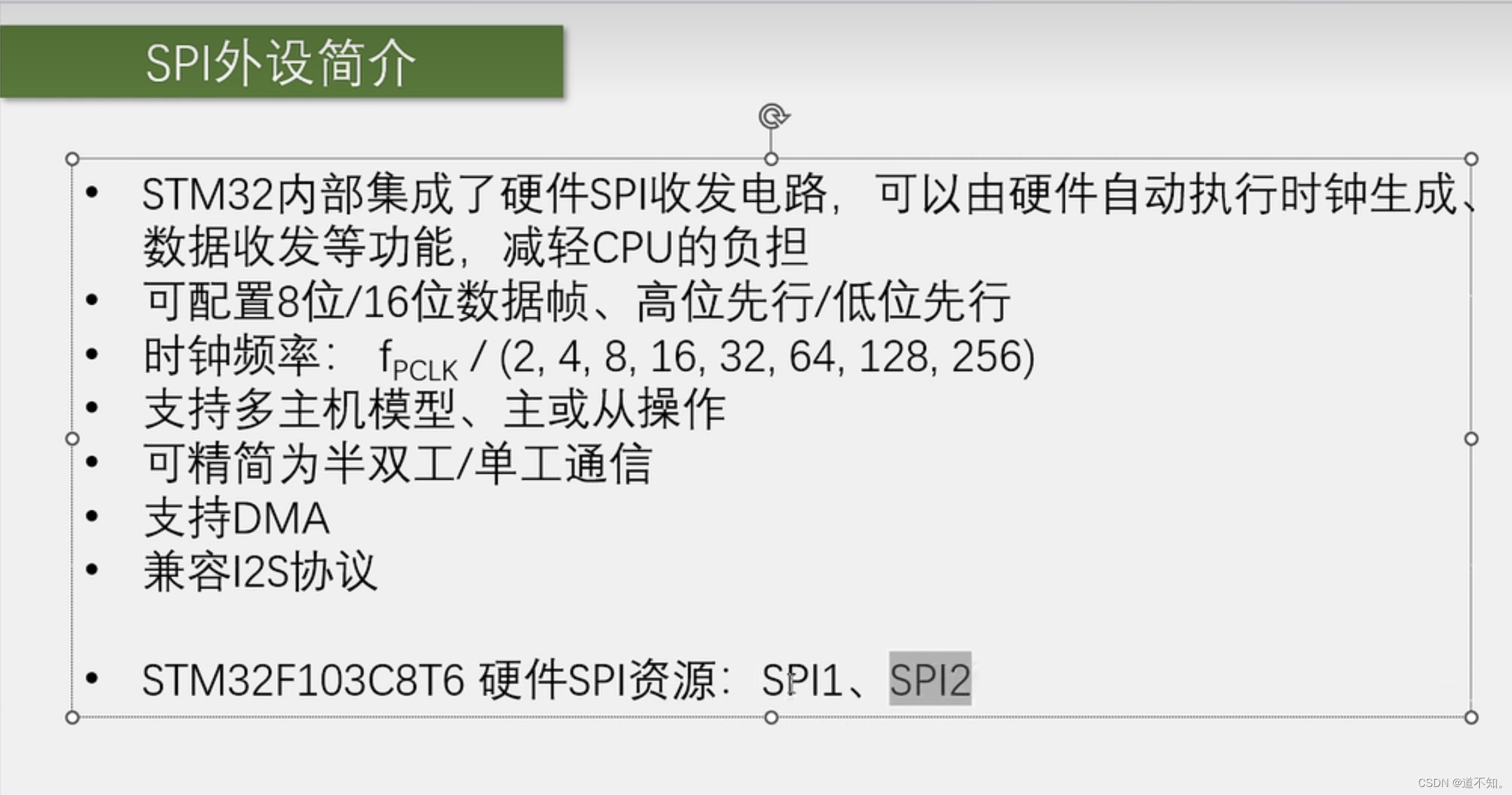

硬件SPI

软件SPI是通过手动翻转电平来实现时序。硬件SPI使用stm32内部的SPI外设实现时序

串口USART是低位先行,SPI和I2C是高位先。

时钟频率:SP1挂载在APB2,频率是72MHZ,SOI2挂载在APB1频率32MHZ。

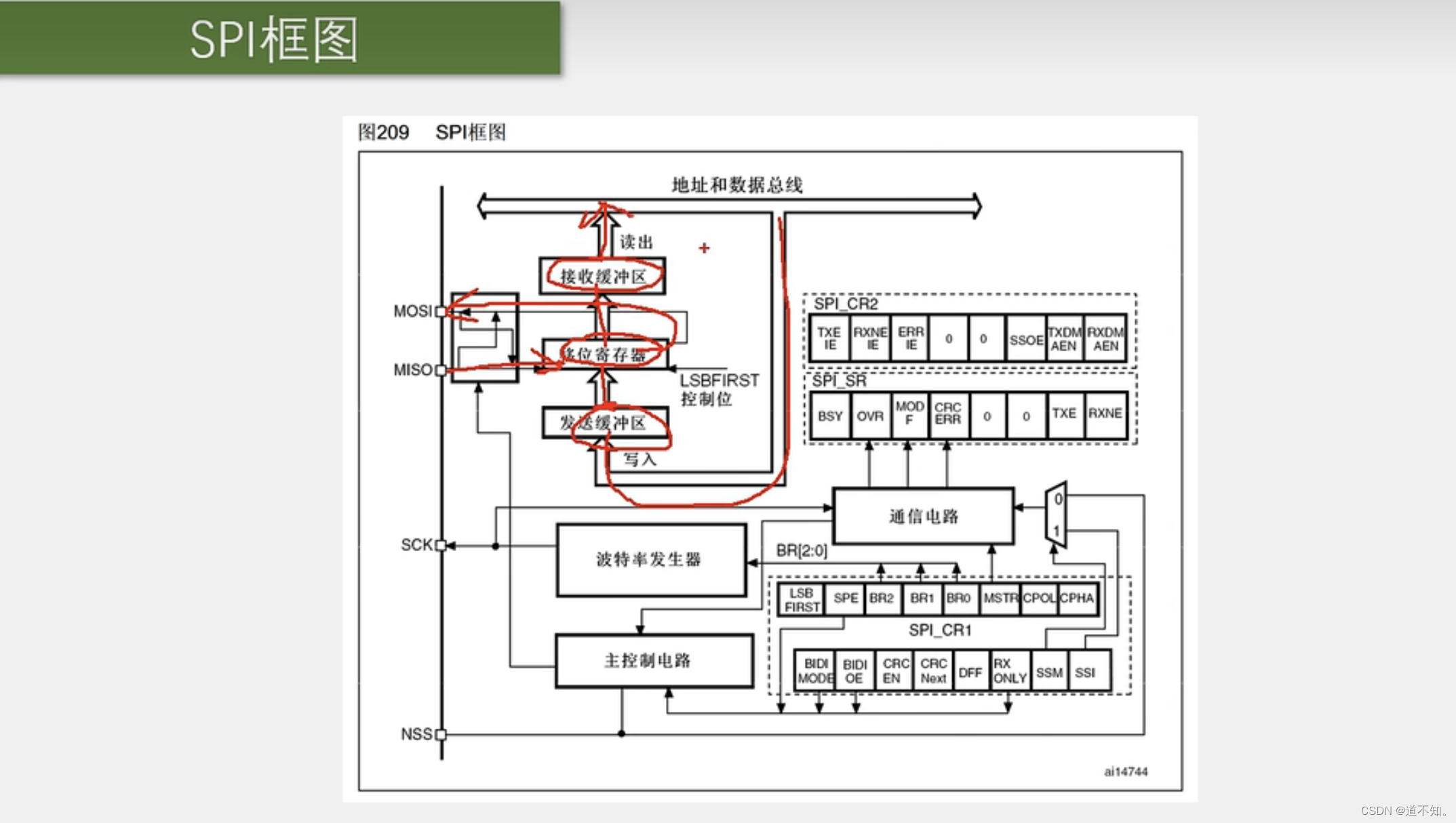

SPI框图

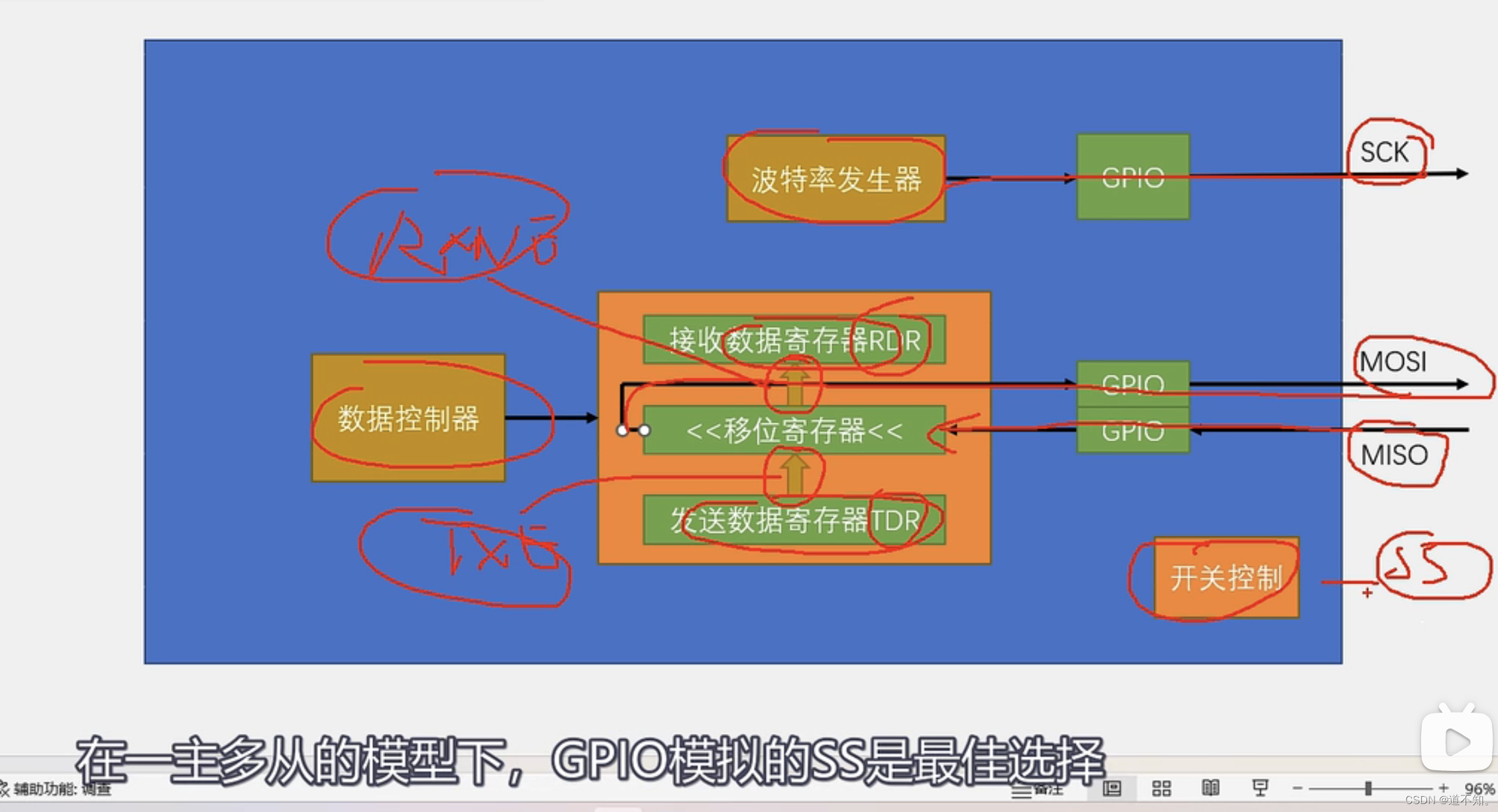

大致流程: 发送数据先写入TDR,然后转入移位寄存器发送,发送的同时接收数据,将接收到的数据转到RDR,将数据从RDR读出。

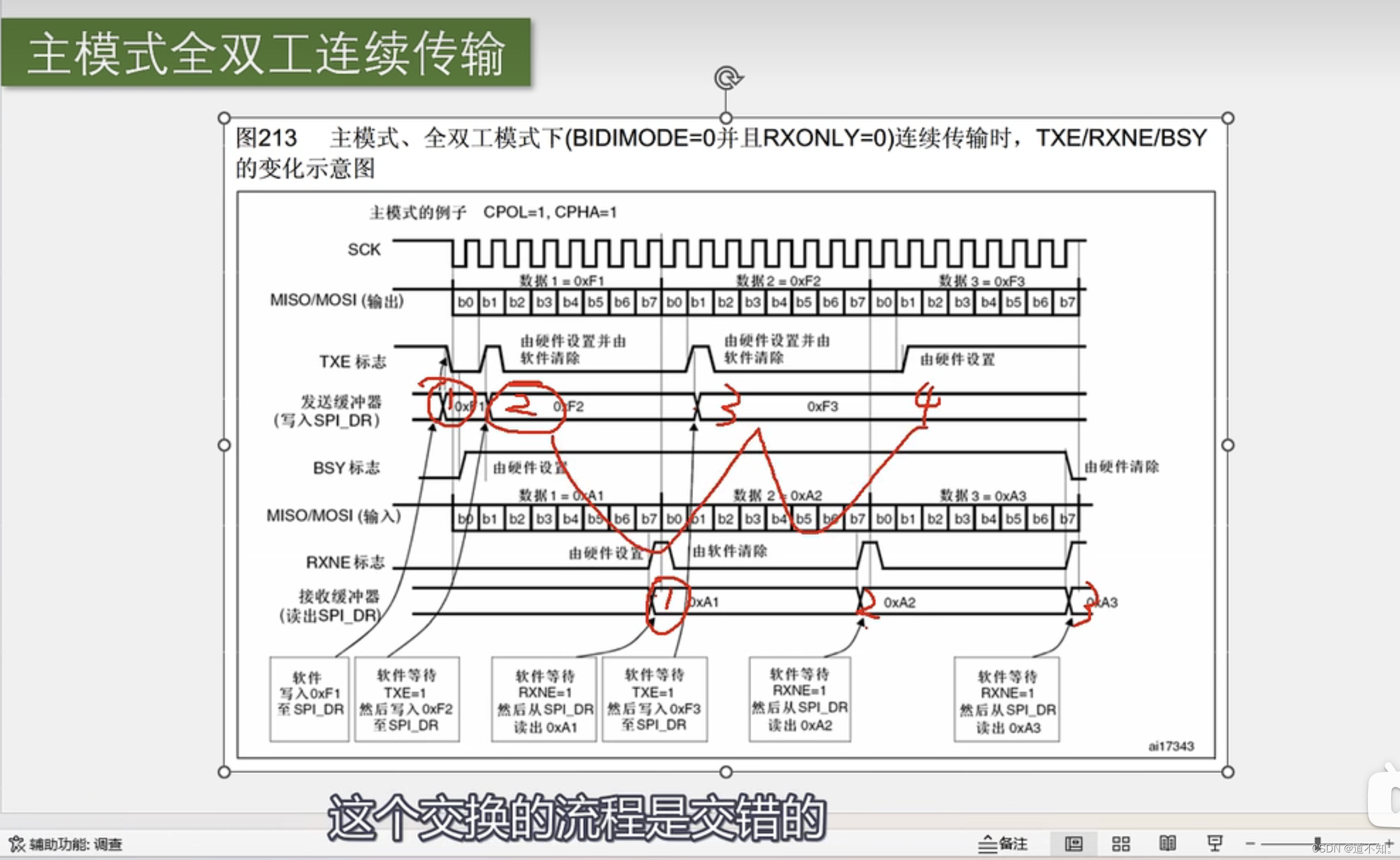

主模式全双工连续传输

效率高

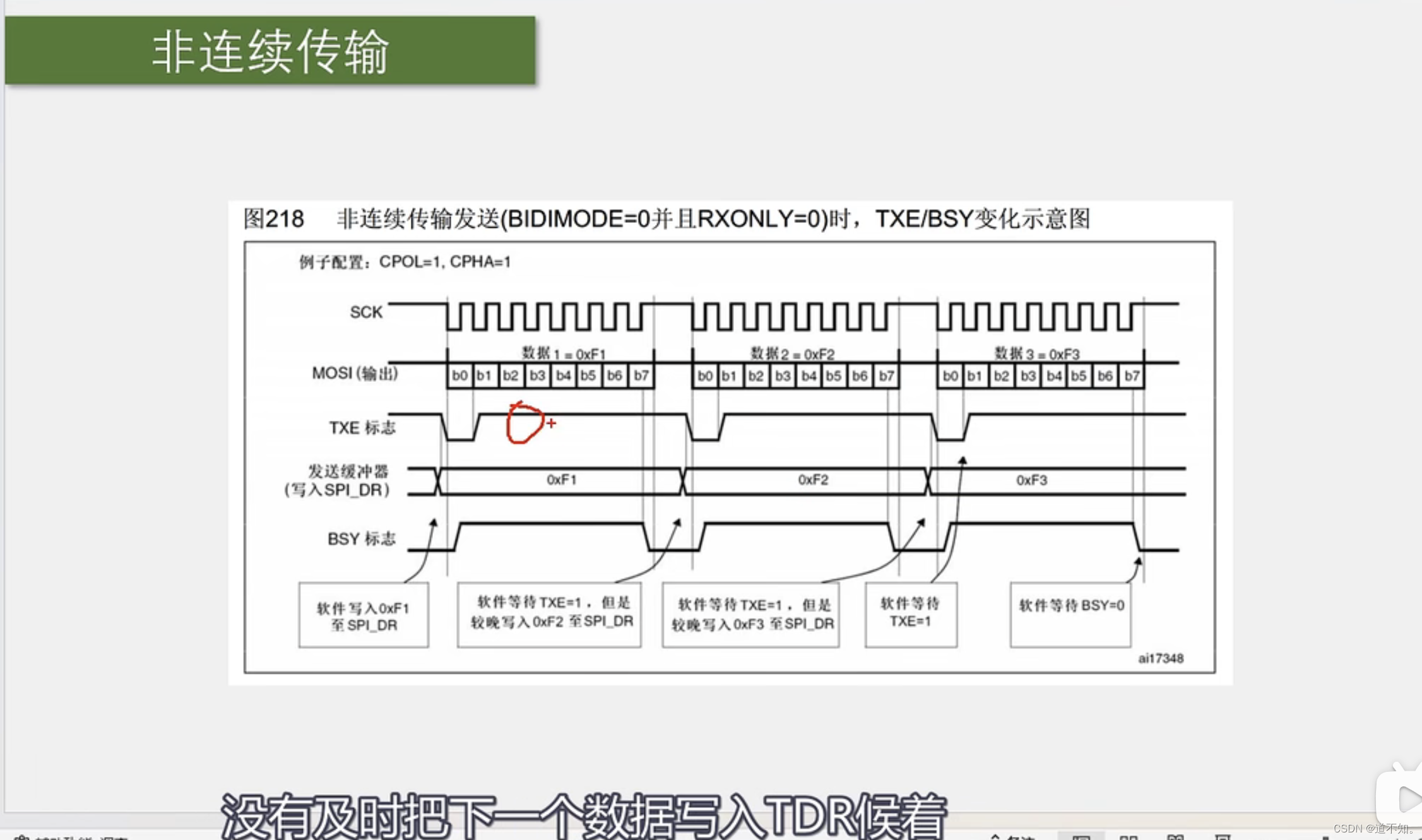

非连续传输

可以大致分为四步:等待 TXE为1,写入发送的数据至TDR,等待RXNE为1,读取RDR接收的数据。

非连续传输没有及时把下一个数据在TDR候着,所以在字节与字节之间会产生间隙,当频率低时,影响不大,但当频率高时会产生较大影响。