TLB(Translation Lookaside Buffer)是什么?

- 通过一个线性地址访问一个物理页。比如:一个DWORD,其实未必真正读取的是4个字节。先读取的PDE再读取PTE,最后才读取的4个字节的页。

- 在2-9-9-12分页中会读取24个字节,如果跨页,可能会读取的更多。

- 为了提高效率,只能做记录。

- CPU内部做了一个表,来记录这些东西,这个表格是存储在CPU内部的,它的读写速度和寄存器一样快,TLB(Translation Lookaside Buffer)。

TLB结构

| LA(线性地址) | PA(物理地址) | ATTR(属性) | LRU(统计) |

|---|---|---|---|

| 0x12345678 |

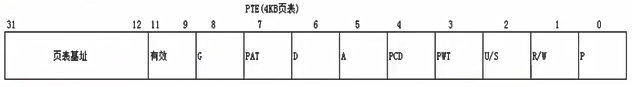

- ATTR(属性):属性是PDPE(PDPT:页目录指针表)、PDE、PTE三个属性AND(与运算)起来的,如果是10-10-12分页形式就是PDE and(与运算) PTE。

- 不同的CPU这个表的大小不一样。

- 只要CR3(指向当前进程页表)改变了,TLB立马刷新,一核一套TLB。

操作系统的高2G映射基本不变,如果CR3改变了,TLB刷新,重建高2G以上很浪费。所以PDE核PTE中有个G标志位,如果G位为1,刷新TLB时将不会刷新 PDE/PTE的G位为1的页。

当TLB满了,根据统计信息将不常用的地址废弃,保留最近常用的。

TLB种类

TLB在x86体系的CPU里的实际应用最早是从Intel的486CPU开始的,在x86体系的CPU里面,一般都设有如下4组TLB:

- 缓存一般页表(4KB字节页面)的指令页表缓存(Instruction-TLB)。

- 缓存一般页表(4KB字节页面)的数据页表缓存(Data-TLB)。

- 缓存大尺寸页表(2MB/4MB字节页面)的指令页表缓存(Instruction-TLB)。

- 缓存大尺寸页表(2MB/4MB字节页面)的数据页表缓存(Data-TLB)。

普通页都是4KB。如果是10-10-12分页形式中,大页是4MB。如果是2-9-9-12分页形式中,大页是2MB。

练习

- 体验TLB的存在

- 给某个线性地址挂一个物理页,如线性地址A。给它挂一个物理页B。挂完物理页以后,再把这个线性地址A的物理页改成C。

- 改成C以后再去读取这个线性地址的内容,会发现读取的仍然是B物理页里面的值,而不是C物理页中的值。

- 为什么呢?因为CPU第一次用这个线性地址的时候就把它的映射关系存储在了TLB中,这个线性地址如果不再使用它,CPU就又缓存原来的。

- 虽然把线性地址A的物理页改为C,但是并没有读写线性地址A,但是系统不知道,所以用的就是旧的。

- 全局页的意义

- 将G位修改为1,体会全局页和非全局页在TLB中是什么情况。

- INVLPG指令的意义

- 可以把TLB里面的某些值,也就是线性地址和物理地址的映射关系,把某些不想要的映射关系删掉。