问题记录

SDI显示项目要求:当外部摄像头无接入时,FPGA产生彩条给显示芯片。当外部摄像头有接入时,显示数据来自于海思。目前能成功显示,但是需要把输出给显示驱动芯片的时钟取反后才可以。尝试使用output delay约束不成功。

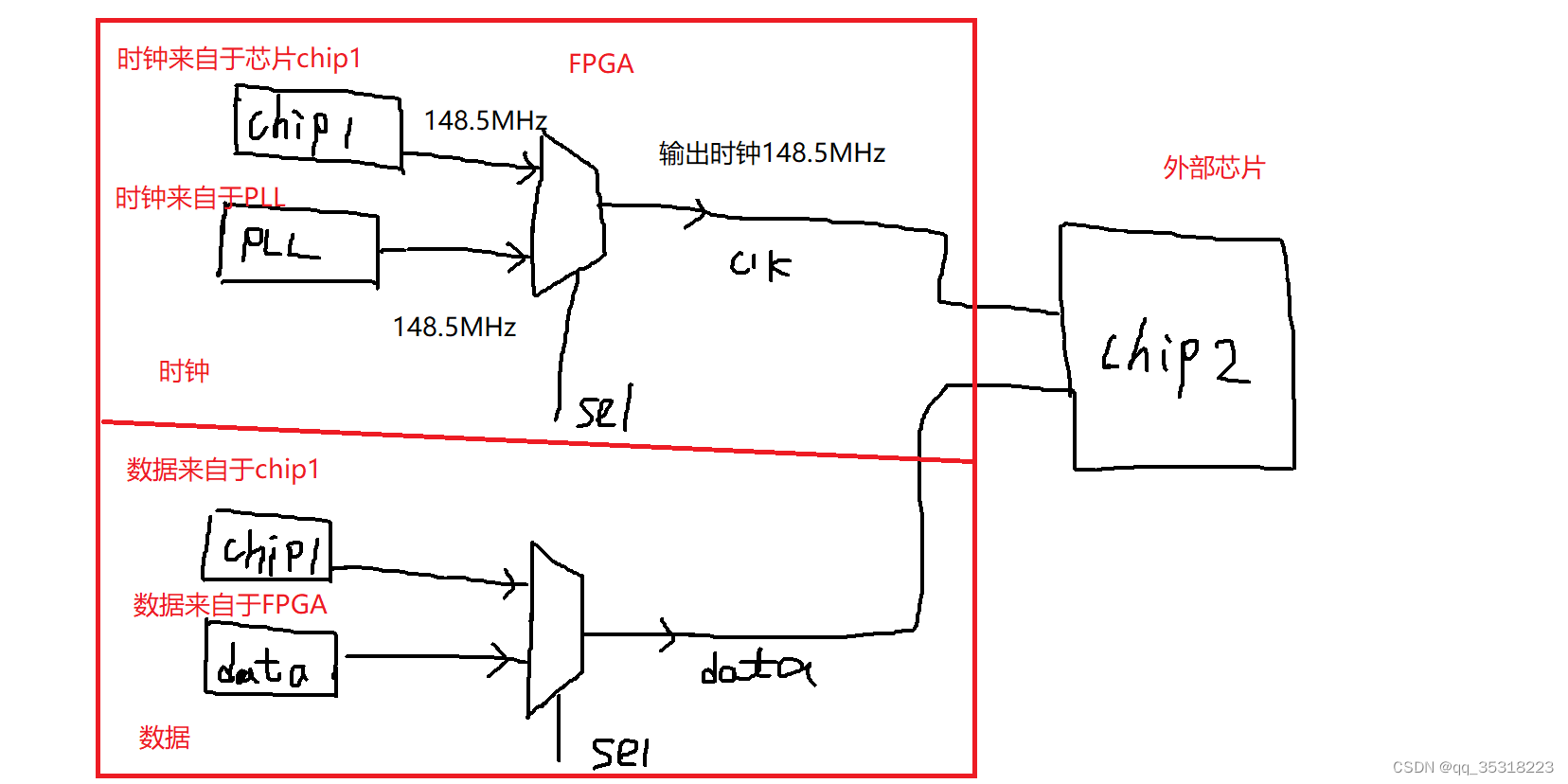

项目架构描述

如下图:

1.FPGA对外输出一组随路时钟和数据。

2.时钟和数据分别来自于两个地方,通过选择器进行选择,一个时刻只能选择一个时钟或数据,即要么选择海思时钟和数据;要么选择FPGA产生的彩条时钟和数据。

3.随路时钟均是148.5MHz。

4.VO1_clk 和VO1_data来自于海思,时钟频率148.5MHz。

5.video_pclk和video_data来自于FPGA内部,时钟频率148.5MHz。

6.gs2971_ch1_lock是有无摄像头接入标志。

assign pclk = (gs2971_ch1_lock==1'b1) ? VO1_clk : video_pclk;

assign pixel_o[19:10] = (gs2971_ch1_lock==1'b1) ? {VO1_data[15:8], 2'b00 } : video_data[19:10];

assign pixel_o[9:0] = (gs2971_ch1_lock==1'b1) ? {VO1_data[7:0] , 2'b00 } : video_data[9:0];

问题描述

问题:笔者使用此种模型进行了约束,还是有大量的路径违例,不明白原因。

create_clock -name gs2972_pclk -period 6.73 [get_ports gs2972_ch1_pclk_o]

set_output_delay -clock gs2972_pclk -max 1.3 [get_ports gs2972_ch1_data_o[*]]

set_output_delay -clock gs2972_pclk -min -0.8 [get_ports gs2972_ch1_data_o[*]]

某网友提出clk mux的两个输入端必须设置物理独立。如下,设置后依然存在功能错误。

create_clock -period 6.730 -name gs2972_pclk [get_ports gs2972_ch1_pclk_o]

set_output_delay -clock gs2972_pclk -max 1.300 [get_ports {

gs2972_ch1_data_o[*]}]

set_output_delay -clock gs2972_pclk -min -0.800 [get_ports {

gs2972_ch1_data_o[*]}]

set_clock_groups -name CLKA -logically_exclusive -group [get_clocks -regexp .*gs2972.*] -group [get_clocks -regexp .*clk_out2.*]

非时序约束解决方案

第一种方法:对输出时钟进行取反。

assign pclk = (gs2971_ch1_lock==1'b1) ? VO1_clk : ~video_pclk;

assign pixel_o[19:10] = (gs2971_ch1_lock==1'b1) ? {VO1_data[15:8], 2'b00 } : video_data[19:10];

assign pixel_o[9:0] = (gs2971_ch1_lock==1'b1) ? {VO1_data[7:0] , 2'b00 } : video_data[9:0];

第二种方法:生成两路同频不同相时钟,一路用于产生数据,一路移相时钟给外部器件,调整相位,直到能正确显示为止。

assign pclk = (gs2971_ch1_lock==1'b1) ? VO1_clk : clk_180;

assign pixel_o[19:10] = (gs2971_ch1_lock==1'b1) ? {VO1_data[15:8], 2'b00 } : video_data[19:10];

assign pixel_o[9:0] = (gs2971_ch1_lock==1'b1) ? {VO1_data[7:0] , 2'b00 } : video_data[9:0];

哪位大神能通过时序约束的方式解决次问题?