1.主时钟约束

主时钟通常是FPGA器件外部的板机时钟或FPGA的高速收发器输出数据的同步恢复时钟信号等。下面这句语法大家一定不会陌生。该语句用于对主时钟的名称、周期、占空比以及对应物理引脚进行约束。

create_clock -name <clock_name> -periood <period> -waveform {

<rise_time> <fall_time>} [get_ports <port_name>]

在设计中,未约束的时钟可以通过时钟网络报告和时钟确认报告查看。在打开综合和实现设计后,输入如下指令:

report_clock_networks

check_timing

对于将高速传输器(gt)的输出时钟网络作为主时钟约束,命令如下:

creat_clock -name rxclk -period 6.667 [get_nets gt0/RXOUTCLK]

对于一些硬件原语的输出时钟引脚,若与其输入时钟之间没有很强的因果关联性,也可以将这个硬件原语的输出引脚作为时钟源进行主时钟约束。

对于差分时钟,只需要对差分缓冲器的输入正端(sys_clk_p)进行主时钟约束即可。若同时对正负端进行约束,会导致不真实的CDC(clock domain crossing)路径产生。

对于MMCM和PLL,系统会自动生成相应的约束文件,不需要手动约束。

在一些时序路径中,如一些引脚上的数据信号,其同步时钟只存在于外部芯片,并不存在于FPGA器件内。这种情况下,为了时序分析的需要也必须定义一个时钟用于描述时序数据引脚的外部时钟信号,这个时钟就是虚拟时钟。虚拟时钟的约束不需要引脚。

create_clock -name clk_virt -period 10

2.时钟特性约束

对于时钟抖动的约束有以下两条 ,其中set_input_jitter只能约束主时钟,set_system_jitter对系统抖动进行定义。

set_input_jitter [get_clocks <clock_name>] <jitter_in_ns>

set_system_jitter <clock_name> <jitter_in_ns>

除时钟抖动以为的所有可能影响时钟周期性偏差的因素,都可以使用set_clock_uncertainty命令进行约束定义。也称用户不确定性。

set_clock_uncertainty -<setup/hold/空出来表示两者都有> -from [get_clocks <clock0_name>] -to [get_clocks <clock1_name>] <uncertainty_value>

对于时钟延时约束,有以下命令:

set_clock_latency [-clock <args>] [-rise] [-fall] [-min/max/空出来表示两者都有] [-source] <latency> <objects>

3.衍生时钟约束

衍生时钟主要是指由已有的主时钟进行分频、倍频或者相移而产生出来的时钟信号,如由MMCM或一些设计逻辑所驱动产生的时钟信号。一般Vivado的时序工具能够自动产生正确的衍生时钟,若设计者认为自动产生的衍生时钟有误,也可以手动进行衍生时钟的约束。

create_generated_clock -name <generated_clock_name> -source <master_clock_source_pin_or_port> -multiply_by <mult_factor>\

-divide_by <div_factor> <pin_or_port>

4.IO接口约束

IO接口的时序约束主要包括set_input_delay和set_output_delay,输入输出约束差不多,主要约束如下:

set_input_delay -clock<args> -reference_pin<args> -clock_fall -rise -max -add_delay <delay> <objects>

#下面对命令进行解释

-clock 用于指定约束引脚的同步时钟(源时钟),其后的<args>即需要指定的同步时钟名称,这个时钟可以是设计中事先定义的主时钟或虚拟时钟。

-reference_pin 用于指定延时值<delay>的参考时钟,其后的<args>即需要指定的参考时钟名称。该项是可选项,不指定该选项,则指定延时值的参考时钟就是-clock指定的同步时钟。

-clock_fall 指定输入延时约束取值相对于同步时钟的下降沿。若不指定,默认为-clock_rise

-rise 指定约束信号相对时钟的边沿关系是上升沿,也可以用-fall指定为下降沿

-max 设定最大延时值,也可以是-min最小值。若不指定,则是最大最小值都包括

-add_delay 用于多组参考组合的输入引脚约束

<delay> 设定延时值

<objects> 指定约束的目标输入引脚名称

关于输入延时的计算如下:

set_input_delay(max)= -Tc2j_pcb(min) + Tco(max) + Td_pcb(max)

set_input_delay(min)= -Tc2j_pcb(min) + Tco(max) + Td_pcb(min)

其中c2j_pcb代表时钟源在pcb上的走线延时,d_pcb为数据在pcb上的走线延时,co为外部芯片数据引脚输出数据所经过的延时,查芯片手册可以获得。

set_output_delay(max)= Td_pcb(max) - Tc2j_pcb(min) + Tsu

set_output_delay(min)= Td_pcb(min) - Tc2j_pcb(min) - Th

5.时钟例外约束

进行时序例外约束的原因:时序分析工具默认的时序检查方式可能与工程实现的实际情况不符合(通常是约束过紧,可能导致时序失败)。因此,设计者需要额外增加一些约束命令,用于调整既有的时序检查方式,以保证时序工具的时序检查与实际情况一致。

进行时序例外约束的典型例子:1.异步时钟域路径,通常可以使用时钟分组约束或虚假路径约束以及多周期约束。2.某些逻辑的时序单元并非每个时钟周期都及进行数据采样传输,此时可以使用多周期约束,适当放宽这些路径的约束 。3.有时设计中希望对时序路径施加更紧的约束,以获得更大的时序余量,此时可以使用最大/最小延时约束。4.某些组合路径是静态的(赋值不变)或不需要进行时序约束,此时可以使用虚假路径约束忽略这些路径。

5.1多周期约束

多周期约束语法如下:

set_multicycle_path <path_multiplier> -setup/hold -start/end -from <startpoints> -to <endpoints> -through <pins/cells/nets>

#

-start和-end用于指定约束命令的周期参数是以源时钟还是以目标时钟作为参考时钟。

对于源时钟和目标时钟同频同相的时序路径分析,是否使用-start和-end是没有头差异的。

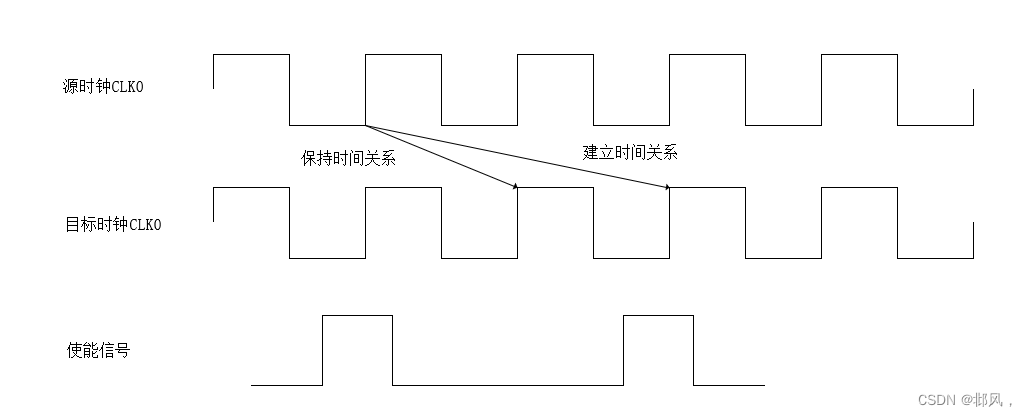

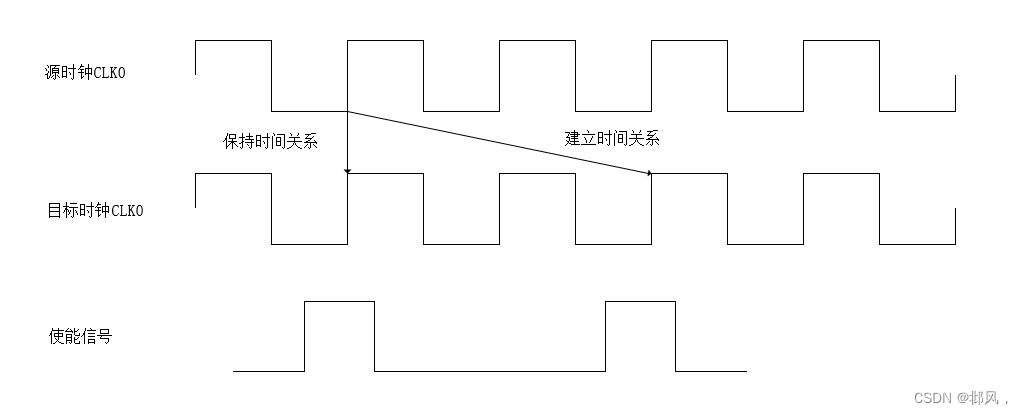

保持时间的时钟周期数=建立时间的<path_multiplier>参数-1-保持时间的<path_multiplier>参数。在一般情况下,若只对setup进行set_multicycle_path约束,则保持时间的<path_multiplier>参数默认为0,也就是保持时间的时钟周期数默认和建立时间的<path_multiplier>参数相差一个时钟周期。那么仅对setup进行约束,则建立时间和保持时间关系同时向右移动<path_multiplier>参数-1个时钟周期,若加上对hold的<path_multiplier>参数约束,则保持时间关系会向左移动hold的<path_multiplier>参数个时钟周期,从而达到多周期约束的效果。

下面给出示意图。

当约束仅为set_multicycle_path 2 -setup -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]时,图形如下:

当约束为set_multicycle_path 2 -setup -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]和set_multicycle_path 1 -hold -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]时,图形如下:

当约束为set_multicycle_path 2 -setup -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]和set_multicycle_path 1 -hold -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]时,图形如下:

对于同频异相的时钟,在默认情况下时序工具会寻找与clk1相邻最近的clk2时钟上升沿,并以clk1和clk2相对时间最短(时序要求最高,即最坏情况)的一组时钟沿的时序路径进行分析。此时,使用如下约束命令进行调整:

对于同频异相的时钟,在默认情况下时序工具会寻找与clk1相邻最近的clk2时钟上升沿,并以clk1和clk2相对时间最短(时序要求最高,即最坏情况)的一组时钟沿的时序路径进行分析。此时,使用如下约束命令进行调整:

set_multicycle_path 2 -setup -from [get_clocks CLK1] -to [get_clocks CLK2]

对于慢时钟域到快时钟域或者快时钟域到慢时钟域有异曲同工之妙,需要注意的是-start和-end的确认,下面给出这两种情况的通用约束方法。

#慢-快

set_multicycle_path N -setup -end -from [get_clocks CLK1] -to [get_clocks CLK2]

set_multicycle_path N-1 -hold -end -from [get_clocks CLK1] -to [get_clocks CLK2]

#快-慢

set_multicycle_path N -setup -start -from [get_clocks CLK1] -to [get_clocks CLK2]

set_multicycle_path N-1 -hold -start -from [get_clocks CLK1] -to [get_clocks CLK2]

5.2虚假路径约束

所谓虚假路径,是指该路径是设计中的非功能路径或没有任何时序要求的路径。做虚假路径约束的原因:可以减少编译时间,同时腾出有限的布局布线资源,用于提升整体的时序性能。常见的虚假路径包括:1.已经做过同步处理的跨时钟域路径。2.上电后只做一次初始化写入寄存器路径。3.复位或测试逻辑路径。4.某些实际并不存在的时序路径。例如,设计中的两个异步是哦只能怪域之间的数据通信已经使用双寄存器锁存等方式进行同步了,就可以使用虚假路径约束关闭这两个时钟之间的数据路径检查。约束的基本语法如下:

set_false_path -setup/hold -from <node_list> -to <node_list> -through <node_list>

#对于两个或多个相斥时钟做约束推荐用法

set_clock_groups -group CLKA -group CLKB

5.3最大/最小延时约束

最大延时约束将覆盖默认的建立时间分析的最大路径延时值。最小延时约束将覆盖默认的保持时间分析的最小路径延时值。基本约束语法如下:

set_max_delay <delay> -datapath_only -from <node_list> -to <node_list> -through <node_list>

set_min_delay <delay> -from <node_list> -to <node_list> -through <node_list>

其中,-datapath_only只能用于含有-from选项的set_max_delay约束命令中。该选项会将时钟偏斜考虑移除,同时会将约束路径的保持时间检查设置为false路径,相当于同时对此路径自动生成了set_false_path -hold约束。也就是说,若对同一路径进行set_min_delay约束,将会被忽略。