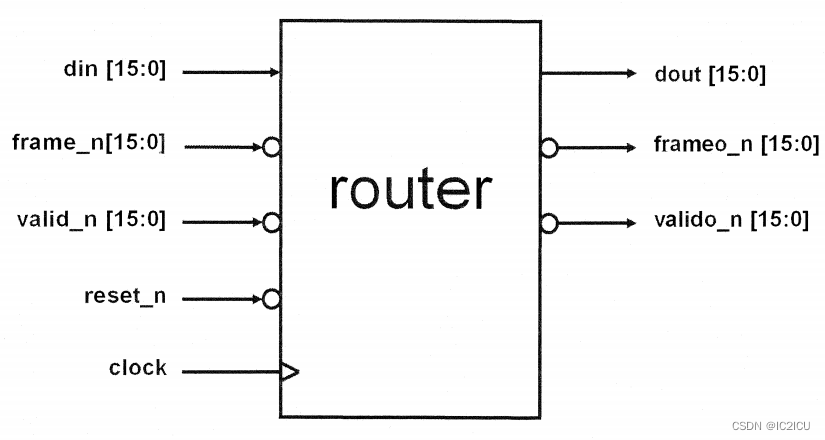

实验一主要是对接口以及其实例化有几个任务。

任务一:为这些信号端口创建接口,并且为其定义时钟块,始终块要求在时钟的上升沿驱动,并且添加测试的program和DUT之间的端口连接,要求所有的方向都是相对于test program,此外还要再接口中使用modport,表明reset_n为输出。

interface router_io(input bit clk);

//创建接口,没有指明方向

logic reset_n ,

logic [15:0] din ,

logic [15:0] frame_n ,

logic [15:0] valid_n ,

logic [15:0] dout ,

logic [15:0] frameo_n ,

logic [15:0] valido_n ,

logic [15:0] busy_n ;

//创建时钟块

//相对于testprogram,再testgram中,router的输入就是我们

//的激励输出,而router的输出就是我们的输入,此时要验证

//功能是否正确

clocking cb @(posedge clk);

default input #1ns output #1ns;

output reset_n;

output din;

output frame_n;

output valid_n;

input dout;

input valido_n;

input frameo_n;

input busy_n;

endclocking:cb

//声明modport

modport TB(clocking cb, output reset_n);

endinterface

任务二:1,声明一个program块,连接在接口中声明的modport TB。2,在Initial语句块中,向屏幕上打印一条简单的信息。

//声明program块

program automatic test(router_io.TB rtr_io);

initial begin

//打印信息

$display("This is lab1");

reset();

end

//写复位任务,即一些初始化工作

task reset();

rtr_io.reset_n = 1'b0;

rtr_io.cb.frame_n <= '1;

rtr_io.cb.valid_n <= '1;

##2 rtr_io.cb.reset_n <= 1'b1;

repeat(15) @(rtr_io.cb);

endtask: reset

endprogram:test

任务三:将test program和DUT通过inteface连接起来

`timescale 1ns/100ps

module router_test_top;

parameter simulation_cycle = 100;

bit SystemClock;

//添加接口实例

router_io top_io(SystemClock);

//实例化test program

//通过接口实现IO连接

test t(top_io);

//实例化dut

//端口名可以由interface_name.signal_name来表示

router dut(

.reset_n (top_io.reset_n),

.clock (top_io.clock),

.din (top_io.din),

.frame_n (top_io.frame_n),

.valid_n (top_io.valid_n),

.dout (top_io.dout),

.valido_n (top_io.valido_n),

.busy_n (top_io.busy_n),

.frameo_n (top_io.frameo_n)

);

//初始化语句块

initial begin

//添加时间格式

$timeformat(-9, 1, "ns", 10);

SystemClock = 0;

forever begin

#(simulation_cycle/2)

SystemClock = ~SystemClock; //时钟信号产生

end

end

endmodule