最近几个月项目比较多,比较急,所以没时间更新,今天更新一点前段时间做项目过程中最基本的芯片测试项-------OS、Leakage测试

OS:在集成电路制造过程中,会有相应比例制造缺陷导致DUT本身电路开短路,这部分产品已有OS缺陷,芯片已经不能正常工作了。在实际的生产测试中,产品成本与测试时间成正比,所以OS测试是芯片测试中第一位测试的,测试fail直接换下颗。

下图是集成电路设计中芯片的保护电路,通常为了保护输入输出引脚,使其避免受到静电放电或其他过压情况导致的损坏,会在引脚与地之间加入一个保护二极管,这些二极管在电路正常工作时是反向截止的,不会对电路正常工作有任何影响。

测量时,首先把所有引脚接地,包括电源引脚。接下来把被测引脚接到测试机上,测试机施加一个很小的电流,这个电流会使得其中一个保护二极管正向导通,通过测试这个导通压降,就可以判断被测引脚的开短路状态,根据欧姆定律:U=I*R

当被测引脚短路时,R趋近于0,测得电压趋近于0;而当被测引脚开路时,电阻R相当于无穷大,测得电压会很大,所以做测试时,需要对最大电压做钳位限制,以防止输出电压过大,损坏测试机和被测器件。一般来说,硅衬底的二极管压降0.6-0.7V,锗二极管导通压降大约0.4V,所以一般我们设置电压绝对值得上下限分别为1.5和0.2,当测量电压绝对值超过1.5时,被测引脚判定为开路;当测量电压绝对值小于0.2时,被测引脚被判为短路。而钳位电压的设置绝对值要大于limit,否则会因为电压被钳制而造成虚假通过。下表举个例子说明pass/fail的情况。

| 测试引脚 | 驱动电流/档位 | 电压测量结果/量程 | 最小值 | 最大值 | 测试结果 |

| Pin1 | -0.100mA/2mA | -641mV/8V | -1.5V | -200mV | Pass |

| Pin2 | -0.100mA/2mA | -3V/8V | -1.5V | -200mV | Fail |

| Pin3 | -0.100mA/2mA | -4mV/8V | -1.5V | -200mV | Fail |

Leakage:理想情况下,集成电路的输入引脚或具有三态输出的引脚对电源和地的电阻非常大,当对这些引脚施加电压时,只会有很小的电流流入或流出这些引脚。这些电流称为漏电流-Leakage。

随着工艺的进步,器件内部和引脚间的绝缘氧化膜越来越薄,导致漏电发生的概率更大。另外,制造过程中的工艺缺陷导致的桥接、异物或封装过程中造成的芯片划伤,裂痕都会造成IC的漏电流偏大。有部分产品可能会表现漏电流偏大但功能正常,但是这类产品却有潜在的可靠性问题。

针对数字电路,有相应的输入低电平漏电流IIL和输入高电平漏电流IIH测试,测试过程如下:

1)对电源引脚施加手册中定义的电源最大电压VDDmax,这是漏电流测试中最严苛的条件。

2)除被测引脚外,对其他引脚施加高电平VIH=VDDmax。

3)被测引脚用PMU施加VIL(0V),此时测得电流为IIL。

使用相同的方法,当其他引脚施加低电平,被测引脚施加高电平时测到的电流为IIH。

在射频芯片中,客户通常会给相应的TestPlan来标明测试条件,通常情况下,只会测试的pin脚电压,其他都为0,然后测试其leakage,下图是某芯片测试leakage的TestPlan,我们只需要按照要求给指定的PIN脚电压,然后设定正确的参数就能进行leakage测试。

所以在射频芯片上,通常也就是测IIH。

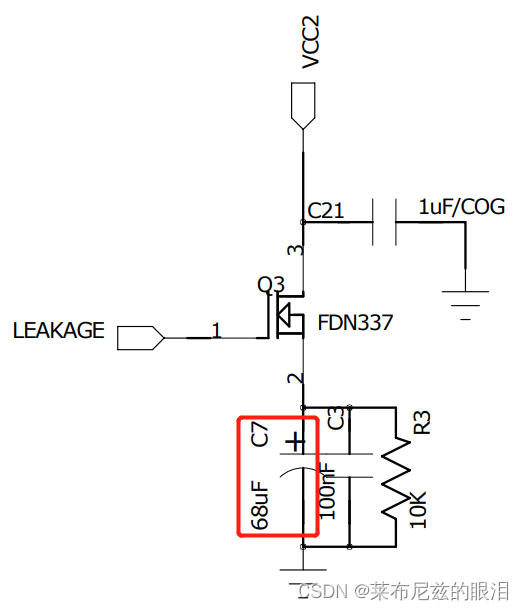

在参数设定上,由于在发射频信号时,电源引脚需要提供一个较大的电流,此时仅靠电源pin又不能及时提供大电流出来,那么就需要在电源pin下挂一个大电容,在发射频信号的时候电容瞬间放电,以提供一个大电流能够支撑射频信号发送出去。电源电路如下图所示。

在设置leakage测试参数的时候测试时间也需要长一点,因为电容放电是需要一段时间的,最好能够抓出电流变化曲线来看测试时间设置多久合适。

以上就是近期在做项目过程中测试的两个最基本的测试项,后续我会首先更新我们使用的自动化测试软件以及使用方法,然后再继续介绍Wifi、PA等测试项测试方法及心得。