存储系统

存储器映射

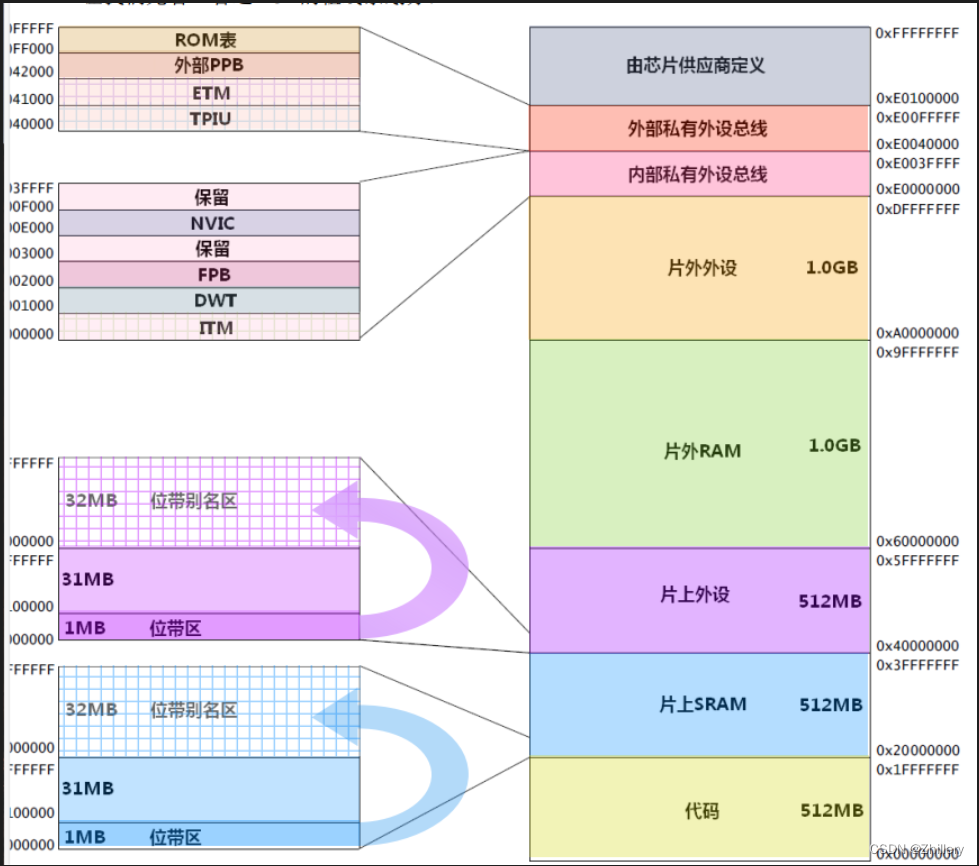

CM3 预定义存储器映射简图(CM3 的地址空间是 4GB )

片上 SRAM:大小 512MB,拥有 1MB 位带区,32MB 位带别名区;而位带别名区里面的每个字对应位带区的一个比特

片上外设:定义个片上 SRAM 几乎一致,但不可以执行命令

片外外设、片外 RAM:各占 1GB 用于连接外部,但片外外设区同样不可执行命令

总结:外设区不可以执行命令,而 RAM 区均可执行命令

最后的 512MB 分配给 CM3 的系统级组件,内部私有外设总线 s,外部私有外设总线 s,以及由提供者定义的系统外设

私有外设总线有两条

- AHB 私有外设总线,只用于 CM3 内部的 AHB 外设,它们是:NVIC, FPB, DWT 和 ITM

- APB 私有外设总线,既用于 CM3 内部的 APB 设备,也用于外部设备

NVIC 所处的区域叫做“系统控制空间(SCS)”

存储器各种访问属性

CM3 为存储器的访问设置了 4 个属性

- 可否缓冲(Bufferable)

- 可否缓存(Cacheable)

- 可否执行(Executable)

- 可否共享(Sharable)

CM3 片上默认无配备缓存,而可以使用外设缓存,此时就需要引入缓存设置来进行管理

存储器的缺省访问许可

CM3 在未开启 MPU(存储保护单元)时,缺省访问许可才能生效

如果启用了 MPU,则会在地址空间划分多个区,为不同区设置不同访问权限

位带操作

位带操作(Bit Banding)是一种在嵌入式系统中进行位级操作的技术。它通过将特定的位与内存地址进行映射,以实现对单个位的原子操作。

那片上 SRAM 作为介绍,它拥有一个 1MB 位带区,以及一个 32MB 位带别名区,下面时对应位带操作流程:

- 位带别名区将单个比特膨胀为 32 位的字

- 通过访问这些字,从而达到访问原始比特的目的

一般而言,位带操作包含:读、改、写三步,而这三步之间夹杂着两个极短的切换空挡,若多个进程并发执行位带操作,可能会导致紊乱现象(即冲突)

而 CM3 位带操作改进了这一缺点,使三步变成了一个原子操作,完美解决了

C 编译器不支持位带操作,故需要使用 define 定义

使用 define 定义一个位带别名区地址:#define DEVICE_REG0 ((volatile unsigned long *) (0x40000000))

非对齐数据传输

最低有效位(LSB):即二进制数中最右边的一位数字;

最高有效位(MSB):即二进制数中最左边的一位数字;

在 CM3 构架下,非对齐的数据传送只发生在常规的数据传送指令中,如 LDR/LDRH/LDRSH

互斥访问

CM3 使用互斥访问技术取代了传统 ARM 中的 SWP 指令

在互斥访问操作下,允许互斥体所在的地址被其它总线 master 访问,也允许被其它运行在本机上的任务访问,而 CM3 能够“驳回”有可能导致竞态条件的互斥写操作

互斥访问的读写操作对应的指令为

LDREX/STREX, LDREXH/STREXH,

LDREXB/STREXB

在使用互斥访问时,LDREX/STREX 必须成对使用

严格的驳回规定(目前大多数情况下选择):

- 当执行一条 LDREX 指令后,下一条立马跟着就是 STREX,那么他将会被执行

- 如果第一条 LDREX 指令后又跟着其他的 STR 指令或者某些中断,那么接在这些代码之后的 STREX 就会被驳回!

LDREX/STREX 的工作原理:

- 执行 LDREX 后,在处理器内部标注一段地址,地址一般从 R0 开始

- 紧接着执行 STREX,若其存储区地址落在标注地址内,那么就清除该标记

端模式

CM3 虽然同时支持小端模式和大端模式,但是推荐直接使用小端

CM3 使用的是“字节不变大端”

CM3 中,均在复位时确定使用哪种端模式,且运行时不得更改