SPI(Serial Peripheral Interface)是Motorola公司推出的一种同步串行接口技术,通过串行外围设备接口,能与外部设备之间进行全双工同步串行通信,其功能类似于51串行接口的方式0,有4个引脚:MISO,MOSI,SCK,CS.

基本概念

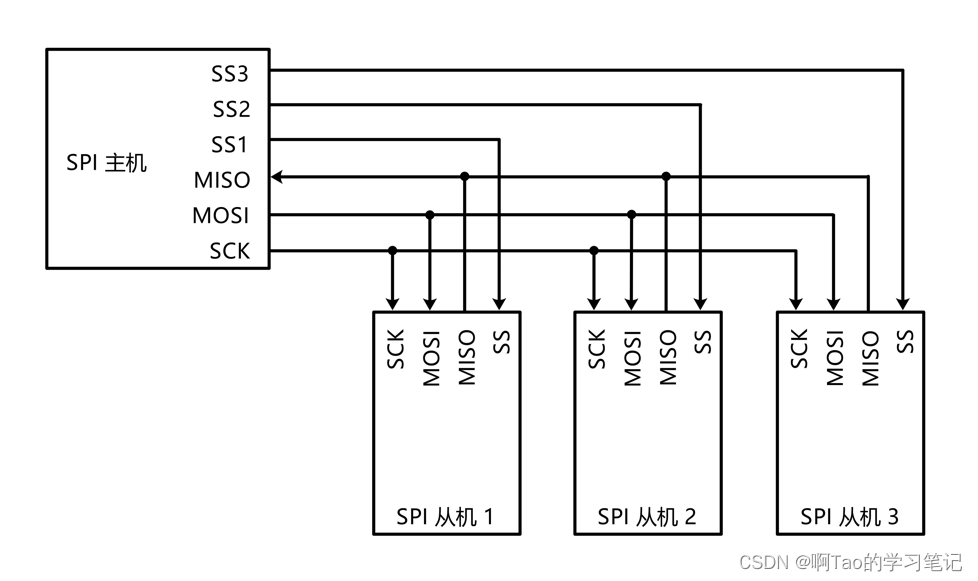

标准的SPI总线接口有4根通信线路,一条总线上也挂载多个SPI从设备(一主多从),是一种全双工同步通信总线。

MISO(Master Input Slave Output):主设备输入从设备输出,主设备读取从设备的数据,也有一些器件称之为SDI,就是串行数据输入的意思;

MOSI(Master Output Slave Input):主设备输出从设备输入,主设备向从设备发送数据,另一种称法是SDO,就是串行数据输出的意思;

SCK(Serial Clock):和IIC相同,无论是主设备还是从设备,所有数据的传输都是以这条线路上的时钟为同步,所以SPI和IIC都是属于同步串行接口;

SS(Slave Select):IIC可以通过寻址来找到总线上的指定设备,SPI则是用SS线来使能需要操作的设备,设备多的话,也可能使用多个IO口或者数据选择器、译码器之类。也有的器件称为CS。

支持SPI接口的设备有EEPROM,FLASH,RTC,AD转换器等。现在很多器件都是SPI的变种,三线SPI(MISO,MOSI复用)是一种半双工同步串行通信。

硬件接线时,所有SPI设备的SCK、MOSI、MISO分别连在一起,主机另外引出多条SS控制线,分别接到各从机的SS引脚,引脚配置方面输出引脚配置为推挽输出,输入引脚配置为浮空或上拉输入。由下图可以看出其接线方式。

SPI总线通信规则

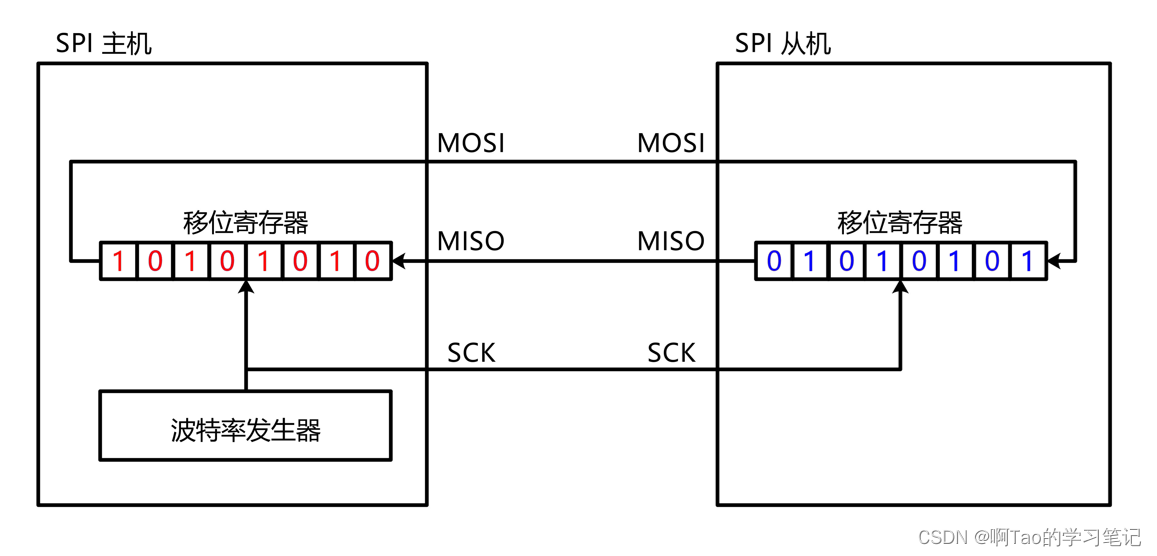

SPI数据传送

数据传输时主从设备的数据移位寄存器同时工作。 主机移位寄存器的最高位发送到从机移位寄存器的最低位,从机移位寄存器的最高位也送到主机移位寄存器的最低位,经过8次数据传输后,从机一个字节的数据被送到主机的移位寄存器中,主机一个字节的数据也被送到从机的移位寄存器中,两边的数据同时完成交换。所以SPI的收发是同步执行的,而IIC收发是异步执行的。

SPI的收发是同步的,而若是只要求主机接收或者发送时又该怎么办呢?

要求主机只接收时,那么主机的移位寄存器中放入一个不需要从机读取的数据即可(一般为0X00或0XFF),要求主机只发送时,那么对从机移入的数据不读即可。

如上图所示,主机和从机要交换数据,在一个时钟周期内,当时钟的第一个边沿发生时,主机和从机都将自己最高位的数据发到数据线(MOSI、MISO)上,对应上图就是主机将1放到MOSI,从机将0放到MISO上,时钟的第二个边沿发生时,主机和从机将数据线上的数据读出放到移位寄存器最低位。完成一个位的传输后这时主机移位寄存器的内容就变为0101010,从机移位寄存器数据为10101011.重复8次后就可完成一个字节的传输。

简单的来说,SPI的传输方式是数据高位先行,一个时钟周期内,第一个时钟边沿输出数据到信号线上,第二个时钟边沿采样数据,将数据送入移位寄存器最低位。

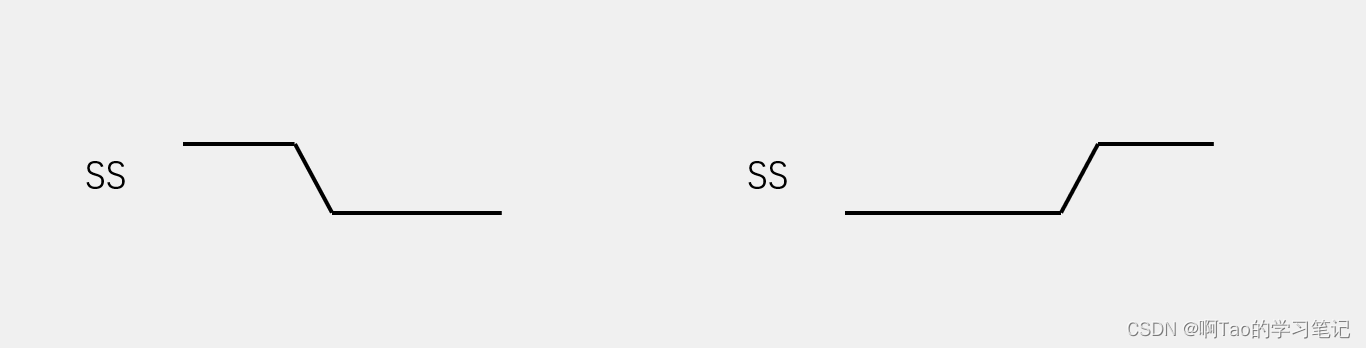

起始位和终止位

起始条件:SS从高电平切换到低电平

终止条件:SS从低电平切换到高电平

如图,左边是起始信号,右边是终止信号。

与IIC不同,SPI选中从设备即表示数据输出将开始,SPI的片选线是SS,SS为低电平有效即低电平时表示主机选中从机,高电平时未选中从机。

时钟信号的相位和极性

硬件SPI接口,主机侧需要对相关寄存器进行设置,其中 有两个重要的位,其配置不同,则通信的模式也不同。

CPOL(Clock Polarity):时钟极性选择位(时钟在高或低电平空闲)。

CPOL=0,表示空闲时时钟为低电平即SCK=0,有效状态为时钟高电平(SCK=1)

CPOL=1,表示空闲时时钟为高电平即SCK=1,有效状态为时钟低电平(SCK=0)

CPHA(Clock Phase):时钟相位选择位(数据在第一或第二个边缘采样(读取))。

CPHA=0,表示数据采样在第一个边沿(奇数边沿),数据传输在第二个边沿(偶数边沿)

CPHA=1,表示数据采样在第二个边沿(偶数边沿),数据传输在第一个边沿(奇数边沿)

不同的从设备可能在出厂的时候配置为某一种模式,这是不能改变的,通信双方必须是工作在同一模式下,所以需要主设备对SPI模式进行配置,通过CPOL和CPHA来控制主设备的通信模式。

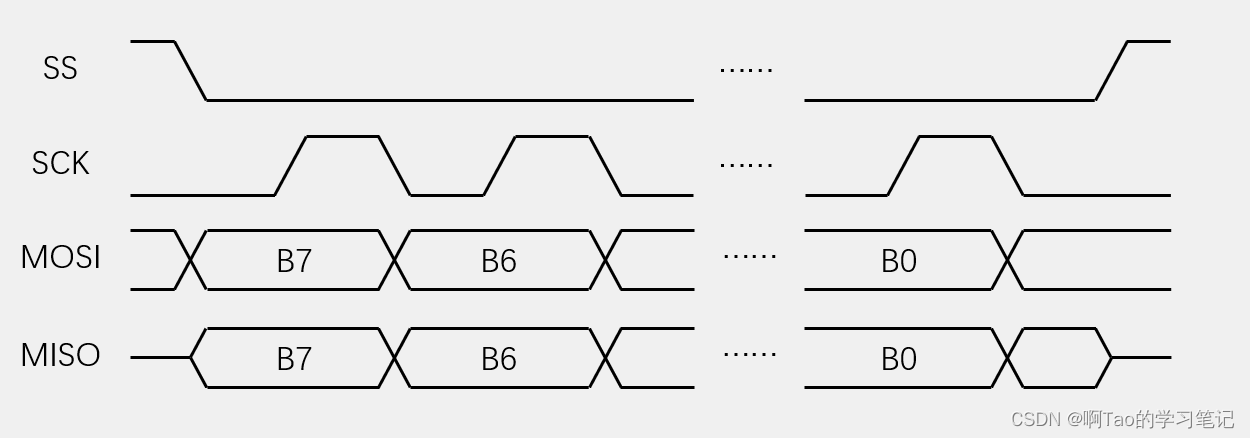

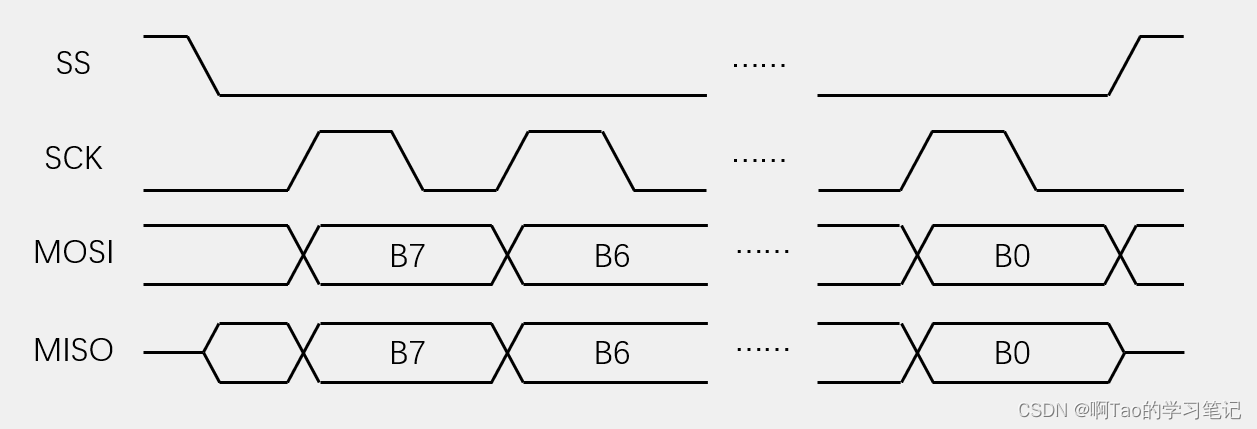

模式0(CPOL=0,CPHA=0)

CPOL=0:空闲状态时,SCK为低电平

CPHA=0:SCK第一个边沿移入数据,第二个边沿移出数据

该模式下为奇数边采样,偶数边输出

如上图所示为模式0的时序图。因为该模式下是时钟信号第一个边沿采样,所以在SS下降沿(启动信号)后需要立即将要发送的数据输出到数据线(MOSI、MISO)上,这样才能使第一个时钟边沿时主机和从机采样到信号,当到达第二个时钟边沿(偶数边),继续将第二个数据输出到数据线上,不断重复这个过程就可以实现一个字节或多个字节的传输。

由图可以看出SS下降沿后,MISO和MOSI立即变化,表名有数据输出到该数据线上,SCK上升沿时,主机和从机采样数据,此时数据线上的信号必须保持稳定,这样才能确保数据的有效性。下一个边沿发生时才继续将新的数据输出到数据线上。

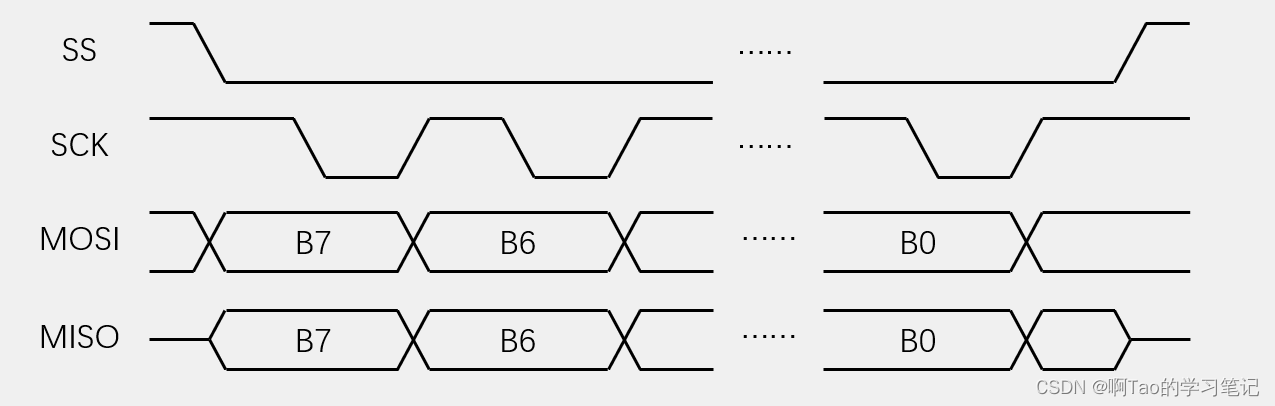

模式1(CPOL=0,CPHA=1)

CPOL=0:空闲状态时,SCK为低电平

CPHA=1:SCK第一个边沿移出数据,第二个边沿移入数据

该模式下为偶数边采样,奇数边输出

与模式0不同的是,该模式下为第二个边沿采样数据,所以在SS下降沿(启动信号)后不需要立即将数据输出到信号线上,而是在SCK第一个边沿(奇数边)的时候才将数据输出到数据线上,在SCK第二个边沿(偶数边)时采样数据。

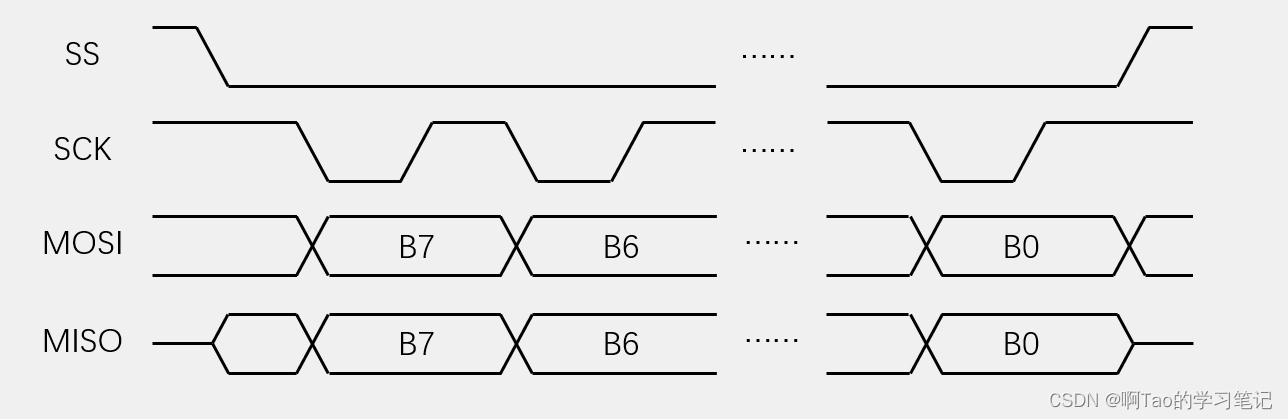

模式2(CPOL=1,CPHA=0)

CPOL=1:空闲状态时,SCK为高电平

CPHA=0:SCK第一个边沿移入数据,第二个边沿移出数据

该模式下为奇数边采样,偶数边输出

该模式与模式0相似,只不过SCK空闲时的电平为高电平,将模式0的SCK取反就可得到该模式,其输出和采样原理和模式0相同。

模式3(CPOL=1,CPHA=1)

CPOL=1:空闲状态时,SCK为高电平

CPHA=1:SCK第一个边沿移出数据,第二个边沿移入数据

该模式下为偶数边采样,奇数边输出

数据位有效性

数据在时钟线上升沿或下降沿被采集,采集时数据线(MISO,MOSI)信号必须保持稳定,其他时间可以变化。

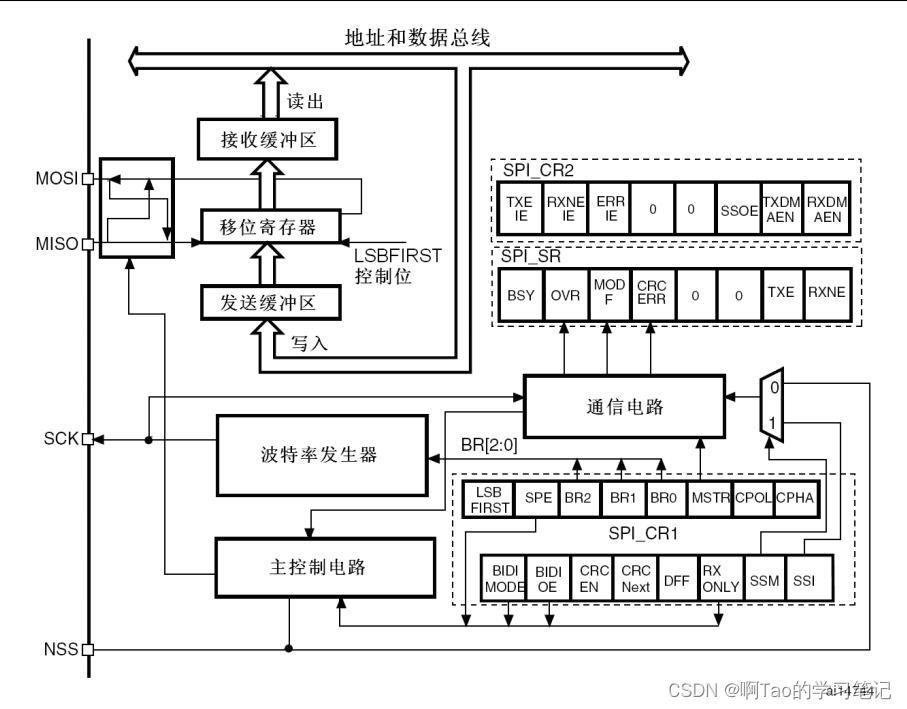

STM32 的SPI

STM32内部集成了硬件SPI收发电路,可以由硬件自动执行时钟生成、数据收发等功能,减轻CPU的负担。

上图为STM32的SPI结构框图,其可分为三个部分,一为数据的接收和发送,二为时钟输出,三为控制部分。

数据的接收和发送是框图中的左上部分,端口为MISO和MOSI,从图中数据箭头指示方向看出MISO数据移入的时候先移入的是移位寄存器的左边,这与我们之前说的SPI为高位先行正好相反,说明了STM32的SPI支持高位先行和低位先行,若要其变为高位先行则需要对LSBFIRST控制位进行相应的操作。MOSI和MISO之间有交叉线,这是用来做主从机模式选择的时候用的,若该STM32为主机则不需要交换MISO 和MOSI,而当该STM32作为从机时,需要交换这两个数据线。

硬件SPI传输数据

下图为STM32硬件SPI非连续传输发送,非连续传输用于传输速率要求不高的地方,大多数场景下非连续传输已经够用,所以本文只介绍非连续传输。

上图中SPI配置为模式3,数据传输为低位先行(高位先行原理相同)。

当开始信号发出后(SS下降沿图中未给出),SCK第一个边沿之前,TXE下降沿,发送缓冲区非空,表示有数据写入发送缓冲区,在图中可看出该TXE下降沿后发送缓冲区中内容变为0XF1,之后发送缓冲区数据送入数据移位寄存器,SCK第一个边沿时,数据1的b0位输出,数据传输开始。

TXE=1发送数据缓冲区为空,此时虽然发送数据缓冲区为空,当并没有将新的数据放入其中,而是等待当前一个字节的数据发送完成后,再放入新数据。从图中可以看出数据1的b7位传输完成后,当SCK下一个边沿之前TXE出现下降沿,重复发送第一个数据的时序。

总结

SPI总线由SCK,MISO,MOSI,SS四线构成,是一种全双工同步通信总线。主机和从机都有一个串行移位寄存器,主机通过自己的串行移位寄存器写一个字节来发起传输。根据极性和相位的不同有4种工作模式,数据传输期间数据线根据极性和相位的设置在时钟线SCL在不同的边沿输出或采样数据。