此系列博客,仅对Xilinx平台PS端(ARM部分)开发做介绍,不对PL(FPGA)做过多介绍。

目录

1.2 Configuration Security Unit

一. MPSoc启动单元

1.1 Platform Managerment Unit

PMU 处理单元主要完成电源管理,系统启动初始化,复位和唤醒等

PMU Processor是一个Microblaze(FPGA的软核)

1.2 Configuration Security Unit

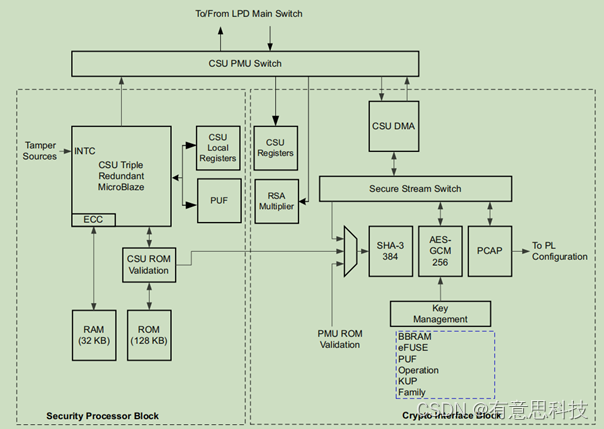

CSU由两个Block组成,分别是Security Processor Block负责启动等操作,和Cryto Interface Block负责加密等操作。

二. 详细启动流程

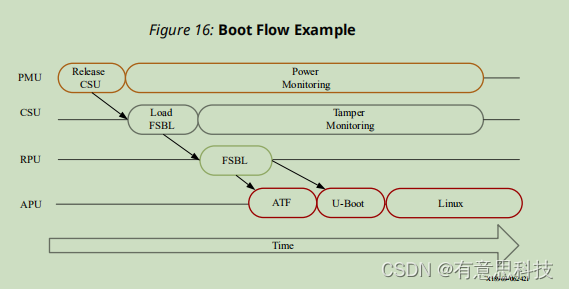

Xilinx MPSoc的启动流程分为三个阶段,预配置阶段,配置阶段和后配置阶段。

注:FSBL可在APU或RPU运行

2.1 预配置阶段

预配置阶段CSU尚未启动,由PMU完全控制,但是执行的是PUM ROM里面代码,ROM里面的代码是固化的,用户无法修改,所以我们无法干预这一阶段的任何行为。

PMU处理所有复位和唤醒过程。上电复位用于复位CSU和PMU,因为它们负责调试,系统和软件复位。

初次启动期间将执行下列步骤:

• 通过上电复位 (POR) 将 PMU 从复位状态唤醒。

• PMU 执行来自 PMU ROM 的代码。

• PMU 初始化 SYSMON 和启动所需的 PLL、清空低功耗域和全功耗域, 并释放 CSU 复位。

这阶段结束的标志是CSU复位的释放。

注:MBIST: 存储器内建自测试

MicroBlaze: 软核处理器,FPGA中的一个软核

2.2 配置阶段

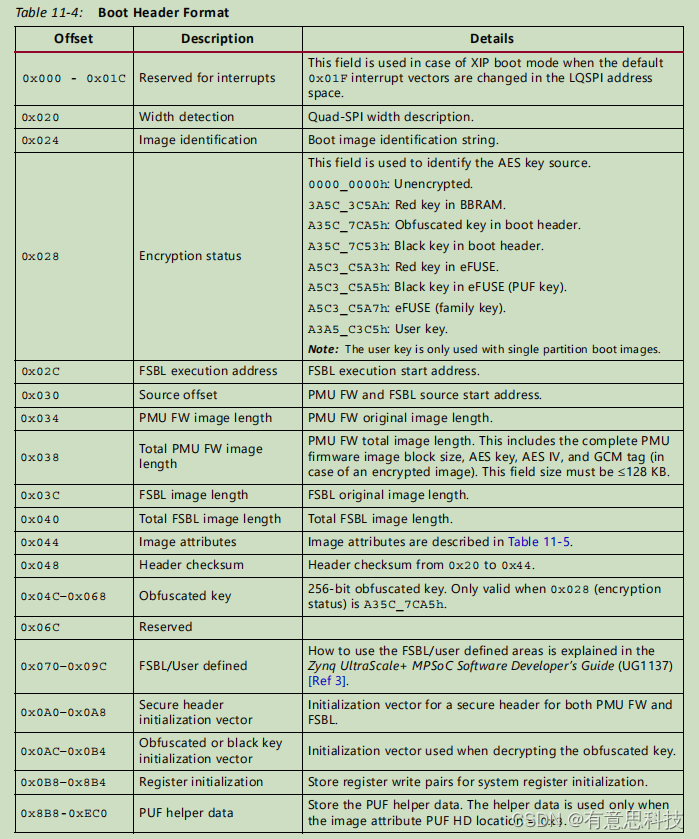

在配置阶段CSU开始工作,BootROM(CSU ROM代码的一部分)解释boot header以配置系统,初始化OCM,并将PS的FSBL(first-stage boot loader)代码加载到256KB片内RAM(on-chip RAM, OCM)中(无论是在安全还是非安全启动模式)。

系统根据BOOT Header的内容选择在CPU(Cortex-A53)还是RPU(Cortex-R5)上执行。负责初始化必要的时钟、内存和外设,加载Bit文件和用户代码等。

读取Mode Pin引脚,选择不同的启动方式。

在boot过程中,CSU还将PMU用户固件(PMU Firmware)加载到PMU RAM中,以与PMU ROM一起提供平台管理服务。PMU的Firmware不是必须的,但是大多数基于Xilinx的FSBL和系统软件的系统都存在PMU Firmware。

这个阶段FBSL可以通过PCAP接口从PS配置PL,但是这只是一个可选的操作。因为其实我们也可以在PS端的操作系统启动之后再动态配置PL端。有时,可能只需要 FSBL 在启动过程中加载部分 PL。随后,有必要在系统生命周期里继续对 PL 进行部分重配置。

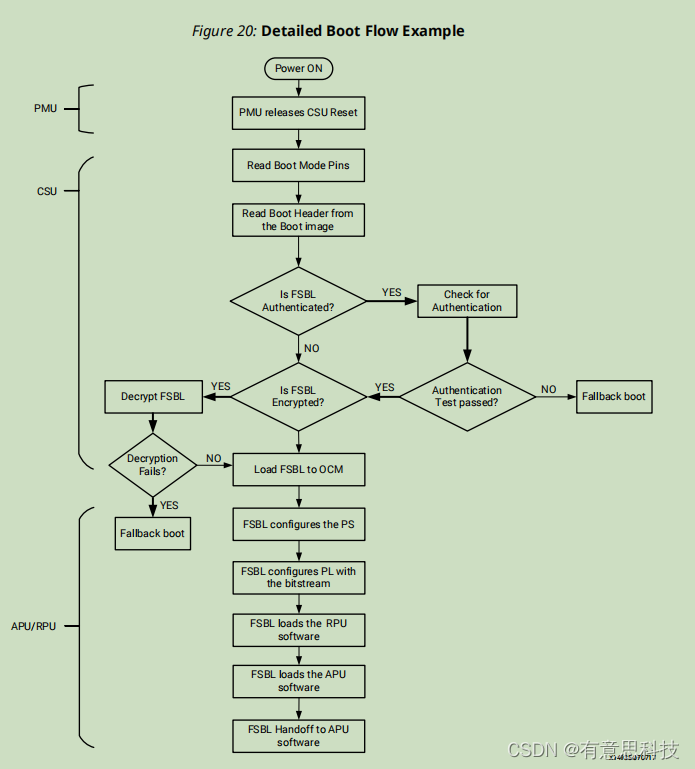

在 PMU 释放 CSU 后, CSU 将执行以下操作:

• 检查并判定 FSBL 或用户应用是否需要进行身份验证。

• 执行身份验证检查, 并且只有在身份验证检查通过以后才继续执行。然后, 检查镜像是否包含任何已加密的分区。

• 如果 CSU 检测到分区已加密, 那么 CSU 会执行解密并初始化 OCM、判定启动模式设置、执行 FSBL 加载和可选PMU 固件加载操作。

• 执行 CSU ROM 代码后, 它会将控制权交给 FSBL。 FSBL 使用 PCAP 接口来对含比特流的 PL 进行编程。

随后,在后配置阶段 FSBL 会负责对系统进行操作。

2.3 后配置阶段

开始执行FSBL之后,CSU ROM代码进入后配置阶段,该阶段负责系统干预响应。 CSU硬件提供持续的硬件支持,以验证文件,通过PCAP配置PL,存储和管理安全密钥以及解密文件。

FSBL主要会完成初始化系统,处理器,DDR,启动设备的初始化,固件加载,分区头文件验证,固件拷贝等工作。

这个阶段会启动SSBL,就是Linux的bootloader,开始引导启动Linux系统,或者直接进入RPU的应用程序。

注意:FSBL大小最好在170KB以下