示例:

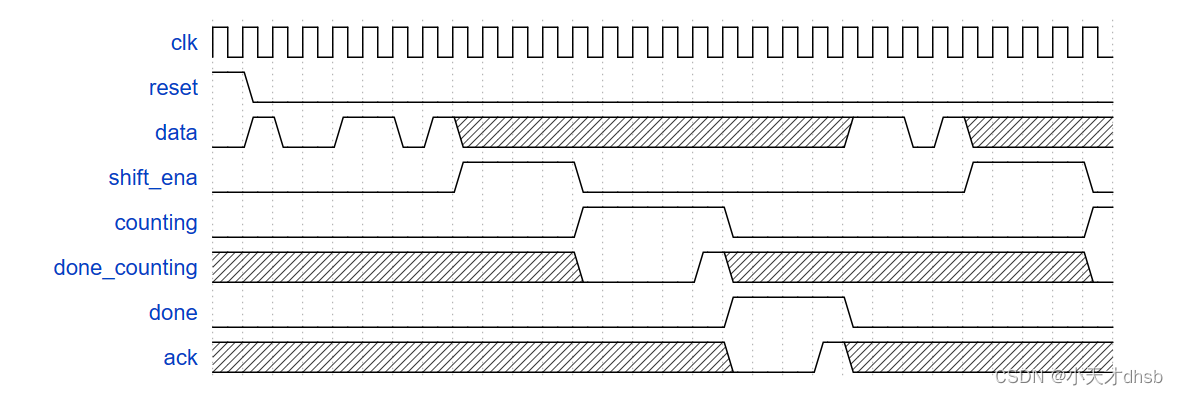

题目的主要意思是:复位之后寻找1101序列,找到之后shift ena在四个周期内为1,此后输出counting,如果done-counting=0,则counting一直为1,直到done-counting=1,counting才为0;

同理在done-counting为1后done一直为1,直到ack为1。也就是说done-counting结束了counting,启动了done。ack=1后回到第一个状态

module top_module (

input clk,

input reset, // Synchronous reset

input data,

output shift_ena,

output counting,

input done_counting,

output done,

input ack );

parameter b1=0,b2=1,b3=2,b4=3,s1=4,s2=5,s3=6,s4=7,cou=8,aacckk=9;

reg [3:0] state ,next_state;

//b1~b4:1101

//s1~s4: 保持shift_ena=1

//cou: 输出counting=1,等待done_counting输入

//aacckk;输出done=1,等待ack输入

always@(*)

begin

case(state)

b1:

next_state<=data?b2:b1;

b2:

next_state<=data?b3:b1;

b3:

next_state<=data?b3:b4;

b4:

next_state<=data?s1:b1;

s1:

next_state<=s2;

s2:

next_state<=s3;

s3:

next_state<=s4;

s4:

next_state<=cou;

cou:

next_state<=done_counting?aacckk:cou;

aacckk:

next_state<=ack?b1:aacckk;

endcase

end

always@(posedge clk)

begin

if(reset)

state<=b1;

else

state<=next_state;

end

assign shift_ena=(state==s1||state==s2||state==s3||state==s4);

assign counting=state==cou;

assign done=state==aacckk;

endmodule