电磁兼容EMC整改专题

目录

EMC整改流程及常见问题

首先我们来从EMC测试项目构成说起,EMC主要包含两大项:EMI(干扰)和EMS(抗干扰和敏感度)。这两大项中又包括许多小项目,如下图:

1EMC整改意见

1.首先需要双方的沟通相关信息,如验收的标准、摸底的报告、PCB图等信息;为什么要确定这么多信息呢?举例标准方面在车载行业,如五等级跟二等级那差距就大了去了。在提供相关资料和沟通后,我们会给出初步的整改建议,定位好EMC整改计划。

2.定位手段,对于这里小编觉得主要可以分为两点。

第一:经验判断,根据双方沟通情况,根据工程师的经验结合数据及测试情况来进行判断。

第二:比较测试,根据再次测试仪器所提供的数据来进行分析问题。

2EMC整改流程

1.RE超标整改流程

2.电源电缆导致辐射超标定位子流程:

3.信号电缆导致辐射超标定位子流程:

4.屏蔽体泄漏整改流程:

3EMC整改的一些小建议

1.电容的滤波作用

即频率f越大,电容的阻抗Z越小。当低频时,电容C由于阻抗Z比较大,有用信号可以顺利通过;当高频时,电容C由于阻抗Z已经很小了,相当于把高频噪声短路到GND上去了。

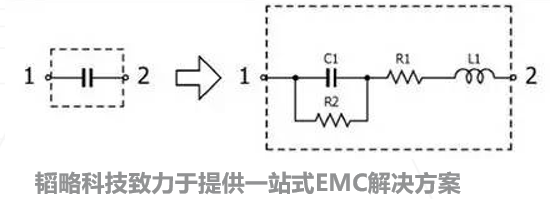

2.电容滤波在何时会失效整改中常常会使用电容这种元器件进行滤波,往往有“大电容滤低频,小电容滤高频”的说法。以常见的表贴式MLCC陶瓷电容为例,进行等效模型如下:

容值10nF,封装0603的X7R陶瓷的模型参数如下:

由于等效模型中既有电容C,也有电感L,组成了二阶系统,就存在不稳定性。对电路回路来说,就是会发生谐振,谐振点在如下频率处:

下图是谐振曲线的示例:

即常说的在谐振点前是电容,谐振点之后就不再是电容了。

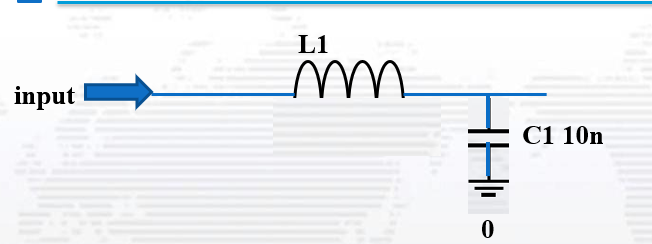

3.LC滤波何时使用如果串联电感L,再并联组成C,就形成了LC滤波:

单独一个电容C是一阶系统,单独一个电感L也是一阶系统,在幅值衰减斜率是-20dB。但LC组成的二阶系统,幅值衰减斜率是-40dB,更靠近理想的“立陡”的截止频率的效果,即滤波效果更好。

4.PWM频率到底是多少往往提到PWM,比如会说用20kHz PWM驱动电机等。

但实际上,这个20kHz仅代表PWM的脉冲周期是50us

对于阶跃信号来说,由于上升时间tr无穷小,则频率f无穷大。当频率高了之后,寄生参数则不能在忽略,会引发很多谐振的问题。从信号上来看,就是很陡峭的阶跃信号会有过冲和振荡的问题。简单来说就是频率f越大,则噪声所占的频率就会越宽泛,即EMC特性就会越差。

5.如何将原理图和PCB对应起来由于细分工种的问题,原理图和PCB被割裂开来,由两组人进行分工作业:

例如在原理图上有如下的电路:

其隐含一个问题就是在PCB上其实V1的负极和C1的负极是有一条线(PCB layout工具软件中用的词比较准确,Trace,踪迹/轨迹)。往往在设计阶段A->B->C是都会关注的。如果EMC出现问题,除了要在原理图上查找电路参数的问题,还需要特别关注C->D,即回流路径。

如果回流路径不顺畅,会造成信号的畸变。

比如在EMC试验时,MCU的ADC采集到的信号被干扰到了,则除了在原理图上分析外,在PCB上讲该信号高亮出来,然后再耐心寻找该信号的回流路径是否有不顺畅的地方:对着信号线头脑中想象回流路径,有点意识流的感觉。

4总结

电磁兼容(EMC):EMC小结之时钟辐射问题

一前言

在电磁兼容的辐射发射测试中,最常见的就是时钟辐射超标(如下图所示)。可以说70%的辐射超标都是时钟问题引起的,因为时域中周期性的信号对应频域中离散的频谱,所以时钟能量比较集中,这在频谱上的表现就是:时钟频点(时钟基频以及倍频)上能量很高,而非时钟频点几乎没有能量。

那么我们如何分析测试数据并且改善辐射呢?

二测试数据分析

分析辐射数据之前,我们先简单了解一下时钟最基本的一个特点:倍频。如下图所示,常见的梯形波在频域上是有很多间隔规律的单支的,比如一个24MHz的摄像头时钟,那么f0=24MHz,在频域上每隔24MHz就会有一个单支能量很高(24MHz,48MHz,72MHz,96MHz,120MHz……)。

所以想要从测试数据上分析时钟源头,就需要计算出每个相邻时钟单支的频率间隔△f,f0=△f。比如上述测试数据中:

f5-f3=875.2470-750.1083≈125MHz

f3-f2=750.1083-625.0780≈125MHz

f2-f1=625.0780-501.1790≈125MHz

从计算结果中可以知道,1号点、2号点、3号点、5号点是125MHz时钟的倍频(4号点833MHz是实验室中手机的噪声,可以忽略)

三辐射超标的原因

分析出了超标的时钟频率,就可以很轻松的通过频谱仪或者原理图和pcb找到时钟来自哪一个芯片的哪个时钟信号。但是这并不代表我们可以很好解决时钟问题,因为时钟辐射的路径多种多样,又可能包含差模、共模辐射。即使找到了辐射路径,也不一定能降低辐射,因为时钟是我们电子产品需要的有用信号,很多滤波手段会影响信号完整性,从而导致功能异常或者降低稳定性和一致性。这就需要我们在电磁兼容和产品性能中取一个平衡,这让很多工程师越来越憔悴。

不过别慌,只要我们沉住气,一步一步分析问题,总有海阔天空、枯木逢春的一天。接下来我们看看时钟辐射超标的几个常见原因:

1. 排线是时钟辐射的良好天线,比如屏排线,摄像头排线,喇叭排线等。很多排线本身没有时钟线,但是会耦合到时钟噪声,所以也需要注意,无论是输入排线(①)还是输出排线(②),都要在接口处做好滤波措施,如有必要,最好再加上磁环。另外,排线的屏蔽接地是非常重要的,一根屏蔽接地良好的排线,可以降低10-30db的辐射。

2. 一般CPU都会有参考时钟,如果参考时钟晶体附近有长走线,那么时钟噪声很容易耦合到长走线,从而辐射出去。所以走线要远离晶体,晶体附近也要做好包地处理。

3. 很多数据线上也会有时钟噪声(④和⑥),一般在数据线源端做好RC滤波,R取值22或者33欧姆(也可以考虑换成磁珠,增强滤波),C取值33pf以内。

4. 时钟走线本身辐射是最强的(⑤和⑦),所以一定要全程包地线处理,走线越短越好,源端滤波最好采用磁珠+电容的方式,磁珠取值60-600欧姆@100MHz,电容取值33pf以内。因为时钟超标一般是100-1000MHz,磁珠用于降低100-500MHz的噪声(500Mhz以上也有较好的滤波效果),电容用于降低500-1000MHz的噪声。

5. PCB上的长走线(⑧)有时候也带有较强的时钟噪声,因为芯片内部电路设计问题,或者pcb走线设计有问题会耦合到时钟噪声。对于长走线,应该用频谱仪探针看看是否有噪声,然后进行滤波。这类走线如果速率很低或者对信号完整性要求很低,就可以加大滤波参数,所以较好解决。

6. 靠近时钟线的走线(⑨)很容易耦合到噪声,所以时钟线未包地的情况下,其他走线要远离时钟等高速信号,降低耦合程度。

7. 因为时钟滤波参数不能太大,所以很多时钟我们即使知道问题出在哪也无能为力。这个时候就可以考虑在晶体(⑩)上加展频IC,可以有效降低辐射。下图是增加展频前后的测试数据。

四结语

时钟辐射问题可以通过分析测试数据找到时钟源头,但是有时候未必能有效解决问题,因为超标的原因很多,我们不能一直盯着时钟走线疯狂滤波。这个时候就需要我们耐心分析,剥丝抽茧,拨开云雾见天明。