1. 中断系统

为什么需要中断?

输入,输出。

计算机程序调试;发生异常事件;

都需要由中断系统进行处理.

1.1 中断的原因

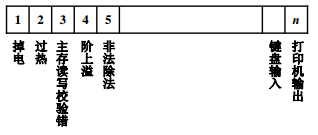

引发中断的各种因素包括:

人为设置中断, 转管指令;

程序性事故, 溢出、操作码不能识别、除法非法

硬件故障,

I/O设备,

外部事件, 用 键盘中断 现行程序;

1.2 中断系统需解决的问题

(1) 各中断源 如何 向 CPU 提出请求 ?

(2) 各中断源 同时 提出 请求 怎么办 ?

(3) CPU 什么 条件、什么 时间、 以什么 方式

响应中断 ?

(4) 如何 保护现场 ?

(5) 如何 寻找入口地址 ?

(6) 如何 恢复现场,如何 返回 ?

(7) 处理中断的过程中又 出现新的中断 怎么办 ?

硬件 + 软件

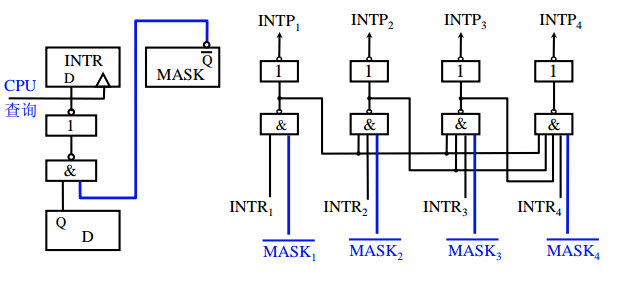

2.中断请求标记和 中断判优逻辑

中断系统任意瞬间只能响应一个中断源的请求。

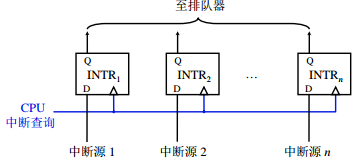

2.1 中断请求标记 INTR

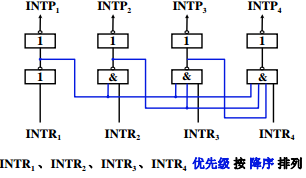

一个请求源, 一个 INTR 中断请求标记触发器;

多个INTR, 组成 中断请求标记寄存器;

INTR, 分散 在各个中断源的 接口电路中,

INTR, 集中 在 CPU 的中断系统 内;

2.2中断判优逻辑

如果有多个中断请求怎么办?

响应哪一个?

硬件实现(排队器)

- 分散 在各个中断源的 接口电路中 链式排队器

- 集中 在 CPU 内;

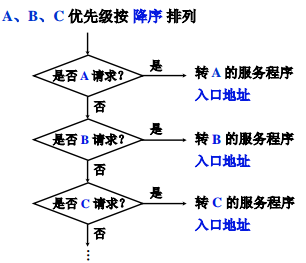

2.3软件实现(程序查询)

3. 中断服务程序的入口地址

3.1 硬件向量法

如何找到中断服务程序的入口地址?

知道了要响应的中断源,才能确定要执行那个中断服务程序.

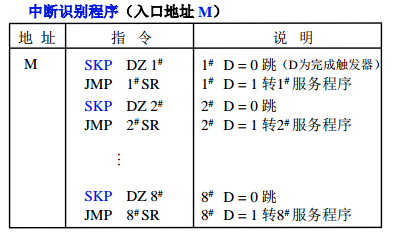

3.2 软件查询法

八个中断源 1, 2, … 8 按 降序 排列

用软件如何实现寻找中断服务程序的入口地址呢?

4. 中断响应

CPU在什么时间、什么条件下响应中断?

CPU在任何条件下都要立即响应中断吗?

CPU在任何时间都能响应中断吗?

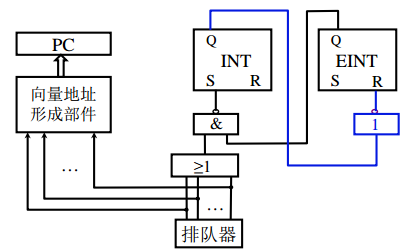

4.1 响应中断的 条件

允许中断触发器 EINT = 1

4.2 响应中断的 时间

指令执行周期结束时刻由CPU 发查询信号;

4.3 中断隐指令

所谓中断隐指令,指的是计算机指令集中并没有设计该指令,实际的实现过程是由硬件实现的,

在执行某些指令时,这些隐指令由硬件自动实现。

如果需要响应某个中断请求, CPU如何响应中断请求?

- 响应中断,要去执行中断服务程序;

- 为将来的中断返回做准备

(1)保护程序断点

(2)保护程序运行的软硬件状态;

单重中断:执行中断, 服务程序时不允许再发生中断.

多重中断:保护程序,软硬件状态的过程中,不允许发生中断;

-

保护程序断点

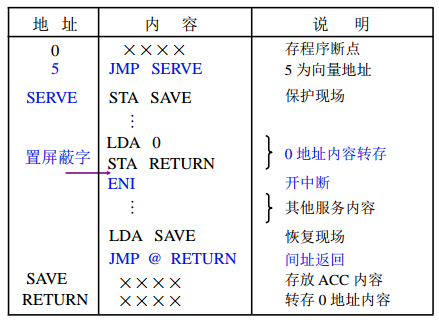

断点存于 特定地址( 0 号地址) 内, 断点 进栈; -

寻找服务程序入口地址

向量地址 —> PC (硬件向量法)

中断识别程序, 入口地址 M—> PC (软件查询法)

- 硬件 关中断

INT 中断标记;

EINT 允许中断;

R – S 触发器;

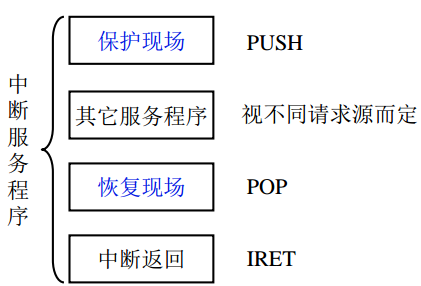

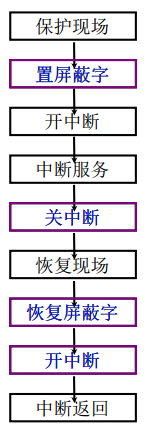

5. 保护现场和恢复现场

5.1 保护现场

断点: 中断隐指令 完成;

寄存器 内容: 中断服务程序 完成;

5.2 恢复现场

中断服务程序 完成;

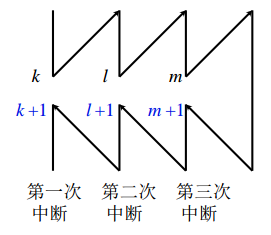

6. 多重中断

6.1 多重中断的概念

如果在执行中断服务程序的过程中,出现了更重要

的,需要及时处理的新事件,怎么办呢?

程序断点 k+1 , l+1 , m+1;

6.2 实现多重中断的条件

要允许CPU在执行某个中断服务程序时,响应新的中断请求

是不是任何一个新的中断请求,均能中断正在进行的中断服务?

-

提前 设置 开中断 指令;

-

优先级别高的中断源, 有权中断优先级别低 的中断源;

6.3 屏蔽技术

6.3.1 屏蔽触发器的作用

MASK = 0(未屏蔽), MASKi = 1 (屏蔽)

INTR 能被置 “1”, INTPi = 0 (不能被排队选中)

6.3.2 屏蔽字

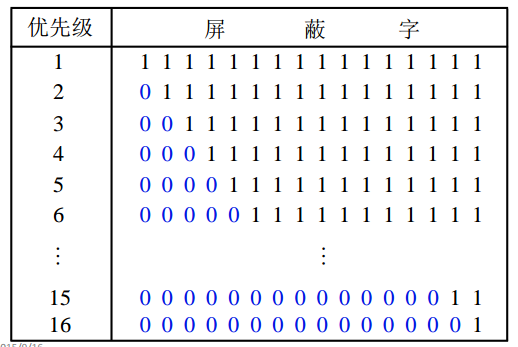

16个中断源 1, 2, 3 , … 16 按 降序 排列

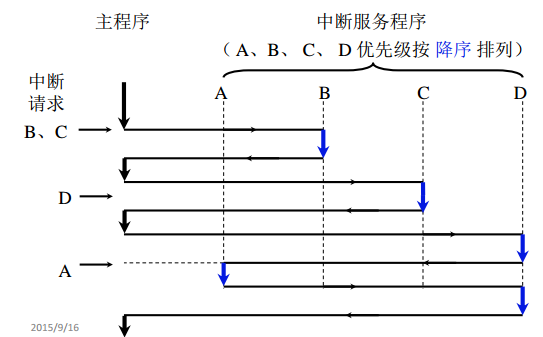

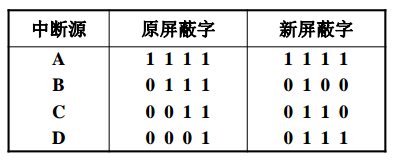

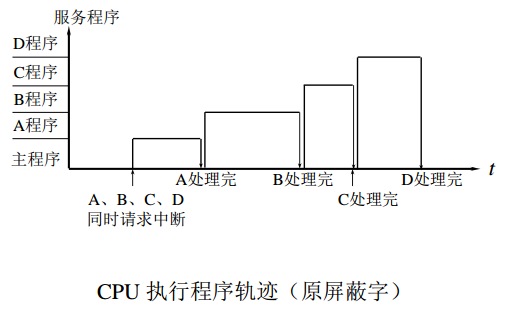

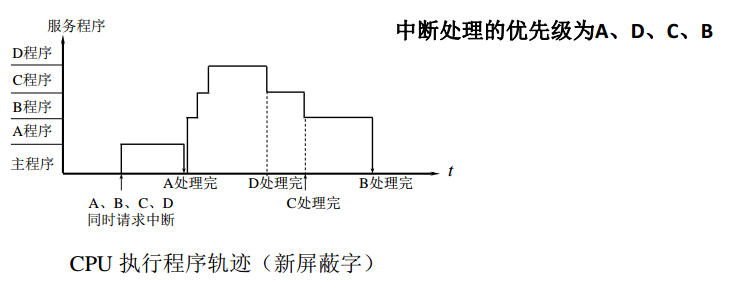

6.3.3 屏蔽技术可改变处理优先等级

响应优先级 不可改变

处理优先级 可改变(通过重新设置屏蔽字)

响应优先级 A→B→C→D 降序排列

处理优先级 A→D→C→B 降序排列

6.3.4 屏蔽技术的其他作用

可以 人为地屏蔽 某个中断源的请求;

6.3.5 新屏蔽字的设置

6.4 多重中断的断点保护

6.4.1 断点进栈

中断隐指令 完成

6.4.2 断点存入“ 0 ” 地址

“ 0 ” 地址表示,并非是真正的物理地址0;

可以是给定的物理地址,

中断隐指令 完成;

中断周期:

0 --> MAR

命令存储器写

PC —> MDR, 断点 —> MDR

(MDR) —> 存入存储器;

三次中断,三个断点都存入 “ 0 ” 地址

如何保证断点不丢失?

中断隐指令 完成;

pc:保存了下一条指令,要执行的地址;

6.4.3 断点保护

程序断点存入 “ 0 ” 地址的断点保护